提升LED驅動芯片視覺刷新率的邏輯電路設計

黎官華,王衛東

(桂林電子科技大學信息與通信學院,廣西桂林541004)

?

提升LED驅動芯片視覺刷新率的邏輯電路設計

黎官華,王衛東*

(桂林電子科技大學信息與通信學院,廣西桂林541004)

摘要:為了提升LED顯示屏的畫面質量,設計了能提高LED顯示屏視覺刷新率的邏輯電路。該電路將一個顯示周期分為32段,每一段包含有128個灰度時鐘周期,占空比由12位灰度數據控制。邏輯電路產生的PWM和傳統的PWM相比能提高視覺刷新率,最高能將視覺刷新率提高至32倍;能彌補S-PWM(Scrambled-PWM)在灰度數據低時視覺刷新率低的不足。在Cadence軟件下進行設計仿真,并在開發板上進行了驗證設計的可行性。

關鍵詞:LED顯示屏;邏輯電路; PWM;刷新率

LED顯示屏具有節能、環保、色彩鮮艷等優勢被廣泛使用于公共媒體、戶外廣告、亮化工程等領域中[1]。灰度等級和視覺刷新率是衡量LED顯示屏顯示效果的兩個重要的指標,刷新率越高,人眼越不能感覺到畫面的閃爍;灰度等級越高,顯示畫面就更加細膩,同時色彩會更加豐富,但是高的灰度等級和刷新率是相互矛盾的指標[2]。在相同的灰階時鐘下,灰度等級越高,會產生刷新率過低的問題[3]。降低灰度等級或提高灰階時鐘頻率可以提高視覺刷新率,但是降低灰度等級會嚴重影響畫面的細膩和色彩,而提高灰階時鐘頻率容易產生電磁干擾。

1 傳統的PWM和S-PWM

傳統的PWM用灰度數據和灰階計數器的計數值相比較,計數器的計數值小于或是等于灰階數據值時,LED點亮;計數器的計數值大于灰階數據值后,LED關閉。對于任何級別亮度點亮脈沖的起始位置在同一個時間點上,如果所有LED同時被點亮會產生一個很大的電流尖峰,會產生嚴重的電磁干擾[4]。同時,在一個刷新周期內,LED點亮和關閉只有一次,只出現一個連續的時間可變點亮脈沖,刷新率會很低,可能給人眼帶來閃爍感。S-PWM是將一個計數周期打散為若干個較短的計數周期,打散的計數周期之和等于打散前的計數周期,占空比也相等,這樣就增加了整體的刷新率[5-6]。S-PWM將一個PWM周期分為最重要為(MSB)和最不重要位(LSB),MSB計數周期打散后重復更新多次,再加上一次LSB計數周期,使打散的計數周期之和等于打散前的計數周期,占空比也相等。但是這種調制也存在一個重要的問題,當MSB的數據全為0,LSB數據不為0時,S-PWM和傳統的PWM產生的灰度控制信號幾乎一樣[7]。這種情況下刷新率并沒有得到提升。

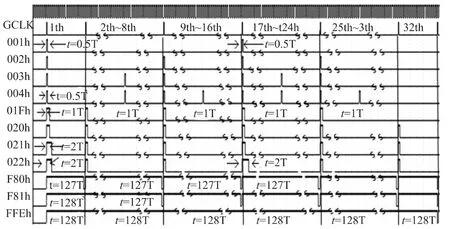

2 改進的PWM工作原理

針對傳統的PWM和S-PWM存在的不足,本文提出了一種改進型的PWM。改進型的PWM的工作原理是:以4 096個灰度時鐘周期(GCLK)為一個LED顯示周期,將一個顯示周期分為32段,也就是將一個完整的PWM劃分為32段pwm,每一段含有128個灰度時鐘,每一段占空比由12位灰度數據控制,整個PWM的高電平時間隨著灰階數值的加1而增加一個GCLK,整個PWM高電平包含的GCLK個數等于灰階數據的十進制值。計數器的計數值的高5位和灰階數據的低5位(LSB)共同進行段選,計數器值的低7位和灰階數據的高7位(MSB)相比較決定每一段的pwm高電平時間。灰階數據小于010h時,選中的段數為輸入灰階數值對應的十進制值的兩倍,每段pwm高電平時間為0.5個GCLK。選中段的順序為:1、17>9、25>5、21>13、29>3、19>11、27>7、23>15、31>2、18>10、26>6、22>14、30>4、20>12、28>8、24。灰階數據大于或等于010h時,選中的段數等于與輸入灰階數值對應的十進制值,選中的段pwm的高電平時間包含的GCLK個數等于MSB對應的十進制數值加1,未選中的段pwm的高電平時間包含的GCLK個數等于MSB對應的十進制數值。選中的段順序為:1>17>9>25>5>21>13>29>3>19>11>27>7>23>15>31>2>18>10>26>6>22>14>30>4>20>12>28>8>24>16>32。例如灰階數據為二進制000000100001時,MSB為0000001,那么段的pwm高電平時間為2個GCLK,LSB位為00001表示第1段被選中,選中的第1段pwm高電平時間為2個GCLK,剩余的31段為1個GCLK。隨著灰階數據加1,MSB不變,但是低LSB加1,則選中的段數加1,此時第1、17段pwm高電平時間為2個GCLK,剩余的30段為1個GCLK。灰階數據為FFFh時,MSB為1111111,那么段的pwm高電平時間為128個GCLK,LSB位為11111表示中的1到31段被選中,選中的1到31的pwm高電平時間128 個GCLK,剩余的第32段為127個GCLK。部分波形如圖1所示。

圖1 PWM部分波形

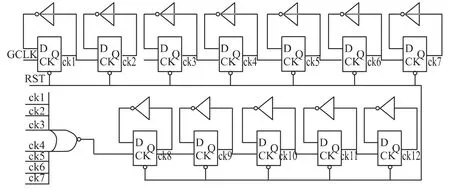

圖2 計數器電路

3 邏輯電路實現圖

3.1計數器

12bit的計數器如圖2所示,計數器由12個D觸發器構成。其中GCLK為計數時鐘,RST為復位信號。當RST為低電平時,各個觸發器的輸出端Q 為1,ck1~ck12全為1。當RST為高電平時,低7位計數器開始進行減1計數。當ck1~ck7位全為0時,計數了128個GCLK,經過或非門,產生一個脈沖,高5位開始計數。在高5位中,ck8~ck12全為1時表示第一個128個GCLK計數5段,隨著計數的不斷進行,ck8~ck12為0時表示第32計數段。在一個刷新周期內,包含32×128個GCLK,實現了12bit的計數器。

3.2PWMH及PWML電路

PWMH及PWML電路包括有比較器、加法器,CP、CI模塊電路及輔助選通邏輯判斷電路。比較器由14個全加器構成。灰階數據和計數器的計數值相比較,計數器的計數值小于或是等于灰階數據值時,LED點亮;計數器的計數值大于灰階數據值后,LED關閉。在上述原理分析中可知,MSB位全為灰0時,而且灰階數據不小于010h時,選中段導通時間為1個GCLK,未選中的段為0個GCLK。因此在整個比較器進行兩路數據比較,一路是原始的MSB,產生PWML;另一路是MSB加1后的灰階數據,經過邏輯判斷電路進行選擇后產生PWMH。但是灰階數據為0的時,LED在整個周期不亮的,如圖1所示,所以用LSB位進行段選時只有31個狀態。但是每當在MSB不為0,LSB全為0的時,所有的段都被選中,第32段才被選中,因此可以利用這個條件產生一個第32段才選中的控制信號。

在圖1中,灰階數據為020h,二進制位000000100001時,32段全部被選中,每段的高電平時間還是1個GCLK。若在圖3的加法器模塊還是加1,那么加1后的MSB位數據將變為0000010,再送入比較器中,那么此時的pwm的高電平時間為2個 GCLK,和實際相違背。同理,每當LSB位全為0,但是MSB位不全為0時都會出現中這種情況。為了解決這個問題,可以對灰階數據進行一個預先判斷,判斷電路如圖3的CP、CI模塊。當遇到LSB位全為0,但是MSB位不全為0時,CI為0,那么加法器進行加0,再送入比較器進行比較。LSB不全為0時,CI為1,加法器進行加1。例如灰階數據位為二進制000000100001,即圖1中的021h時,由于LSB不為0,那么加法器加1,輸出為0000010,PM1高電平時間為2個GCLK,PWML的高電平時間為1個GCLK,低5位為00001表示第一段選中,因此有第一段的高電平時間為2個GCLK,其余的31段沒被選中,各段高電平時間為1個GCLK。加法器模塊是由7個半加器構成,輸入信號為G5~G11及CI,輸出為g5~g11,F。由于在灰階數據小于010h時,每段的高電平時間為0.5個灰階周期。因此利用比較器的比較結果PM1和灰階時鐘GCLK相與,即可得到一個高電平時間為0.5 個GCLK的脈寬調制波PM2。灰階數據G5~G11經過一個8輸出或門產生一個判斷信號C,灰階數據小于010h時,C為1,否則為0。C可以作為PM1和PM2的選通信號,C為1,PM3等于PM2,否則PM3等于PM1。在MSB全為1時,對應的十進制數為127,加1后變為十進制數128,MSB各位為0,進位標志F 為1。F和PM3經過或門,或門的輸出為PWMH,F 為0,PWMH為PM3,F位1,PWMH在整個長為128 個GCLK段中保持高電平。

圖3 PWMH及PWML電路

3.3譯碼電路

灰度數據的LSB和計數器的高5位ck8~ck12共同進行段選。從上述段選的順序可知,隨著LSB的增加,選中的段數會加1,LSB所對應的十進制數值是多少,就會有多少段被選中,溫度計譯碼也是輸入的二進制信號所對應的十進制是多少就會有多少個“1”輸出。因此對LSB譯碼時采用溫度計譯碼。為了降低電路的復雜性,5位溫度計譯碼由2位溫度計譯碼和3位溫度計譯碼共同構成。其中2位溫度計譯碼的輸出作為列信號,3位溫度計譯碼的輸出作為行信號,再結合電源和地,就構成了4行8列的陣列,32個輸出;每個輸出端的狀態是由行、列的狀態和行列選擇邏輯電路決定[8]。N位溫度計譯碼有2N-1個“1”輸出,但是第32段是在LSB全為0,MSB不為0的時候才被選中。因此可以通過圖3中的CP、CI產生模塊中產生一個判斷信號CP,譯碼器的第32個輸出端CP相或,則5位溫度計譯碼可以輸出32個“1”。灰階數據小于010h時,選中的段數為輸入灰階數值對應的十進制值的兩倍,灰階數據大于010h時選中的段數為輸入灰階數值對應的十進制值,二進制左移一位,相當于乘以2。因此可以設置一個位移電路,在圖3中,C為1時,灰階數值進行左移一位。段譯碼器電路的輸入信號為計數器的計數值高5位,譯碼32個輸出,每一個輸出表示一個包含128個GCLK計數段。

圖4 譯碼電路

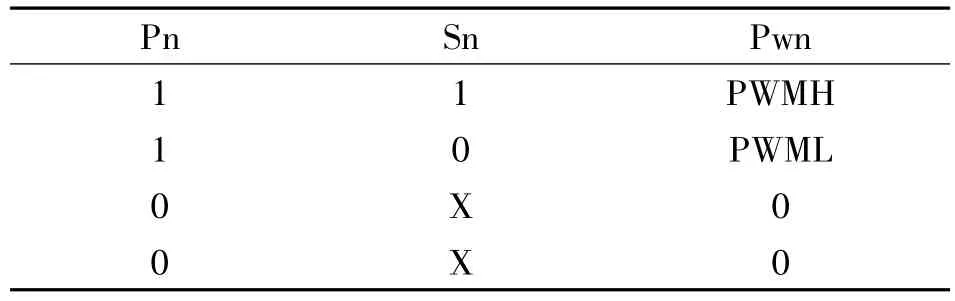

3.4選擇邏輯電路

比較器產生了兩個不同的結果,一個是PWML,另一個是PWMH。每一段pwm是PWML還是PWMH,由溫度計譯碼決定,溫度計譯碼輸出為“1”,則段的輸出為PWMH,否則為PWML。但是第幾段pwm輸出由段譯碼器決定,段譯碼器的P1端輸出為“1”則表示第一段輸出。溫度計譯碼的結果和段譯碼的結果共同決定第圖5中pw狀態。他們邏輯關系如表1所示,pwn經過圖5的PWM合成模塊,得到一個完整的PWM。

圖5 選擇邏輯電路

表1 Pn、Sn與Pwn的邏輯關系表

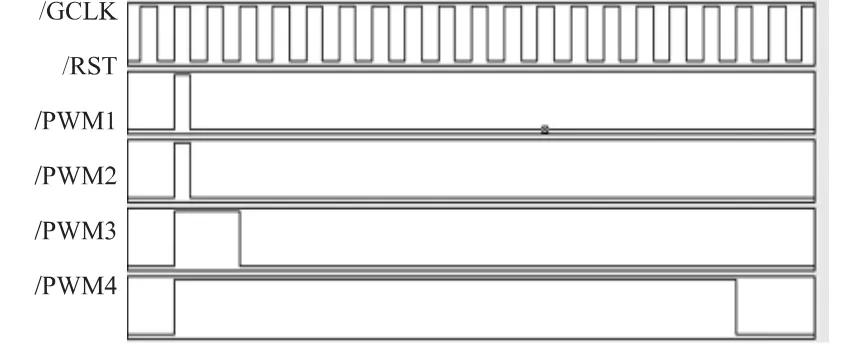

5 仿真驗證結果及分析

采用Cadence ADE仿真平臺中的Spectre Verilog數模混合仿真器對電路進行仿真。PWM1、PWM2、PWM3、PWM4分別為輸入灰階數據003h、007h、023h及103h時PWM輸出波形。003h和007h都小于010h,選中的段數是其對應的二進制輸出數值的兩倍,因此PWM1、PWM2分別有6個和14個高電平脈沖,可見在灰階數據低的時候,刷新率也有了提高。023h及103h都大于010h,MSB和LSB位不全為0,選中的段數是其對應的二進制輸出數值。因此,選中的段數分3,即有3段輸出的是兩路比較器輸出PWMH,剩下29段輸出的是PWML,在一個完整的PWM內有32個高電平脈沖,刷新率是傳統的PWM的32倍。

圖6 PWM的仿真結果圖

圖7是第17段的pwm高電平包含的GCLK個數。003h、007h、023h及103h時,17th都被選中。003h和007h都小于010h,其pwm只包含0.5個GCLK,PWM1和PWM2的總的高電平時間分別為3個、7個GCLK。023h的MSB為0000001,那么比較器輸出中PWMH包含2個GCLK,PWM包含1個GCLK,所以PWM1的高電平包含有(3×2+29×1)個GCLK,和023h對應的十進制值35相符合。

圖7 第17顯示段pwm仿真圖

為了進一步驗證電路的可靠性,在QuartsⅡ軟件中建立上述原理圖,并下載到FPGA中,用撥碼開關模擬灰階數據輸入,通過示波器觀看PWM的輸出波形。當模擬的輸入值為103h時,PWM的輸出波形如圖8所示,波形和圖7中的PWM4相符合。

圖8 灰階數據為103 h時PWM圖

6 總結

本文分析了傳統的PWM和S-PWM的不足,設計了一種實現改進型的PWM的電路。電路包含了計數器、比較器、譯碼器等模塊,將一個完整的PWM顯示周期劃分為32個顯示段,不同的灰階數據每個顯示段包含的GCLK不同。劃分前的PWM和劃分后的PWM占空比相一致。改進型的PWM即使在灰階數據很低時視覺刷新率也有了很大提高,提升了LED顯示屏的畫面質量。

參考文獻:

[1]陳龍,魯寶春,莊明照,等.全彩LED顯示屏灰度改進研究[J].遼寧工業大學學報,2011,31(1) :9-12.

[2]宗慶國,袁勝春,何國經.LED顯示屏高灰階高刷新技術探討[J].現代顯示,2012,140:335-339.

[3]鄧宏貴,梅衛平,曹文輝,等.基于PWM的LED顯示屏像素亮度控制方法[J].光電子技術,2010,30(2) :131-134.

[4]宋超,王瑞光,馮英翹.LED顯示屏驅動電流的潛在電磁干擾分析[J].光電子·激光,2013,24(6) :1059-1064.

[5]蘇信華.可提高影像刷新率及電磁干擾的高灰度LED驅動芯片[J].現代顯示,2007(10) :66-68.

[6]邱天奇.基于SPWM功能的LED恒流驅動芯片[D].西安:西安電子科技大學,2011:27-28.

[7]王巍,黃展,安友偉,等.全彩LED驅動芯片的S-PWM優化[J].電視技術,2012,36(21) :74-76.

[8]劉衛平.8位高速電流舵型DAC電路研究與設計[D].電子科技大學,2006:36-38.

[9]Svilainis L.LED Brightness Control for Video Display Application [J].Displays,2008,29(5) :506-511.

黎官華(1987-),男,漢族,廣西玉林人,桂林電子科技大學集成電路工程碩士研究生,研究方向為數模混合集成電路設計,69571294@ qq.com;

王衛東(1956-),男,漢族,桂林電子科技大學碩士生導師,教授,中國通信學會高級會員,研究方向為模擬集成電路與電流模式電路。

Design of High Refresh Rate and High Precision LED Constant Current Drive Circuit

LI Guanhua,WANG Weidong*

(School of Information and Communication Engineering,Guilin University of Electronic Technology,Guilin Guangxi 541004,China)

Abstract:In order to improve the quality of image of LED display,a high refresh rate and high stability LED constant current drive circuit was designed.A complete PWM is divided into 32 sections.A novel counter is designed by modified the M-serial to produce irregular PWM,improves visual refresh rate.At the same time,improve the band gap reference source and using high output impedance current mirror to improve the stability of current.

Key words:high refresh; high stability; band gap reference source; current mirror

中圖分類號:TN432

文獻標識碼:A

文章編號:1005-9490(2015) 03-0526-05

收稿日期:2014-06-30修改日期:2014-08-12

doi:EEACC:4240D; 121010.3969/j.issn.1005-9490.2015.03.012