基于FPGA的巴克碼相關器設計與研究

張 鑫,孫海青

(中國船舶重工集團公司第七二四研究所,南京211153)

基于FPGA的巴克碼相關器設計與研究

張鑫,孫海青

(中國船舶重工集團公司第七二四研究所,南京211153)

摘要:分析巴克碼的設計及其相關的特點與原理,用Verilog語言編寫相關器,利用FPGA實現13位巴克碼相關器,并對其用Modelsim仿真。仿真證明輸出了最大功率主副比,有效抑制了旁瓣,并為雷達工程中巴克碼的應用提供更堅實的理論基礎。

關鍵詞:雷達;信號處理;FPGA;巴克碼;相關器;旁瓣抑制

0引言

雷達系統最基本的任務是完成對目標的檢測,從而實現對目標的跟蹤和定位。然而,由于雷達微弱目標回波信號總是處在各種各樣的噪聲環境中,其直接影響系統對目標回波的處理質量,如降低對目標的檢測能力,降低目標的跟蹤定位精度。相關器根據信號和噪聲相關函數的差異進行檢波,周期信號的自相關函數仍然是周期的,且隨時間衰減得很慢。而噪聲由于其隨機性,在相關器中隨時間衰減的很快,因此相關器可以從信號和噪聲的混合波形中檢測出目標信號[1]。巴克碼由于具有尖銳的自相關函數,從而可以將淹沒在噪聲下的基于巴克碼波形的微弱目標信號有效相關出來,實現對信號與噪聲的分離,因此常用于雷達信號波形設計中。

Verilog HDL是一種全方位的硬件描述語言,包括系統行為級、寄存器傳輸級、邏輯門級等多個設計層次,支持結構、數據流和行為3種描述形式的混合描述[2-3]。將巴克碼相關器采用Verilog語言在FPGA中實現,可以借助FPGA的并行性實現信號相關檢測的高速實時特性。

1巴克碼相關器原理

1.1 m序列

m序列是最長線性移位寄存器序列的簡稱[4]。它具有優良的自相關函數,易于產生和復制,在擴頻通信中得到了廣泛的應用。m序列也是研究和構造其他序列的基礎。

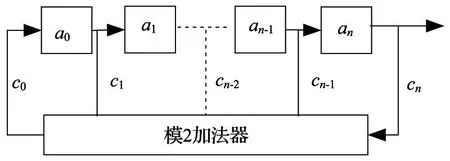

m序列是由線性反饋移位寄存器產生,如圖1所示。圖中a0,a1,…,an-1表示移位寄存器的狀態,c0,c1,…,cn-1為對應級移位寄存器的反饋系數,ci=0表示該反饋斷開,ci=1表示該反饋存在。

圖1 m序列產生原理圖

對于反饋移位寄存器產生的序列,取決于反饋系數,其反饋邏輯表示為

F(x)=c0+c1x+c1x2+…+cnxn

(1)

式(1)稱為m序列的特征多項式。特征多項式一旦確定,那么其產生的偽隨機序列也就確定了。經嚴格的證明:若反饋移位寄存器的特征多項式為本原多項式,則移位寄存器就能產生m序列,且其周期為N=2n-1,n為寄存器的個數。

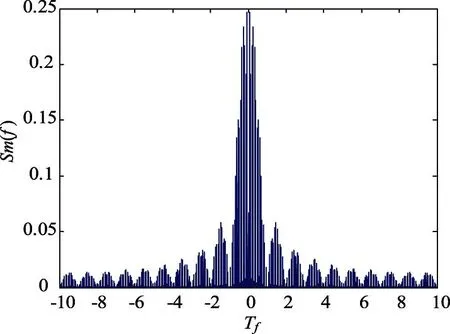

在m序列長度為15位時,m序列的功率譜見圖1。從圖中可以看出m序列的功率譜特點:(1)由于自相關函數的周期性,其功率譜是一個線狀譜;(2)譜線包絡由m序列碼元寬度Tc決定與周期序列無關。

圖2 15位m序列的功率譜

m序列功率譜寬度理論值為無窮大,但主要能量集中在第1個零值點之內,其約占總能量的90%。所以,實際上,也經常把f=0~1/Tc這段頻率范圍稱為偽碼序列的頻帶寬度,記作△f。

(2)

m序列具有如下性質:

(1) 平衡性:m序列的一個周期中,“1”的個數與“0”的個數基本相等,確切地說,“1”的個數比“0”的個數多1個。

(2) 游程分布:每個周期內,總共有2n-1個游程,其中長度等于k,1≤k≤n-2的游程占游程總數的1/2。“0”和“1”的游程數目各占一半,長度為n-1的游程只有1個為全“0”游程,長度為n的游程也只有1個為全“l”游程。

(3) 移位可加性:1個m序列同該序列的任意移位(循環移位)序列相加(模2加),仍是m序列。

1.2 barker序列

barker序列也稱為巴克碼,也是一種偽隨機二維序列,其非周期自相關函數很類似白噪聲的自相關函數。二元偽隨機序列的非周期自相關函數如下:

(3)

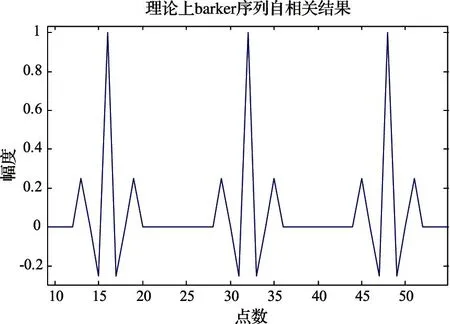

這個二元偽隨機序列就稱為巴克序列。這種序列的非周期自相關函數只有4種可能值,最大值為P,最小值為±1或0。但是,巴克碼有一個很重要的缺點,就是巴克序列很短,目前只找到9種巴克序列,最長為P=13。13位巴克序列的自相關函數具有類似白噪聲自相關函數的特性,如圖3所示。

圖3 barker碼自相關函數圖

根據巴克碼的頻譜和自相關特性,巴克碼也是一種性能比較優良的偽隨機碼。但是,巴克碼的本身長度太短,在實際運用中受到了很大的限制。人們找了一種增加巴克碼長度的方法,稱為組合巴克碼。

組合巴克碼就是用一個巴克碼作為碼元(內碼)組成另一個新的巴克碼(外碼)。這個新的巴克碼就是組合巴克碼。例如,以4為巴克碼{+ + - +}作為基本碼元,做成一個新的4位巴克碼:

其中-Bi(4)為Bi(4)的反碼,即-Bi(4)={-,-,+,-}。所以,新的16位巴克碼為

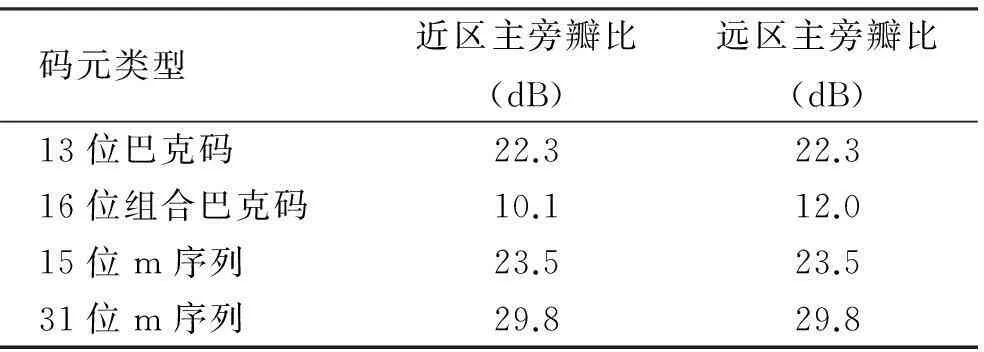

新的16位巴克碼自相關函數如圖4所示。可以看出,組合巴克碼的旁瓣特性既不完全同于內碼旁瓣特性,也不完全同于外碼特性。組合巴克碼主峰附近的最大電平是由外碼的碼長決定,而遠離主峰旁瓣變化規律與內碼的自相關函數特性相同。根據計算可以得16位組合巴克碼自相關函數主峰近區和遠區的最大主旁瓣比電平和15位m序列自相關函數主峰近區和遠區的最大主旁瓣比電平。

圖4 組合巴克碼自相關函數

由巴克碼的自相關函數圖可以看出,組合巴克碼的旁瓣性質沒有m序列的旁瓣性質好。近、遠區的主旁瓣比如表1所示。由表可以看出,雖然同等位數的巴克碼主旁瓣比與m序列相近,但組合16位巴克碼的近遠旁瓣比都小于m序列。這對于偽隨機序列的自相關性能會帶來很大的影響,降低了其抗干擾性能是重要的影響之一。數字信號處理方案是在頻域進行的,但組合巴克碼的長度能很方便取到2N位。這樣能很方便地通過對雷達的信號與噪聲進行FFT變換(先補零)后得到其頻譜函數,與傳輸函數相乘后即為頻率響應,再經IFFT變換,求匹配濾波器傳輸函數來實現輸出時域波形。如果需要進一步提高主旁瓣信噪比,則需要對每一碼元再進行編碼,通過增加延遲加權周期,可進一步降低旁瓣電平。這部分的取舍取決于系統的要求。

表1 巴克碼和m序列近遠區主旁瓣比

2Verilog實現仿真與結論

2.1 Barker碼的相關器的Verilog實現

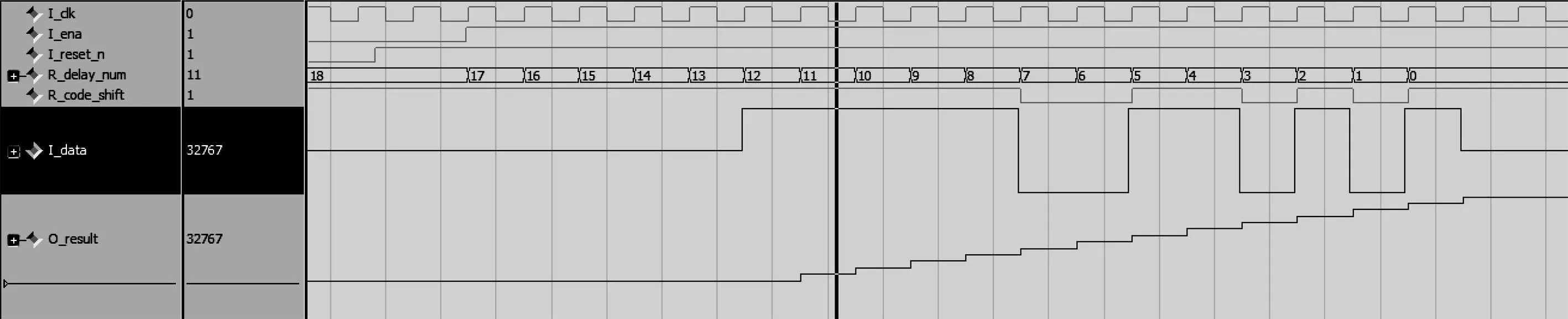

通過以上Barker碼的理論研究后便開始13位Barker碼的設計實踐。在創建了barker13_acu2模塊后,設計了時鐘I_clk,16位數據輸入端I_data,以及延遲8位的延時的周期數信號I_delay_num,最后輸出20位結果O_result。而Barker碼相關器測試向量Testbench的設計,采用了在對相關器初始化并復位后直接輸入預先生成的16位定點模擬回波的方法,即直接在每個延遲200ns的時間點上給予I_data確定的定點值,以此來判斷輸出信號O_result是否符合Barker碼的自相關性。

2.2 仿真結果與結論

根據相關器的實現框圖,方案為使用負數為取反加一的方法實現與-1的乘法,可以得到13位Verilog語言實現。在整個架構完成后進行了測試向量Testbench 設計。對相關器初始化復位后,輸入預先生成的16位定點模擬回波,并得到了Modelsim功能仿真結果。見圖5。

在圖5中,R_code_shift 代表本地的13位barker碼,I_data代表輸入的13位barker碼,O_result代表輸入信號與本地碼相關后的輸出,R_delay_num代表著距離門數。當其值遞減到12時,輸入信號的barker碼與本地的barker碼開始積累,積累13個時鐘周期后輸出達到最大幅值,實現了Barker碼的相關器。將Modelsim功能仿真結果導出,送回matlab進行對比,近遠區主旁瓣比均接近于22.3dB,可以看出兩仿真結果一致,實現了13位barker相關。

3結束語

基于FPGA的巴克碼相關器很好地實現了巴克碼脈沖回波信號的相關,有效地實現了噪聲環境下微弱目標回波信號的提取,仿真結果也與實際使用情況是相吻合的。后續再通過組合巴克碼加權實現高主副比以及長碼下多普勒處理等工程方法的解決,可以使巴克碼波形在雷達中得到更廣泛的應用。

圖5Modelsim功能仿真結果

參考文獻:

[1]王心水.基于fpga的巴克碼發生器與識別器的設計[J].電子技術,2010(2).

[2]龍光利.巴克碼識別器的設計與FPGA的實現[J].科技廣場,2006(4).

[3]張增良,焦智,周濤.基于CPLD的巴克碼信號發生器與譯碼器[J].華北航天工業學院學報,2005(03).

[4]Jackson W,edBarker R H.Communication Theory[M].New York: Academic Press Inc,1953:273-287.

[5]Cohen M N.現代雷達原理[M].卓榮邦,楊士毅,等譯.北京:電子工業出版社,1991:480-517.

Design of a Barker code correlator based on FPGA

ZHANG Xin, SUN Hai-qing

(No.724 Research Institute of CSIC, Nanjing 211153)

Abstract:The Barker code and its characteristics and principle are analyzed. The 13-bit Barker code correlator is designed with Verilog language based on the FPGA, and then simulated via the Modelsim. The simulation results indicate that the maximum master-to-slave power ratio is output and the sidelobe is suppressed effectively, providing a solider theoretical foundation for the application of Barker code in radar engineering.

Keywords:radar; signal processing; FPGA; Barker code; correlator; sidelobe suppression

中圖分類號:TN911.7

文獻標志碼:A

文章編號:1009-0401(2015)04-0039-04

作者簡介:張鑫(1981-),男,工程師,研究方向:雷達總體技術;孫海青(1983-),男,工程師,研究方向:雷達信號處理。

收稿日期:2015-04-28;修回日期:2015-07-20