基于FPGA的Serial RapidIO協(xié)議 的設(shè)計與實現(xiàn)

許樹軍,黃 镠,牛戴楠,王 銳

(中國船舶重工集團公司第七二四研究所,南京 211153)

基于FPGA的Serial RapidIO協(xié)議 的設(shè)計與實現(xiàn)

許樹軍,黃镠,牛戴楠,王銳

(中國船舶重工集團公司第七二四研究所,南京 211153)

摘要:在對RapidIO協(xié)議和Serial RapidIO(SRIO,下同) IPcore用戶接口介紹的基礎(chǔ)上,詳細(xì)描述了Serial RapidIO交換架構(gòu)在FPGA上的編程方法,并采用雙緩存機制實現(xiàn)了位寬、數(shù)據(jù)流速的轉(zhuǎn)換,完成了多SRIO節(jié)點間的高速數(shù)據(jù)通信,具有較強的通用性和可移植性。

關(guān)鍵詞:FPGA;SRIO IPcore;RapidIO;高速通信;串行接口

0引言

RapidIO高速總線技術(shù)主要為了實現(xiàn)系統(tǒng)內(nèi)部設(shè)備互連,總線支持芯片到芯片和板到板通信。其規(guī)范采用三層分級體系結(jié)構(gòu):邏輯層、傳輸層和物理層。在物理連接上,它支持兩種方式:并行模式和串行模式。與并行模式相比,串行模式具有更少的連接管腳、更大的帶寬、更高的擴展性能、更低的成本等優(yōu)點。

本文采用Xilinx公司Virtex6系列的FPGA實現(xiàn)高速串行RapidIO(SRIO)接口,即利用FPGA內(nèi)RocketIO模塊實現(xiàn)3.125Gbps ×4的SRIO高速接口。

1用戶接口介紹

1.1 RapidIO協(xié)議概述

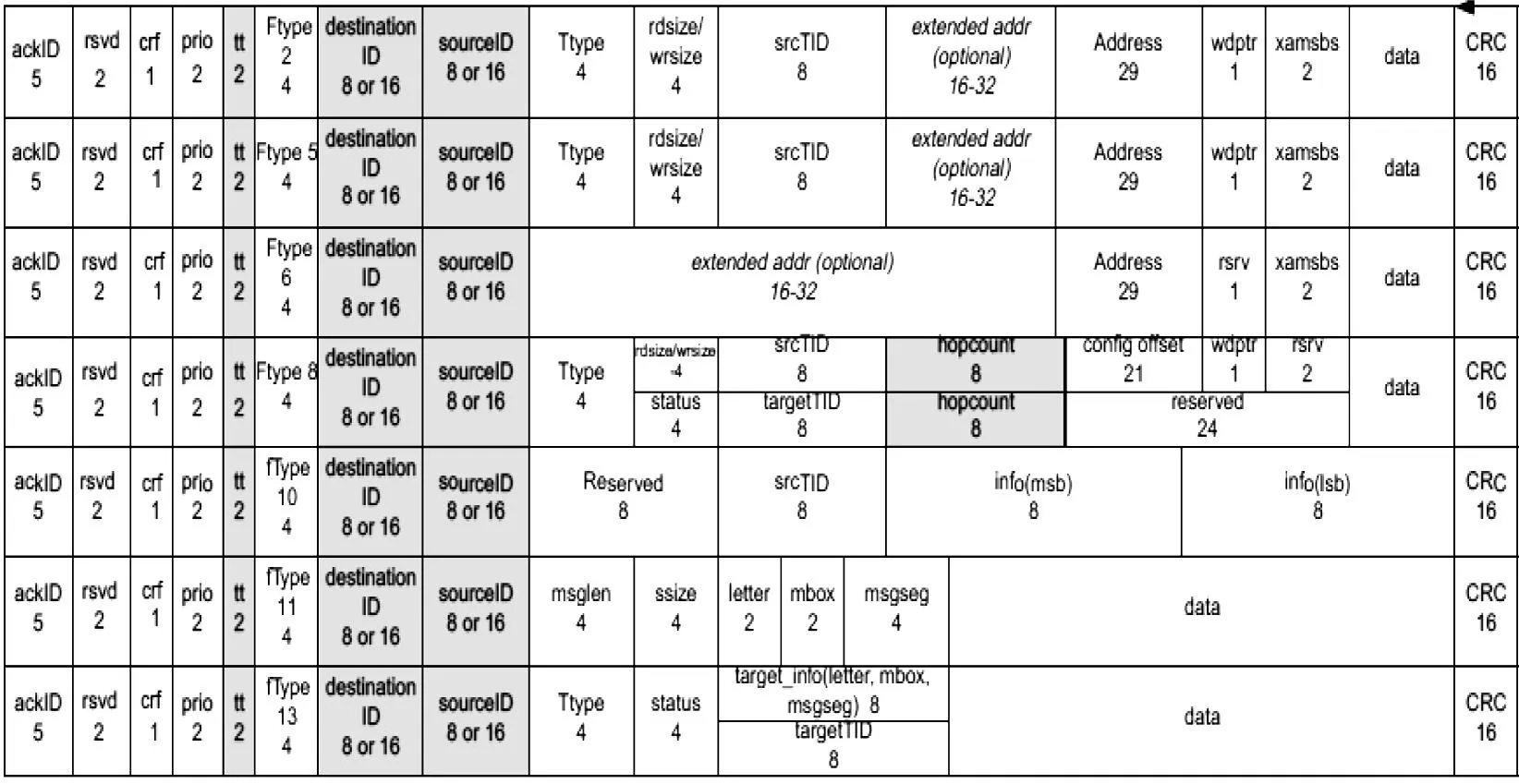

RapidIO數(shù)據(jù)交換流程是基于請求和響應(yīng)事務(wù)的。包是系統(tǒng)中各設(shè)備端點間的基本通信單元,發(fā)起端點產(chǎn)生一個請求事務(wù),該事務(wù)被發(fā)送至目標(biāo)端點。目標(biāo)端點產(chǎn)生一個響應(yīng)事務(wù)直至發(fā)起端點來完成該次操作。圖1顯示了FPGA中SRIO端點支持的幾種典型包格式。

圖1中,ackID為物理層的包號;crf為擴展優(yōu)先級位;prio為包的優(yōu)先級;tt為器件尋址模式,=00為8位地址模式,=01為16位地址模式;Ftype為包格式類型字段;Ttype為事務(wù)類型字段;srcTID為源事務(wù)ID號;目的地址和源地址的長度由tt字段決定。所有包以16位循環(huán)冗余校驗碼(CRC)結(jié)束。

圖1 FPGA中SRIO支持的典型包格式

1.2 SRIO IPcore的用戶接口

SRIO IPcore已經(jīng)實現(xiàn)了SRIO協(xié)議中的物理層、傳輸層和邏輯層的功能,用戶只需對用戶接口部分進行編程就可以實現(xiàn)FPGA與外部其他設(shè)備端點(以下以CPU處理器為例介紹,其他端點類似)的高速數(shù)據(jù)交換。

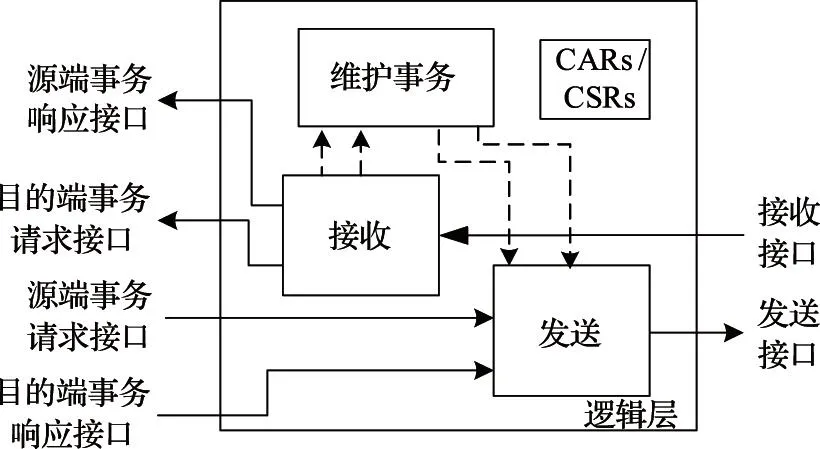

用戶接口分為源端事務(wù)接口和目的端事務(wù)接口。源端事務(wù)包括源端點發(fā)起的請求事務(wù)和目的端對該請求事務(wù)應(yīng)答回來的響應(yīng)事務(wù),目的端事務(wù)是目的端點發(fā)過來的請求事務(wù)及源端點對該請求事務(wù)進行應(yīng)答的響應(yīng)事務(wù)。圖2顯示了典型的有響應(yīng)事務(wù)操作過程。無響應(yīng)事務(wù)只有請求事務(wù),沒有響應(yīng)事務(wù)。

圖2 典型的有響應(yīng)事務(wù)操作過程

SRIO IPcore的用戶接口如圖3所示,包括源端事務(wù)請求用戶接口、源端事務(wù)響應(yīng)用戶接口、目的端事務(wù)請求用戶接口和目的端事務(wù)響應(yīng)用戶接口。

圖3 邏輯層用戶接口框圖

考慮在FPGA中實現(xiàn)SRIO協(xié)議的主要目的是為了高速的數(shù)據(jù)交換,即FPGA發(fā)送或接收高速數(shù)據(jù)流。為了編程邏輯實現(xiàn)的簡單可靠,本文在設(shè)計中主要實現(xiàn)了兩類事務(wù)接口:流寫(Ftype=6)和門鈴(Ftype=10),均采用8位器件地址和34位尋址模式。下面對源端事務(wù)請求接口的信號作簡要說明,其他接口信號與此類似。

ireq_sof_n表示一包的開始,低電平有效;ireq_eof_n表示一包的結(jié)束,低電平有效;ireq_vld_n數(shù)據(jù)有效標(biāo)志,只有在ireq_vld_n為低電平時其他接口信號才有效;ireq_rdy_n為邏輯層準(zhǔn)備就緒信號指示,其他信號必須在ireq_rdy_n有效的情況下才被邏輯層接受;ireq_prio[0:1]包的優(yōu)先級,取值范圍0~3,在數(shù)據(jù)包中一般取值0~2,最低優(yōu)先級為0,最高優(yōu)先級為3;ireq_ftype[0:3]表示包格式類型,ireq_ttype[0:3]表示事務(wù)類型,如表示流寫(SWRITE)的Ftype=6,流寫只有一種事務(wù)類型,所以Ttype的值可以忽略,表示寫(WRITE)的Ftype=5,Ttype有如下幾種情況(Ttype=4 NWRITE,Ttype=5 NWRITE_R等);ireq_dest_id[0:7]表示目的端的端點號,采用8位器件地址模式(tt=0),所以最多可以尋址256個端點(0xFF端點號一般不采用);ireq_tid[0:7]表示事務(wù)ID,在端點之間交換數(shù)據(jù)包時指示這是第幾個事務(wù),一般采用自動累加計數(shù)器,每傳輸一包使該字段加一;ireq_data[0:63] 8字節(jié)的傳輸數(shù)據(jù);ireq_addr[0:33] 34位字節(jié)尋址的地址偏移量。

一次流寫請求事務(wù)的時序圖如圖4所示:在ireq_rdy_n和ireq_vld_n有效的情況下, ireq_sof_n為低電平指示一包數(shù)據(jù)的開始,在ireq_sof_n有效時鐘周期內(nèi)采集其他接口信號的值;包開始后,在每個有效時鐘周期(ireq_rdy_n和ireq_vld_n都有效)采集ireq_data上的數(shù)據(jù),直到ireq_eof_n有效,采集最后一個數(shù)據(jù)值,從而一包完整的數(shù)據(jù)即可傳送到邏輯層內(nèi)部。

微小鈣化是超聲診斷甲狀腺癌的重要指標(biāo)之一,其特異性較強,尤其是對乳頭狀癌的特異性較高。因當(dāng)微小鈣化這一指征出現(xiàn)時,考慮甲狀腺癌的幾率較高。

圖4 SWRITE 源端請求時序圖

2設(shè)計實現(xiàn)

接口邏輯主要完成FPGA內(nèi)部邏輯與SRIO IPcore之間正確的數(shù)據(jù)交換,包括兩個方面的功能:把FPGA內(nèi)部數(shù)據(jù)流按照SRIO核的接口時序要求形成發(fā)送數(shù)據(jù)包;正確解析SRIO核接收到的其他端點發(fā)送來的數(shù)據(jù)包,并形成相應(yīng)的響應(yīng)事務(wù)包。

2.1 設(shè)計思路

設(shè)計中采用源端事務(wù)和目的端事務(wù)分離的模式。為了在FPGA中的邏輯實現(xiàn)方便,所有的數(shù)據(jù)傳輸都是采用8字節(jié)對齊的方式(每次傳輸?shù)臄?shù)據(jù)字節(jié)數(shù)為8的整數(shù)倍)。

在數(shù)據(jù)接收過程中,如果收到的是寫事務(wù),則根據(jù)接收到的偏移地址值把接收到的有效數(shù)據(jù)寫入相應(yīng)地址的RAM;如果收到的是門鈴,則判斷門鈴號。

數(shù)據(jù)發(fā)送的過程是先傳輸數(shù)據(jù),在一次數(shù)據(jù)傳輸完畢后發(fā)送門鈴信號通知目的端點讀取數(shù)據(jù),這樣就完成了一次數(shù)據(jù)的傳輸,接著啟動下一次的數(shù)據(jù)傳輸。在RapidIO協(xié)議中規(guī)定,每個事務(wù)包的有效數(shù)據(jù)載荷在1~256字節(jié)之間(無有效數(shù)據(jù)載荷的包除外)。為了最大化傳輸效率,在設(shè)計中采用除最后一個數(shù)據(jù)包外其他包的有效數(shù)據(jù)載荷都為256個字節(jié)。

2.2 具體實現(xiàn)

數(shù)據(jù)接收的實現(xiàn)過程相對簡單,只要根據(jù)接收到的地址把數(shù)據(jù)正確寫入接收數(shù)據(jù)的雙口RAM中,接收完畢給出標(biāo)志信號即可完成一包數(shù)據(jù)的正確接收。

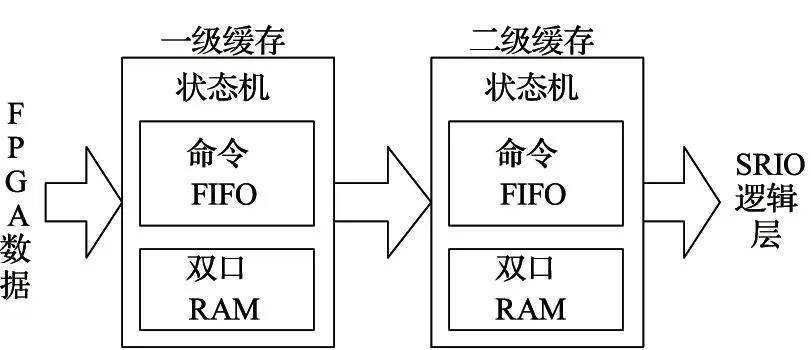

數(shù)據(jù)發(fā)送過程相對復(fù)雜一些,需要把傳輸?shù)臄?shù)據(jù)分成不大于256字節(jié)的包,并根據(jù)每包傳輸?shù)淖止?jié)數(shù)控制每包的偏移地址量,保證數(shù)據(jù)傳輸正確。由于RapidIO核每接收一個完整的包都要進行包數(shù)據(jù)的重組,且RapidIO核的緩存區(qū)大小也有限制,所以傳輸過程中需要握手信號控制雙方的通信時序。如圖5所示,設(shè)計中采用兩級緩存結(jié)構(gòu)。SRIO核的邏輯層時鐘是156.25MHz、數(shù)據(jù)位寬是64bit,F(xiàn)PGA的數(shù)據(jù)位寬和時鐘頻率很可能和SRIO核不匹配。為了解決時鐘域、數(shù)據(jù)位寬變換等問題,設(shè)計中加入了第一級緩存。由于每個RapidIO事務(wù)包的有效數(shù)據(jù)載荷不大于256個字節(jié),加入第二級緩存完成數(shù)據(jù)分包功能,把FPGA的輸入數(shù)據(jù)分成不大于256個字節(jié)的RapidIO流事務(wù)包。

圖5 具體實現(xiàn)框圖

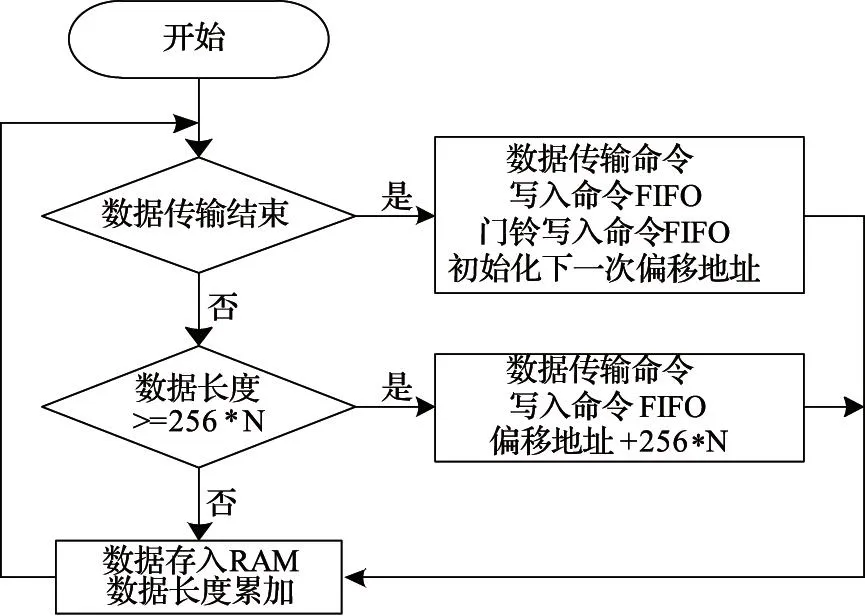

第一級緩存主要實現(xiàn)與FPGA傳輸數(shù)據(jù)的接口。為了防止數(shù)據(jù)丟失,第一級雙口RAM的容量根據(jù)實際需要可以設(shè)置足夠大的空間。命令FIFO每傳輸256*N個字節(jié)數(shù)據(jù)或數(shù)據(jù)傳輸結(jié)束寫一次。命令FIFO存儲的內(nèi)容包括目的端點號、包格式類型、事務(wù)類型、偏移地址量、雙口RAM中數(shù)據(jù)的起始地址和數(shù)據(jù)長度。在每次數(shù)據(jù)傳輸結(jié)尾,要把這次傳輸?shù)淖止?jié)總長度和一些附加信息傳輸出去,最后傳輸門鈴給對方,通知對方接收數(shù)據(jù)。流程如圖6所示。

圖6 第一級緩存寫狀態(tài)機

第二級緩存是把第一級緩存的數(shù)據(jù)包按照RapidIO協(xié)議分包,并最終實現(xiàn)與RapidIO邏輯層的接口時序。流程如圖7所示。首先判斷第一級FIFO是否為空,如果不為空,讀取FIFO中的信息,根據(jù)讀出的包格式類型、數(shù)據(jù)在第一級RAM中的起始地址和數(shù)據(jù)長度,產(chǎn)生RapidIO傳輸包。如果數(shù)據(jù)長度大于256個字節(jié),則讀取256個字節(jié),產(chǎn)生數(shù)據(jù)長度為256個字節(jié)的SWRITE事務(wù)包,直到數(shù)據(jù)長度不大于256個字節(jié)產(chǎn)生最后一個寫事務(wù)包。

圖7 第二級緩存寫狀態(tài)機

由于RapidIO協(xié)議是基于交換結(jié)構(gòu)的,在數(shù)據(jù)正常通信前必須要配置整個系統(tǒng)的交換路由關(guān)系,在系

統(tǒng)配置期間是不能正常通信的,所以在最終的設(shè)計中用戶接口要加入通信使能開關(guān),在系統(tǒng)配置完畢之前不能開始數(shù)據(jù)傳輸。

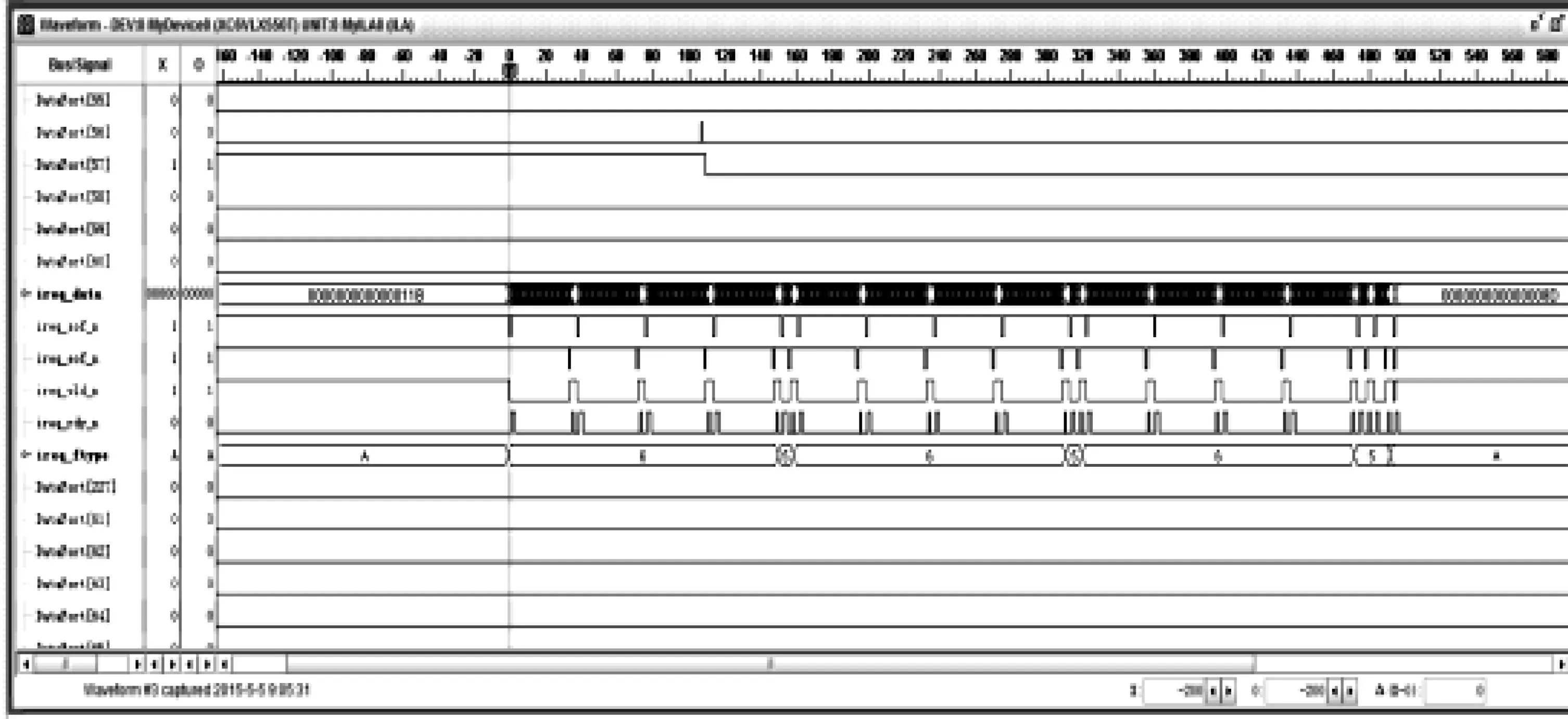

最終的設(shè)計采用VHDL語言在Xilinx公司的XC6VLX550T上實現(xiàn)。為了實現(xiàn)一對多的數(shù)據(jù)交換功能,設(shè)計實現(xiàn)中增加了第一級緩存雙口RAM容量,同時加入更多的命令FIFO深度來實現(xiàn)多點通信能力。按照RapidIO協(xié)議成功發(fā)送數(shù)據(jù)如圖8所示,在ireq_rdy_n和ireq_vld_n都為低電平的情況下 ireq_sof_n為低電平指示一包數(shù)據(jù)的開始,在ireq_sof_n有效時鐘周期內(nèi)采集其他接口信號的值,包括優(yōu)先級、數(shù)據(jù)長度、事務(wù)類型、節(jié)點號、起始地址等;包開始后,在每個有效時鐘周期(ireq_rdy_n和ireq_vld_n都為低電平)采集ireq_data上的數(shù)據(jù),直到ireq_eof_n有效,采集最后一個數(shù)據(jù)值,從而一包完整的數(shù)據(jù)即可傳送到邏輯層內(nèi)部。

圖8 發(fā)送數(shù)據(jù)成功時序圖

3結(jié)束語

RapidIO是面向系統(tǒng)互連和交換結(jié)構(gòu)的標(biāo)準(zhǔn),具有握手協(xié)議簡單、低緩沖開銷等特點。FPGA的高速邏輯陣列、高級I/O能力和可重編程性,應(yīng)用FPGA來實現(xiàn)RapidIO協(xié)議變得簡便可行。RapidIO技術(shù)使FPGA的接口適應(yīng)能力大大提高,使交換結(jié)構(gòu)的使用設(shè)備設(shè)計和升級更加靈活。

RapidIO用戶接口實現(xiàn)中,由于需要適應(yīng)不同接口位寬和不同傳輸速率的數(shù)據(jù)流,并且RapidIO的邏輯層接口也有嚴(yán)格的時序要求,為了接口邏輯的適用性更強,設(shè)計中采用了兩級緩沖機制,第一級緩沖實現(xiàn)FPGA數(shù)據(jù)流的存儲和位寬變化,第二級緩沖用來實現(xiàn)與RapidIO邏輯層的接口時序。在時序關(guān)系調(diào)整正確后,第二級緩沖的邏輯就可以固定下來,因此只需修改第一級緩沖的邏輯來適應(yīng)不同速率和位寬的數(shù)據(jù)流傳輸。RapidIO程序具有較強的通用性和可移植性。

參考文獻(xiàn):

[1]Sam FullerRapidIO嵌入式系統(tǒng)互連[M].北京:電子工業(yè)出版社,2006.6.

[2]LogicCORE IP Serial RapidIO v5.5 user guide,Xilinx Inc,2010.4.

Design and implementation of FPGA-based Serial RapidIO protocol

XU Shu-jun, HUANG Liu, NIU Dai-nan, WANG Rui

(No.724 Research Institute of CSIC, Nanjing 211153)

Abstract:The RapidIO protocol and the Serial RapidIO (SRIO) IPcore user interface (UI) are introduced, on the basis of which the programming method of the SRIO IPcore exchange architecture on the FPGA is described in detail. The two-stage buffer mechanism is adopted to realize the conversion of the bit width and the data rate and complete the high-speed data communication between multiple SRIO nodes. The RapidIO program features strong generality and portability.

Keywords:FPGA; SRIO IPcore; RapidIO; high-speed communication; serial port

中圖分類號:TN911.7

文獻(xiàn)標(biāo)志碼:A

文章編號:1009-0401(2015)04-0036-04

作者簡介:許樹軍(1985-),男,工程師,碩士,研究方向:雷達(dá)信號處理;黃镠(1986-),男,工程師,碩士,研究方向:雷達(dá)信號處理;牛戴楠(1982-),男,工程師,碩士,研究方向:高速電路板設(shè)計和數(shù)字信號處理;王銳(1982-),男,工程師,碩士,研究方向:雷達(dá)信號處理。

收稿日期:2015-04-04;修回日期:2015-05-09