一種機載相控陣雷達波控系統設計

(中國電子科技集團公司第三十八研究所,安徽合肥230088)

0 引言

相控陣技術廣泛地應用于軍事民用的各個領域,其主要特點和優點就是天線系統能夠實現快速靈活的波束掃描,為雷達系統更好地完成對目標的搜索與跟蹤提供了必要的條件。波控系統不僅要為天線掃描提供正確的相位碼,還要滿足波束轉換的速度要求,做到迅速精確地布相,同時還要具有陣面監視與狀態控制能力,因此相控陣雷達波束控制系統設計的好壞,對整個雷達系統能否實現其強大的功能是至關重要的[1]。本文介紹了一種機載相控陣雷達波控系統的設計,具有小型高速、可靠性高與靈活性高等特點,適用于中型及大規模相控陣雷達設計。

1 系統設計實現

1.1 波控系統架構設計

波控設備是安裝在載機平臺的艙外天線單元內部,根據雷達任務要求,需要完成1 000多個T/R組件的數據和時序控制任務。系統設計時,考慮到波控的計算任務量不是很大,可由雷達綜合處理單元中的時序監控模塊完成波控碼的計算,這樣可以省去計算機模塊的設備量。另外根據總體要求,對天線陣面上的波控接口、T/R組件及組件調制電源進行一體化設計,形成通用SAM多功能板模塊,既減少了單元之間的電纜連接,又有利于信號傳輸的穩定性,實現了波控及整個天線設備的小型化設計要求。

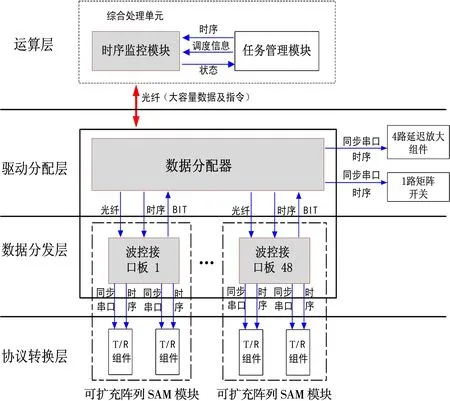

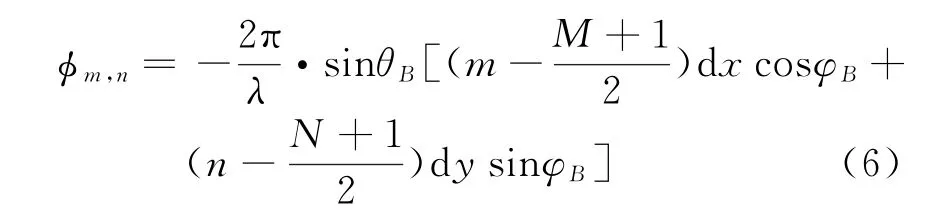

鑒于前述幾個方面的考慮,波控設計采用分級架構,從上至下各層級分別為運算層、驅動分配層、數據分發層和協議轉換層,具體框圖如圖1所示。

圖1 雷達陣面波控分級架構

運算層設備是指雷達任務電子的綜合處理單元,該單元包括時序監控模塊和任務管理模塊等,波控的移相碼運算功能就是嵌入在時序監控模塊中。時序監控模塊收到任務管理模塊的控制指令后,提前一個波位周期計算出所有1 000多個T/R組件的移相碼值,然后將這些數據打包,通過光纖高速線送給波控。時序監控模塊同時產生整機的時序觸發,并轉發給波控。

驅動分配層設備是由數據分配器實現,主要完成大容量數據的分發任務。數據分配器位于天線陣面,接收時序監控模塊送來的光纖打包數據,在FPGA(現場可編程邏輯陣列)內部對數據進行分析處理后,再根據數據去向,重新生成48路子模塊光纖信號,定向送至陣面48個SAM多功能板模塊中的波控接口。數據分配器還從打包數據中解析出陣面延遲組件和矩陣開關的控制數據和時序信號,送至延遲放大組件和矩陣開關。另外數據分配器還負責采集陣面電源及組件的BIT信息,回傳給時序監控模塊。

數據分發層設備由48個波控接口組成。波控接口位于48塊一體化設計可擴充SAM多功能板模塊的內部,每個波控接口負責將數據分配器送來的子模塊打包數據,解析為32路串行數據信號和時序信號,同步發送給多功能板模塊內的32個T/R組件。波控接口完成對48組T/R組件的移相碼分配和時序控制。

協議轉換層設備指位于T/R組件內部的ASIC芯片,數量為48個,可以將波控接口送來的同步串行信號轉換為并行數據,用來控制T/R組件內部的移相器、衰減器和多路開關,這部分功能由T/R組件設計自行完成。

1.2 移相碼設計

波控系統根據天線波束指向信息,首先計算相應方位、仰角上的相位初始值,再根據初始值計算天線陣列中每個移相器單元的相位,最后控制驅動移相器移相,使天線波束指向規定的方向,實現天線在方位角φ和仰角θ這兩個方向上的任意掃描[2]。

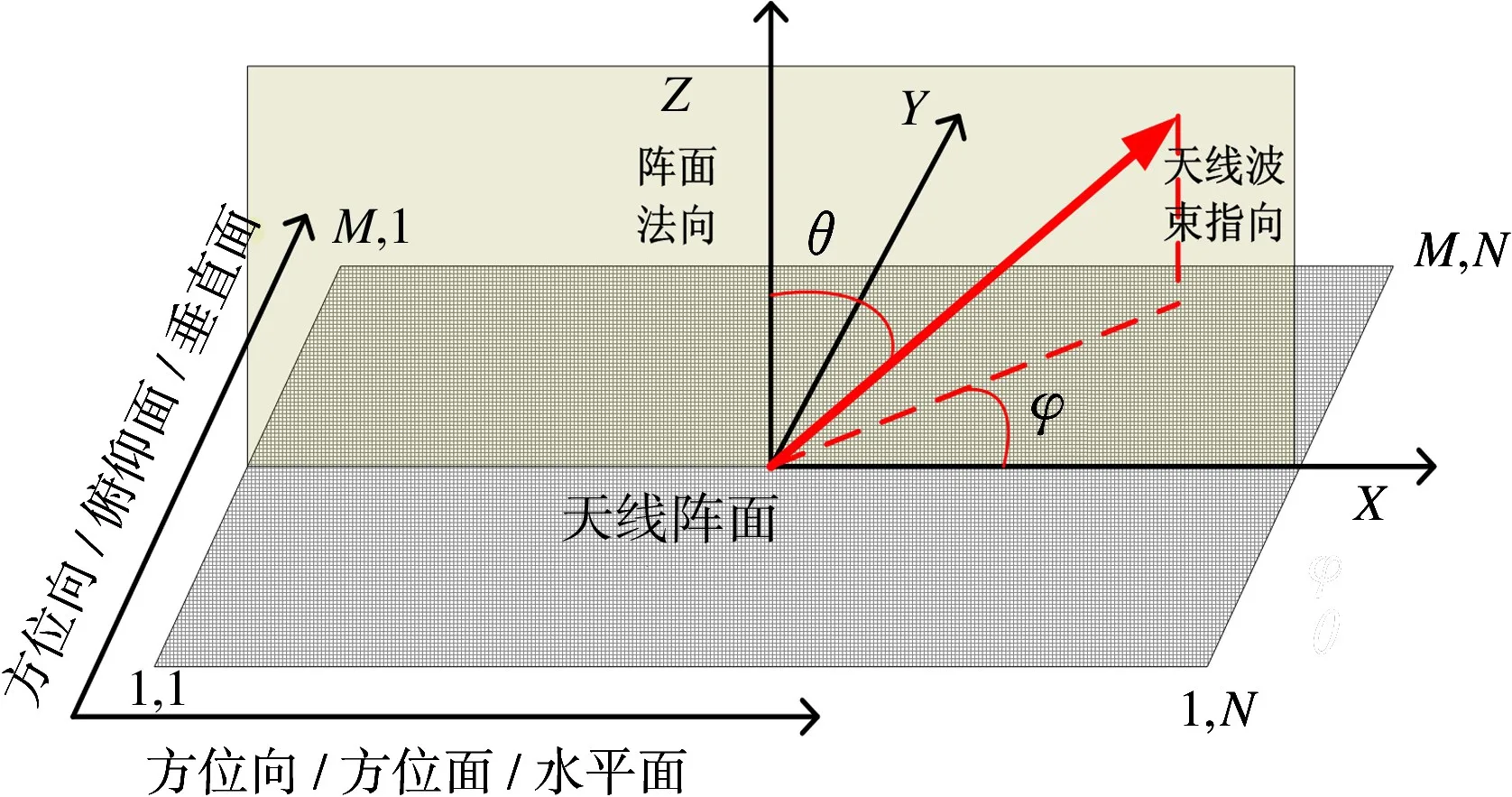

根據雷達總體要求,波控系統需要實現二維天線陣面的移相控制。整個陣面在XY平面上,共有16×72個天線單元,天線單元間距分別為dx(X軸方向)和dy(Y軸方向)。二維相控陣天線陣面天線單元排序及陣面坐標定義如圖2所示。

圖2 天線陣面天線單元排序及坐標圖

在上述N行M列的相控陣天線中,若取陣面中心為坐標原點,當要求波束指向為θB和φB時,依據二維分離布相法則,則第n行的相位值為

第m列的相位值為

式(1)和式(2)中,

第n行第m列單元的相位值為

式(6)中相關參數dx,dy,N,M是確定的,n=1,2,…,16;m=1,2,…,72。

根據確定的波束指向和陣面參數,可以計算出陣面布相所需的單元相位值φm,φn和

實際掃描工作時,天線系統為了獲得較低副瓣的天線波束,在由天線近場測試得出各天線單元的波程校正后,通過改變波控碼來進行相位修正,使天線相位誤差變為零。因此上式還應疊加上相位值Z(n,m),Z(n,m)為陣面中第(n,m)單元的移相器本身的校正同波程校正之和(該值為固定值,由天線實測數據確定)[4]。

本系統設計中,波控移相碼的計算任務是嵌入在時序監控模塊的軟件處理中。時序監控模塊在完成某個波束指向的移相碼計算后,通過光纖數據通道,將移相碼連同時序觸發打包送給波控的數據分配器單元。

1.3 系統單元電路設計

依據分級架構設計思想,波控系統需要設計1個數據分配器和48個波控接口板。

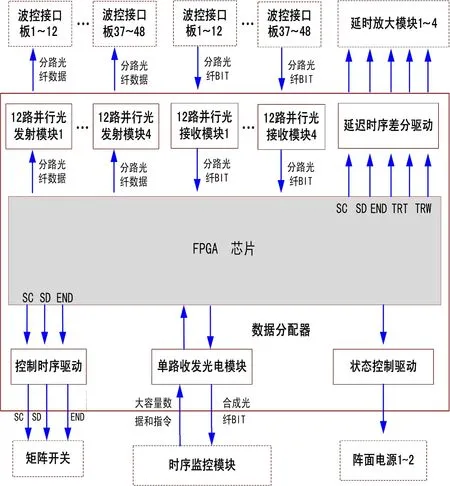

1)數據分配器設計

數據分配器接收時序監控送來的波控碼和波形碼,經過數據解析和重新編碼后,分發給波控接口板。數據分配器還收集波控接口的BIT信息,回傳給時序監控模塊,并產生2路陣面電源控制、以及4路延遲放大模塊和1路矩陣開關的控制時序。數據分配器的功能框圖如圖3所示。其主要設計包括多路光纖收發模塊和FPGA電路。

(1)多路光纖模塊設計

數據分配器分發的光纖通道有48路,為了實現功能及滿足小型化和環境適應性等的要求,多路光纖模塊選用中航光電的HTA8528/8529型12路并行光模塊。多路光纖模塊共4組,用于數據分配器向波控接口板發送T/R相位碼和時序信號等。模塊的中心波長為850 nm,提供總速率達75 GB/s的數據傳輸。單個光模塊使用集成的MT式尾纖接口,大大減小互聯尺寸,封裝形式為LCC48,有12個獨立并行通道。

(2)FPGA電路設計

圖3 數據分配器功能框圖

設計使用的主控制選用Xilinx公司XC7VX485T芯片。該器件擁有485K個邏輯單元、8000Kb內核RAM、56個高速GTP(高速串行收發器),最大700個I/O等資源,可以滿足系統48路光纖通道的設計需要。電路設計中最主要的任務是GTP模塊設計和光纖數據分發傳輸設計,編程工具是ISE14.7。

①GTP模塊設計

數據分配器調用芯片自帶的軟核GTP模塊來實現光纖數據的處理,軟核的配置應用依據廠家提供的手冊進行。設計使用的GTP軟核數量有49個,其中1個用于接收時序監控模塊傳來的指令數據,另外48路用于數據分發。設計的GTP模塊數據寬度為16 bit,經8B/10B編碼后,并行數據寬度為20 bit,采用2.5 GB/s的速率傳輸。

② 光纖數據分發傳輸設計

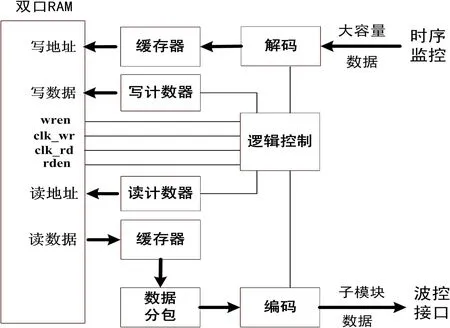

從時序監控模塊傳來的大容量數據和指令,經過解碼和緩存后,首先按照指定規則存入雙口RAM,而后根據時序要求順序從RAM中讀出。讀出的數據先進行分組,再重新編碼,經電光轉換后發送至不同的波控接口。分發傳輸控制的邏輯圖如圖4所示。

電路中使用的雙口RAM是一種可提供2組獨立的控制線、地址線和數據線的存儲器序列,其端口允許對存儲器任一單元單獨進行讀/寫訪問,設計時RAM讀操作快于寫操作,保證了光纖數據的傳輸時間要求。

圖4 分發傳輸控制的邏輯圖

分組后的子模塊數據還需通過特定的編碼才能發給波控接口板,最終輸出的子模塊光纖數據包中除了有移相碼、包頭、包尾等信息外,還有采樣頻率、帶寬等與數據處理有關的信息。表1就是數據分配器與波控接口板的子模塊光纖數據傳輸協議。

表1 子模塊光纖數據傳輸協議

2)波控接口板設計

波控接口板共設計為48塊,位于SAM多功能板內部。每個波控接口板都通過1路光纖高速串行線,接收數據分配器送來的區段波控碼和波形碼,實現的功能有:解析SAM模塊內每路T/R組件需要的移相碼和衰減碼,并將移相數據通過并串轉換送至T/R的接口芯片;產生每路T/R組件需要的時序信號和開關信號,并將它們變換驅動后送至T/R的接口芯片;匯集每路T/R組件的BIT信息,打包后通過光纖回送給數據分配器。

(1)波控接口FPGA電路設計

波控接口板的主控制芯片選用了Xilinx公司XC7A200T型FPGA來進行設計。該型FPGA擁有200K的邏輯單元、2000Kb RAM、16個高速GTP收發器,最大500個I/O資源,配合外圍的電平轉換電路,可以滿足數據處理和信號傳輸設計要求。

波控接口板中FPGA設計主要包含GTP收模塊、GTP發模塊和時序產生模塊。GTP收模塊解析數據分配器發送的光纖32路組件的相位碼,并對它們進行并串轉換。GTP發模塊將SAM模塊內部T/R組件回饋的BIT(機內信息檢測)信息以及自身的BIT信息,通過光纖回送給數據分配器。時序產生模塊根據接收到的波形碼和導前信號,產生每路T/R組件需要的時序信號和開關信號。

(2)組件保護電路設計

T/R組件是天線系統中的關重件,其自保護能力比較弱,需要對它進行保護設計,波控對組件的保護主要通過以下方式實現。

① 功率電源開關控制

T/R組件的功率開關電源的打開時機,需要波控判斷好其他系統狀態都正常以后,才能由波控接口板執行電源的開關控制。

② 硬件時序保護控制

波控接口根據系統的工作模式,對T/R組件的功率開關脈寬進行限制,避免組件功率過高而損壞器件。

③ 上電過程電平保護

T/R組件對控制信號中最敏感的就是發射調制TRT信號,該信號要求在波控上電初始化的時候不能是高電平,否則組件會因功率過高而損壞。但由于波控的主控制FPGA芯片在上電配置期間,其IO輸出的狀態為不穩定態,所以必須要對其進行保護設計。設計時,首先將FPGA配置I/O電平控制PUDC接高電平,使配置期間所有的I/O處于浮空狀態,然后將TRT的驅動芯片使能端接上拉電阻,輸出接下拉電阻,確保配置期間TRT為低。

2 系統關鍵技術

波控系統中的關鍵技術是多路光纖傳輸技術。為滿足小型化設計、一體化設計以及技術指標等的要求,波控設計使用了多組12合1光纖收發模塊,實現了大容量數據的分發處理及時序控制任務。多路光纖傳輸技術的難度主要體現在大容量數據分發傳輸設計、多路高速通道布板設計、系統電源和時鐘電路設計等方面。

1)大容量數據分發傳輸設計

波控設備中的光纖通道達48路,每路又分為收通道和發通道。高速通道中每個波位的數據長度達43 008 bit,這組數據中包含了多種模式、狀態、頻點、指向、帶寬、移相碼、位置、BIT等信息,其分發傳輸非常復雜,時序要求很高。波控在設計時,借助GTP軟核,對多通道高速數據進行了編解碼控制、相位對齊、串并轉換、時鐘激勵、阻抗和電平匹配等措施,實現了快速準確的布相任務。

2)多路高速通道布板設計

由于設計中使用了大量的高速信號,波控在電路布板時,除了要進行信號分層設計外,還要對各路高速信號線進行屏蔽,充分考慮信號的走線,取最優最短的路徑,并且避免信號間相互干擾。另外由于系統要求電源、微波、數字、光纖信號等進行一體化集成設計,設備電磁環境變得復雜,布局布線難度加大。在進行布板時,運用了多組電容、電感的濾波和信號屏蔽措施,滿足了電磁兼容性要求。

3)電源和時鐘電路設計

由于可編程電路及多種驅動電路芯片的大量應用,波控的電源達6個品種,全部由波控自己產生,為了保證電路的穩定性,電源設計時,不僅要考慮電源的帶載能力,還要考慮不同電源的上電順序、紋波要求、隔離要求,濾波電容和磁珠的使用位置、數量和容量等。另外由于高速數據通道多,時鐘設計時要特別注意不同芯片之間的匹配電阻、電容和電平要求,其走線路徑和屏蔽要求也非常嚴格。

3 結束語

采用分級架構設計的波控是實現中型及大規模相控陣雷達波控的有效途經之一。設計中采用光纖互聯高速數據編解碼控制技術,既實現了快速布相任務,又簡化了陣面的走線,滿足了快速靈活及小型化設計要求。系統中數據分配器單元的外形同SAM多功能板模塊的外形大致相同,有利于陣面的總體結構設計。筆者依此思想設計的一套控制1 000多個移相單元的波控系統,經過一年多的驗證,性能穩定可靠,完成了天線近場測試及雷達系統的外場聯試,實現了對空中目標的觀察。對于更大規模的天線陣面波控設計,只需要增加數據分配器單元及波控接口單元的數量即可,滿足武器裝備模塊化的設計要求。

[1]陳俊,馮武.現代相控陣雷達天線波控技術研究[J].數字技術與應用,2014(2):64-67.

[2]段玲琳,段曉超.星載大型相控陣雷達波控系統設計研究[J].合肥工業大學學報(自然科學版),2014,37(3):319-322.

[3]張光義,趙玉潔.相控陣雷達技術[M].北京:電子工業出版社,2006:30-76.

[4]陳之濤,王雨陽,劉浩.一種發射通道校正技術的實現[J].雷達科學與技術,2012,10(3):332-335.CHEN Zhi-tao,WANG Yu-yang,LIU Hao.An Implementation of Calibration Method for Transmitting Channels[J].Radar Science and Technology,2012,10(3):332-335.(in Chinese)