一種基于Verilog的任意整數分頻器實現方法*

谷 濤,黃 勇,盧 晨

(廣西民族大學 信息科學與工程學院,廣西 南寧 530006)

0 引言

1 任意整數分頻器的實現框架

Verilog HDL是電子設計的主流硬件描述語言之一(另一個是VHDL),采用硬件描述語言完成電路設計是當前數字電路設計的主流方法.Quartus II是Altera公司的綜合性PLD/FPGA開發軟件,支持原理圖、VHDL、VerilogHDL 以及 AHDL(Altera Hardware Description Language)等多種設計輸入形式[1].Modelsim是MENTOR公司推出的業界最優秀的HDL語言仿真軟件,Quartus II可以方便地調用Modelsim進行電路設計的RTL級和門級仿真.盡管在目前大部分設計中,可以使用芯片廠家集成的鎖相環資源進行時鐘的分頻,但通過硬件描述語言設計的時鐘分頻電路可以節省芯片內部的鎖相環資源,而且消耗不多的邏輯單元就可以達到對時鐘操作的目的.所以在時鐘要求不高的電路設計中,使用語言來說設計分頻電路是必要的也是廣泛應用的.筆者以Quartus II為設計平臺,基于Verilog語言設計了一個任意整數分頻器,并在Modelsim中完成仿真[2-3].

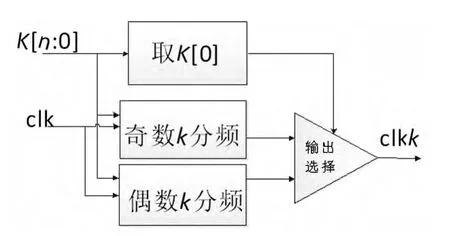

任意整數不是奇數就是偶數,所以筆者的設計思路分別對輸入時鐘源進行奇分頻和偶分頻,然后再判斷分頻比是奇數還是偶數.如果是奇數則選擇奇分頻器輸出的信號為最終輸出信號(此時偶分頻器在執行分頻,但分頻比不符合要求),如果是偶數則選擇偶分頻器輸出的信號為最終輸出信號(此時奇分頻器在執行分頻,但分頻比不符合要求).電路構造簡單,在一定程度上縮短了輸入到輸出的時延.任意整數分頻器的實現框架如圖1所示.

如圖1所示,輸入信號clk分別經過奇數分頻和偶數分頻,然后根據分頻比是奇數還是偶數,選擇分頻后的輸出作為最終的輸出信號clkk.分頻比是奇數,選擇奇數分頻后的輸出,是偶數則選擇偶數分頻后的輸出.對于二進制形式的分頻比k,只需要根據最后一位是1還是0即可判定它是奇數還是偶數.例如輸入分頻比是k[3∶0],可以根k[0]來判斷分頻比的奇偶性.

圖1 任意整數分頻器的實現原理框圖Fig.1Implementation principle of arbitrary integer frequency divider

2 實現框架中各部分的原理

2.1 奇數分頻的實現原理

k倍奇數分頻有兩種實現辦法:

1)首先進行k/2分頻(帶小數,即等于(k-1)/2+0.5),然后再進行二分頻得到[4].這種辦法需要先實現小數分頻,比較麻煩,所以筆者采用第二種奇分頻方法.

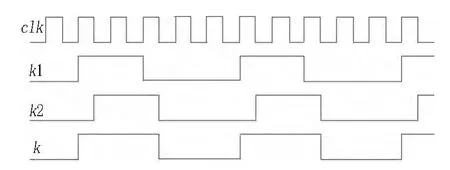

2)通過計數器來實現.一般的方法為:對于實現占空比為50%的k倍奇數分頻,首先進行輸入時鐘上升沿觸發模k計數(從0計到k-1),計數到1時輸出時鐘翻轉,然后經過(k-1)/2個脈沖上升沿計數到(k+1)/2時輸出時鐘再次翻轉.然后繼續計數,計到k-1時計數器清零繼續計數,再次計到1時輸出時鐘再翻轉一次.這樣可以得到一個占空比非50%的奇數k分頻時鐘.再者同時進行輸入時鐘下降沿觸發模k計數(從0計到k-1),計數到1時輸出時鐘翻轉,然后經過(k-1)/2個脈沖下降沿計數到(k+1)/2時輸出時鐘再次翻轉.然后繼續計數,計到k-1時清零并繼續計數,再次計到1時輸出時鐘再翻轉一次.這樣得到另一個占空比非50%的奇數k分頻時鐘.兩個模k計數依次這樣循環下去,得到的輸出時鐘為兩個占空比非50%的輸入時鐘k分頻.把它們相或運算,得到占空比為50%的奇數k分頻時鐘.以5分頻為例,奇數分頻的實現原理如圖2.

圖2 5分頻原理圖Fig.2Schematic diagram of frequency divider(mode=5)

以5分頻為例,在圖2中可以看到,k1內部的計數器對clk的上升沿計數,k1的輸出波形初始為低電平,遇到第1個上升沿計0,遇到第2個上升沿計1,此時k1的輸出波形翻轉為高電平.遇到第3個上升沿計2,遇到第4個上升沿計3,此時k1的輸出波形翻轉為低電平.遇到第5個上升沿計4,第6個上升沿計數器清零,第7個上升沿計1,此時k1的輸出波形再次翻轉,為高電平.然后依次類推……我們可以看到從第2個上升沿到第7個上升沿之間,k1的輸出波形形成了一個完整的脈沖.隨著第8個及后續上升沿的到來,k1的計數器計數和輸出波形依次循環下去.k1的輸出波形是對clk的5分頻,但占空比不是50%.k2的內部計數器計數和輸出波形翻轉辦法與k1類似,只不過k2是對clk的下降沿計數.從圖2中還可以看到把k1和k2相或,可以得到占空比為50%的5分頻信號k.

2.2 偶數分頻的實現原理

偶數分頻原理為:當進行占空比為50%的k倍偶數分頻時,可以由待分頻信號clk的上升沿去觸發計數器計數.當計數器從0計數到(k/2)-1時,輸出信號進行翻轉,同時給計數器賦值為零.待分頻信號clk的下一個上升沿到來時重新從0開始計數,計數到(k/2)-1時,輸出信號再次進行翻轉,計數器再次賦值為零,以此循環下去.采用這種方法可以實現占空比為50% 的任意偶數倍分頻[5].這里不再做詳細敘述.

2.3 輸出信號選擇原理

因為可以根據k[0]來判斷分頻比k[n∶0]的奇偶性,所以把k[0]作為選擇輸出信號的依據.k[0]=1選擇奇數分頻的輸出作為最終輸出信號,k[0]=0選擇偶數分頻的輸出作為最終輸出信號.這個在Verilog中可以用條件賦值語句實現,具體語句將在下面的程序中給出.

3 任意整數k分頻器的完整Verilog設計程序及測試程序

3.1 任意整數k分頻器的完整Verilog設計程序

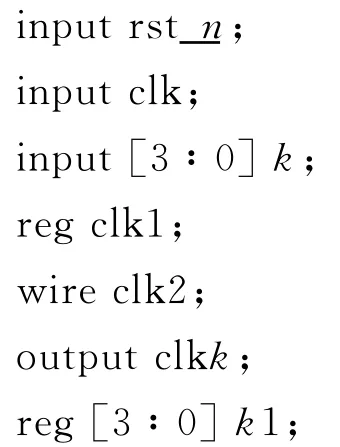

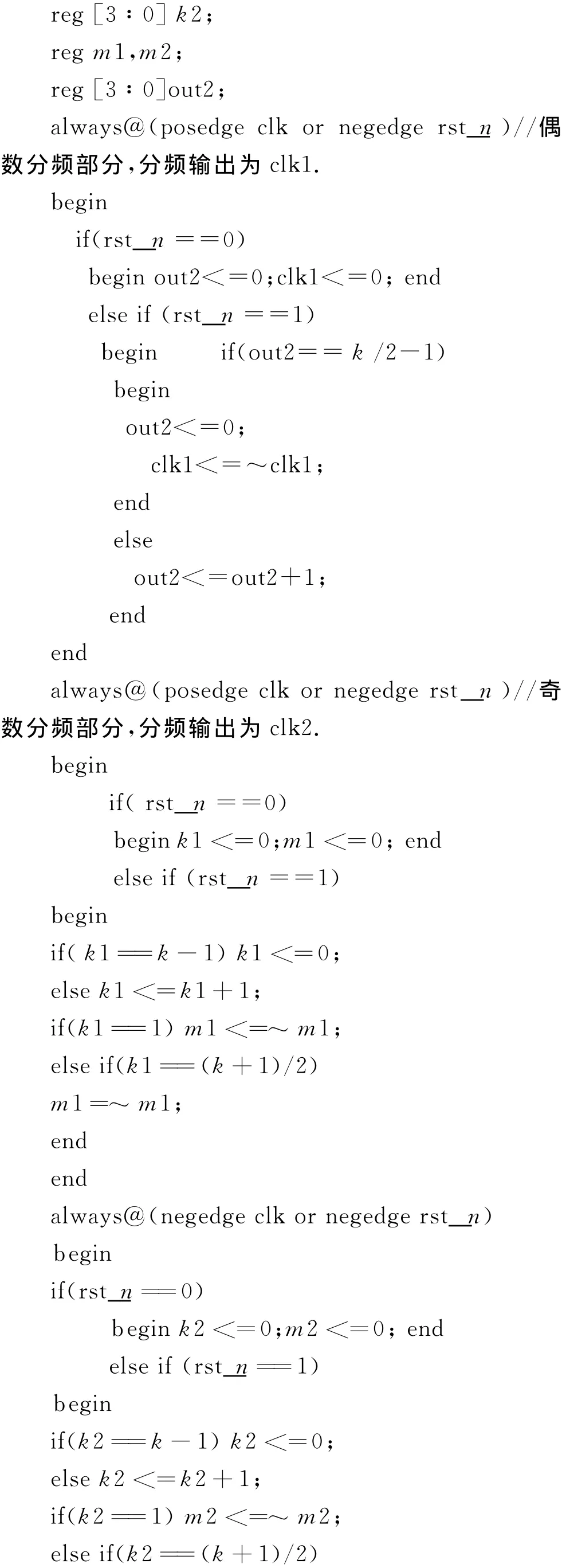

module kfenpin(rst_n,clk,k,clkk);// 該 例 中任意整數k為輸入值k

程序中rst_n是全局的復位信號;clk是輸入的待分頻時鐘信號;k是輸入的分頻比,該例程序中是4位二進制輸入信號,可以改變位寬來達到實現更大分頻比的目的;clkk是分頻后的輸出信號.

3.2 任意整數k分頻器的測試程序

任意整數k分頻器的測試程序如下:

4 仿真結果

在上述設計程序和測試程序下,在Quartus II程序中調用Modelsim,可以看到仿真結果.

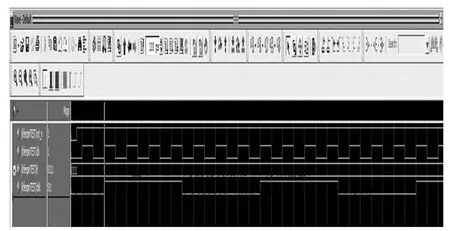

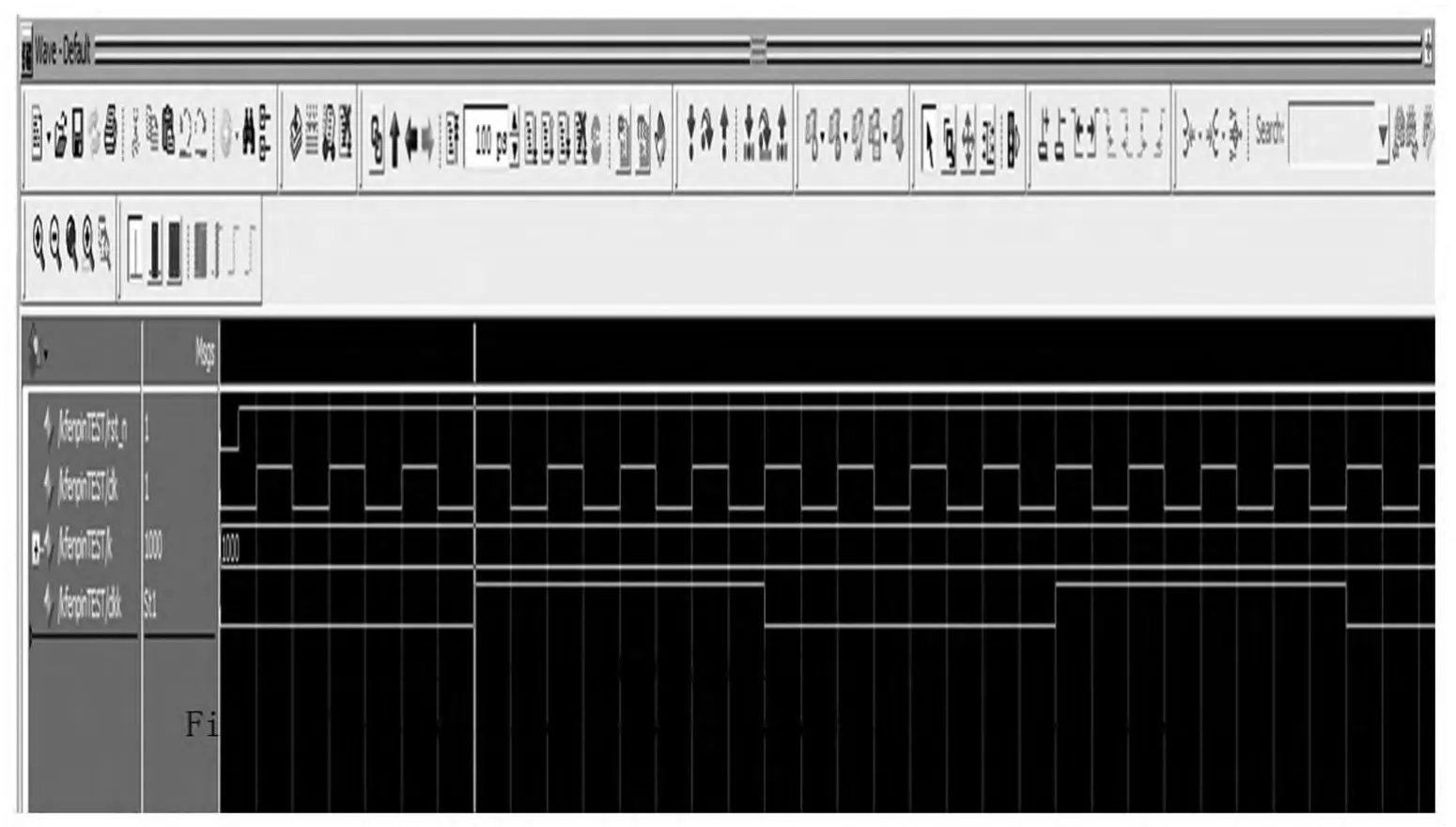

在測試程序中,k賦不同的值,就可以得到相應的分頻輸出.下面給出k=2,k=7,k=8的仿真結果:

可以看到除了最初的幾個周期外(具體幾個周期與分頻比有關),輸出信號是輸入信號的k分頻.該例程序的2分頻的仿真測試也可以通過.

圖3 k=2時的仿真結果(2分頻輸出)Fig.3The simulation results when k =2(2divider output)

圖4 k=7時的仿真結果(7分頻輸出)Fig.4The simulation results when k =7(7divider output)

圖5 k=8時的仿真結果(8分頻輸出)Fig.5The simulation results when k =8(8divider output)

[1]潘松,等.EDA技術實用教程-Verilog HDL版[M].北京:科學出版社,2013.

[2]帥旗.基于FPGA的全數字鎖相環的設計與實現[D].大連理工大學工程碩士學位論文,2013.

[3]張成.基于FPGA的全數字鎖相環的設計與應用[D].合肥工業大學碩士學位論文,2010.

[4]鄧玉元,等.數字電路中等占空比分頻器的實現[J].現代電子技術,2006(24).

[5]黃國達.基于FPGA的任意整數分頻器的設計[J].福建電腦,2013(7).