基于電阻鏈移相的時(shí)柵高速測(cè)量方法研究*

索龍博, 陳錫侯, 茍 李, 張?zhí)旌悖?曹 煥

(重慶理工大學(xué) 機(jī)械檢測(cè)技術(shù)與裝備教育部工程研究中心 時(shí)柵傳感及先進(jìn)檢測(cè)技術(shù)重慶市重點(diǎn)實(shí)驗(yàn)室,重慶 400054)

?

基于電阻鏈移相的時(shí)柵高速測(cè)量方法研究*

索龍博, 陳錫侯, 茍 李, 張?zhí)旌悖?曹 煥

(重慶理工大學(xué) 機(jī)械檢測(cè)技術(shù)與裝備教育部工程研究中心 時(shí)柵傳感及先進(jìn)檢測(cè)技術(shù)重慶市重點(diǎn)實(shí)驗(yàn)室,重慶 400054)

針對(duì)時(shí)柵位移傳感器因頻率響應(yīng)慢影響測(cè)量速率的問(wèn)題,提出了一種電阻鏈移相結(jié)合數(shù)據(jù)處理的方法。利用電阻鏈對(duì)時(shí)柵輸出信號(hào)進(jìn)行移相處理,采用多路模擬選擇器和整形輸出電路對(duì)移相后的信號(hào)分時(shí)輸出,運(yùn)用可編程片上系統(tǒng)(SOPC)技術(shù)進(jìn)行數(shù)據(jù)處理和誤差補(bǔ)償。實(shí)驗(yàn)結(jié)果表明:采用該方法采樣頻率由原來(lái)的400 Hz提高到12.8 kHz,大幅度提高了現(xiàn)階段時(shí)柵位移傳感器的頻率響應(yīng),使傳感器實(shí)現(xiàn)了高速實(shí)時(shí)測(cè)量。同時(shí)能夠有效地降低了隨機(jī)誤差,對(duì)極內(nèi)的誤差峰—峰值由1.5″降低為0.8″,測(cè)量精度提高了近1倍。

時(shí)柵; 電阻鏈; 多路模擬選擇器; 可編程片上系統(tǒng)

0 引 言

時(shí)柵位移傳感器采用相對(duì)運(yùn)動(dòng)雙坐標(biāo)系,將靜止坐標(biāo)系上的位置之差,轉(zhuǎn)換成運(yùn)動(dòng)坐標(biāo)系上的時(shí)間之差,從而實(shí)現(xiàn)“用時(shí)間測(cè)量空間”[1,2],其具有高精度和高分辨力、低成本、抗干擾能力強(qiáng)等諸多優(yōu)點(diǎn)。近年來(lái),時(shí)柵傳感器在業(yè)界表現(xiàn)出強(qiáng)大的競(jìng)爭(zhēng)力,正在向產(chǎn)品化、產(chǎn)業(yè)化方向發(fā)展,已在精密數(shù)控轉(zhuǎn)臺(tái)控制系統(tǒng)、傳動(dòng)誤差檢測(cè)系統(tǒng)以及國(guó)防精密加工中得到廣泛的應(yīng)用。根據(jù)時(shí)柵傳感器時(shí)間測(cè)量原理,在400 Hz的激勵(lì)頻率下,通過(guò)高頻時(shí)鐘插補(bǔ)動(dòng)、定測(cè)頭感應(yīng)信號(hào)正向過(guò)零點(diǎn)時(shí)間差的方式,使得傳感器的測(cè)量速率僅有2.5 ms/次,難以實(shí)現(xiàn)高速測(cè)量。

為了提高時(shí)柵傳感器的頻率響應(yīng),從而提高測(cè)量速率,實(shí)現(xiàn)高速測(cè)量,使其在同等的時(shí)間間隔內(nèi)采集更多的數(shù)據(jù)進(jìn)行平均處理以減小隨機(jī)誤差,從而提高傳感器的測(cè)量精度,現(xiàn)提出電阻鏈移相的方法。電阻鏈移相是一種常用的電子細(xì)分手段,一般用于光柵傳感器以提高角度測(cè)量的精度和分辨力。本文將其應(yīng)用于時(shí)柵傳感器的信號(hào)處理系統(tǒng)來(lái)提高傳感器的頻率響應(yīng),從而解決現(xiàn)階段時(shí)柵所存在的測(cè)量速率慢的問(wèn)題。在系統(tǒng)設(shè)計(jì)中采用可編程片上系統(tǒng)(SOPC)技術(shù)將信號(hào)的采集、處理、傳輸?shù)燃性诟咝阅墁F(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)上實(shí)現(xiàn),解決了移相后多路數(shù)據(jù)處理的實(shí)時(shí)性問(wèn)題。

1 時(shí)柵位移傳感器原理

1.1 結(jié)構(gòu)原理

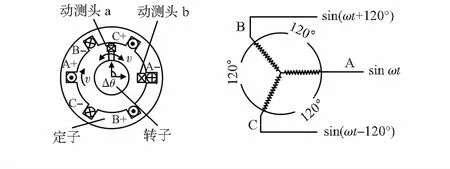

時(shí)柵傳感器的結(jié)構(gòu)主要包括定子、轉(zhuǎn)子、定子內(nèi)嵌線圈以及2個(gè)線圈繞制的測(cè)頭,如圖1所示。其結(jié)構(gòu)與三相交流電機(jī)類(lèi)似,在空間上互差120°的三相線圈中通入時(shí)間上互差120°的交流激勵(lì)電源后,定、轉(zhuǎn)子之間產(chǎn)生一個(gè)勻速旋轉(zhuǎn)磁場(chǎng),旋轉(zhuǎn)速度為V。兩個(gè)測(cè)頭置于旋轉(zhuǎn)磁場(chǎng)內(nèi),一個(gè)固定不動(dòng),稱(chēng)作定測(cè)頭;另一個(gè)隨轉(zhuǎn)子一起運(yùn)動(dòng),稱(chēng)作動(dòng)測(cè)頭,其運(yùn)動(dòng)速度為v。在已知旋轉(zhuǎn)磁場(chǎng)速度V的情況下,通過(guò)檢測(cè)旋轉(zhuǎn)磁場(chǎng)經(jīng)過(guò)兩個(gè)測(cè)頭的時(shí)間差ΔT,就可以得到轉(zhuǎn)子轉(zhuǎn)動(dòng)的角位移θ=VΔT[3](設(shè)兩個(gè)測(cè)頭重合的地方為起點(diǎn),即角位移為0)。

圖1 時(shí)柵傳感器結(jié)構(gòu)原理圖

1.2 時(shí)間測(cè)量原理

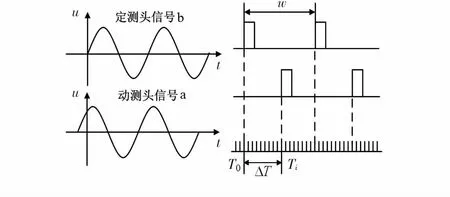

時(shí)柵傳感器的時(shí)間測(cè)量原理如圖2所示。首先通過(guò)零檢測(cè)電路將動(dòng)、定測(cè)頭上感應(yīng)出的兩路行波信號(hào)轉(zhuǎn)換為方波信號(hào);再利用高性能比相電路把動(dòng)、定測(cè)頭信號(hào)正向過(guò)零點(diǎn)之間的相位差轉(zhuǎn)換成為時(shí)間差,即完成時(shí)空轉(zhuǎn)換;最后采用高頻時(shí)鐘脈沖對(duì)該時(shí)間差進(jìn)行時(shí)鐘插補(bǔ),高頻時(shí)鐘脈沖的頻率大約在10 MHz以上[4]。每個(gè)時(shí)鐘脈沖對(duì)應(yīng)一定的空間角位移,對(duì)脈沖進(jìn)行計(jì)數(shù)就可實(shí)現(xiàn)位移測(cè)量,可根據(jù)式(1)計(jì)算出角位移值

(1)

式中Ti為動(dòng)測(cè)頭上升沿出現(xiàn)時(shí)刻;T0為定測(cè)頭上升沿出現(xiàn)的時(shí)刻;W為繞組節(jié)距;ΔT為動(dòng)、定測(cè)頭正向過(guò)零點(diǎn)之間的時(shí)間差。

圖2 時(shí)間測(cè)量原理圖

2 電阻鏈移相的應(yīng)用

在現(xiàn)有400 Hz的激勵(lì)頻率下,為實(shí)現(xiàn)對(duì)時(shí)柵信號(hào)在一個(gè)信號(hào)周期內(nèi)完成多次測(cè)量,提高傳感器頻率響應(yīng),實(shí)現(xiàn)高速測(cè)量。應(yīng)用電阻鏈移相原理設(shè)計(jì)了具有32路輸出的電阻鏈移相網(wǎng)絡(luò),將傳感器在一個(gè)信號(hào)周期內(nèi)只能測(cè)量一次,轉(zhuǎn)變?yōu)榭梢赃M(jìn)行32次測(cè)量,極大提高傳感器的頻率響應(yīng)。

2.1 頻率響應(yīng)的分析

現(xiàn)有時(shí)柵傳感器頻率響應(yīng)較慢的原因主要來(lái)自兩方面:一是電路處理方式的原因,因?yàn)闀r(shí)間行波信號(hào)過(guò)零點(diǎn)處的斜率最大,為了提高時(shí)柵傳感器的靈敏度,盡可能減少干擾對(duì)轉(zhuǎn)換時(shí)刻點(diǎn)的影響。整形輸出電路采用過(guò)零檢測(cè)電路實(shí)現(xiàn)。這種處理方式雖然提高了傳感器靈敏度,減小了干擾對(duì)信號(hào)轉(zhuǎn)換質(zhì)量的影響,但過(guò)零檢測(cè)的方式降低了傳感器的頻率響應(yīng),使得傳感器在一個(gè)信號(hào)周期內(nèi)只能進(jìn)行一次測(cè)量,嚴(yán)重影響傳感器的測(cè)量速率;二是激勵(lì)信號(hào)頻率的原因,時(shí)間行波的變化速率與激勵(lì)頻率呈正比關(guān)系。激勵(lì)信號(hào)頻率越高,其變化速率越快,采集一次數(shù)據(jù)的時(shí)間就越短,因此,傳感器的頻率響應(yīng)越高,測(cè)量速率越快,在相同的時(shí)間內(nèi)可采集更多的數(shù)據(jù)平均處理,測(cè)量的精度就越高。但激勵(lì)信號(hào)頻率越高,同樣的干擾對(duì)傳感器的影響就越大。且在插入的高頻時(shí)鐘頻率一定的情況下,脈沖當(dāng)量就越大,即分辨力就越低。要提高分辨力,就只能提高插入的高頻時(shí)鐘頻率,高頻信號(hào)對(duì)信號(hào)處理系統(tǒng)的設(shè)計(jì)和對(duì)電路板的電磁兼容性設(shè)計(jì)提出了更高的要求。因此,綜合考慮上述幾方面的因素,時(shí)間信號(hào)的頻率選為400 Hz[4]。根據(jù)時(shí)間測(cè)量原理傳感器在2.5 ms內(nèi)只能完成一次測(cè)量,其頻率響應(yīng)較慢,測(cè)量速率受到限制。

2.2 電阻鏈移相原理

電阻鏈移相作為一種常用的電子細(xì)分方法,常用于光柵信號(hào)的細(xì)分,以提高光柵傳感器的分辨力和精度,其具有細(xì)分能力強(qiáng)、精度較高、電阻元件容易獲得等優(yōu)點(diǎn)。

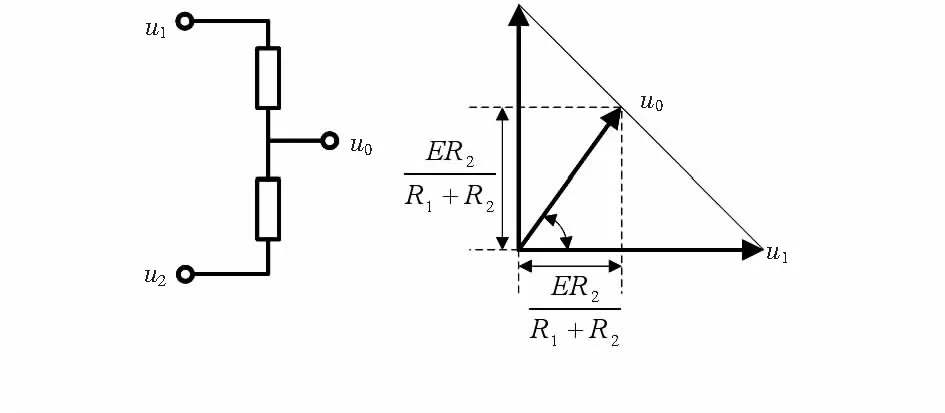

電阻鏈移相原理是將兩個(gè)不同的交變信號(hào)施加在電阻鏈兩端[5,6]。由于電壓合成的移相作用,在電阻鏈的各電阻插頭上將得到幅值和相位不同的一系列移相信號(hào)。本文將時(shí)柵動(dòng)測(cè)頭輸出的兩對(duì)正交信號(hào)施加在電阻鏈兩端[7~9],把動(dòng)測(cè)頭信號(hào)的非過(guò)零點(diǎn)通過(guò)移相轉(zhuǎn)換成為過(guò)零點(diǎn),然后利用整形輸出電路將移相后的信號(hào)整形為方波,與定測(cè)頭方波信號(hào)進(jìn)行比相,實(shí)現(xiàn)一個(gè)信號(hào)周期內(nèi)可以進(jìn)行多次測(cè)量的目的,這種方式在保證傳感器靈敏度和抗干擾能力的情況下,提高了傳感器的頻率響應(yīng),從而實(shí)現(xiàn)了高速測(cè)量。

設(shè)電阻鏈由電阻R1和R2串聯(lián)而成,電阻鏈兩端加有交流電壓u1=Esinωt和u2=Ecosωt。

應(yīng)用疊加原理求出電阻鏈節(jié)點(diǎn)處輸出電壓為

(2)

由圖3中矢量圖求得幅值和相位差為

(3)

(4)

輸出電壓可以表示為

uo=uomsin(ωt+θ).

(5)

根據(jù)圖3中矢量圖可知,通過(guò)改變R1和R2的比值,可以改變?chǔ)龋磳?shí)現(xiàn)了信號(hào)的移相,矢量uo的終點(diǎn)沿直線運(yùn)動(dòng),當(dāng)θ=45°時(shí),uom取最小值,第一象限的情況如此。電路兩端若接cosωt和-sinωt,可以得到第二象限各相輸出電壓;接-sinωt和-cosωt可以得到第三象限各相輸出電壓;接-cosωt和sinωt可以得到第四象限各相輸出電壓。因此,可以通過(guò)移相的方式將動(dòng)測(cè)頭信號(hào)的任意位置移動(dòng)到過(guò)零點(diǎn)來(lái)實(shí)現(xiàn)測(cè)量。

圖3 電阻鏈移相原理圖

3 系統(tǒng)設(shè)計(jì)

為了完成對(duì)信號(hào)的高性能實(shí)時(shí)性處理,采用SOPC技術(shù),利用硬件描述語(yǔ)言(Verilog HDL)進(jìn)行數(shù)字處理模塊的設(shè)計(jì)。動(dòng)測(cè)頭輸出的兩對(duì)差分信號(hào)經(jīng)電阻鏈移相轉(zhuǎn)換為32路信號(hào)輸出,為了不增加整形輸出電路的個(gè)數(shù),在硬件上,設(shè)計(jì)多路選擇電路,利用每路信號(hào)之間固有的相位差,對(duì)其分時(shí)輸出。在軟件上,設(shè)計(jì)Nios II軟核處理器內(nèi)主控程序?qū)Σ杉男盘?hào)進(jìn)行數(shù)據(jù)處理[10]。

3.1 硬件設(shè)計(jì)

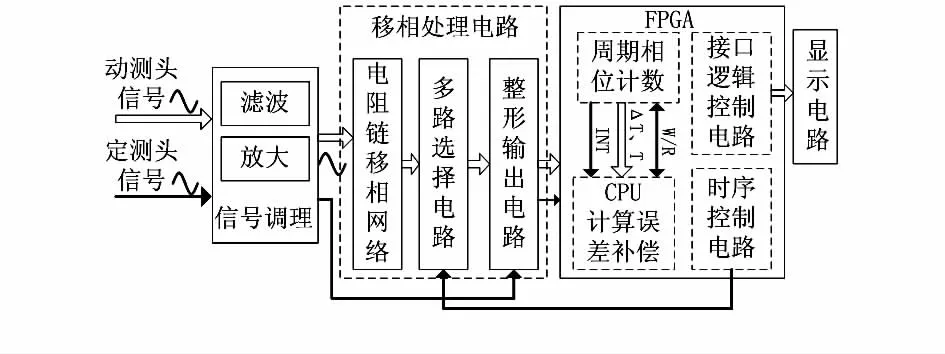

時(shí)柵位移傳感器信號(hào)處理系統(tǒng)框圖如圖4所示,該信號(hào)處理系統(tǒng)主要包括信號(hào)調(diào)理電路、電阻鏈移相網(wǎng)絡(luò)、多路選擇電路、整形電路、FPGA數(shù)字信號(hào)處理電路以及顯示電路。

動(dòng)、定測(cè)頭的感應(yīng)信號(hào)通過(guò)信號(hào)調(diào)理電路放大、濾波后,送入電阻鏈移相網(wǎng)絡(luò)進(jìn)行電壓合成移相。利用選擇器分時(shí)輸出移相后的動(dòng)測(cè)頭信號(hào),同時(shí)把選擇器輸出信號(hào)和調(diào)理后的定測(cè)頭信號(hào)分別送入整形輸出電路進(jìn)行處理,得到方波信號(hào)。將兩列方波信號(hào)送入FPGA,利用周期相位計(jì)數(shù)電路對(duì)兩列信號(hào)相位差和動(dòng)測(cè)頭信號(hào)的周期進(jìn)行高頻時(shí)鐘插補(bǔ),把所得到的計(jì)數(shù)值送入CPU進(jìn)行相位校正、數(shù)據(jù)處理和誤差補(bǔ)償,最終將結(jié)果送入數(shù)碼管顯示電路進(jìn)行顯示。

圖4 信號(hào)處理系統(tǒng)框圖

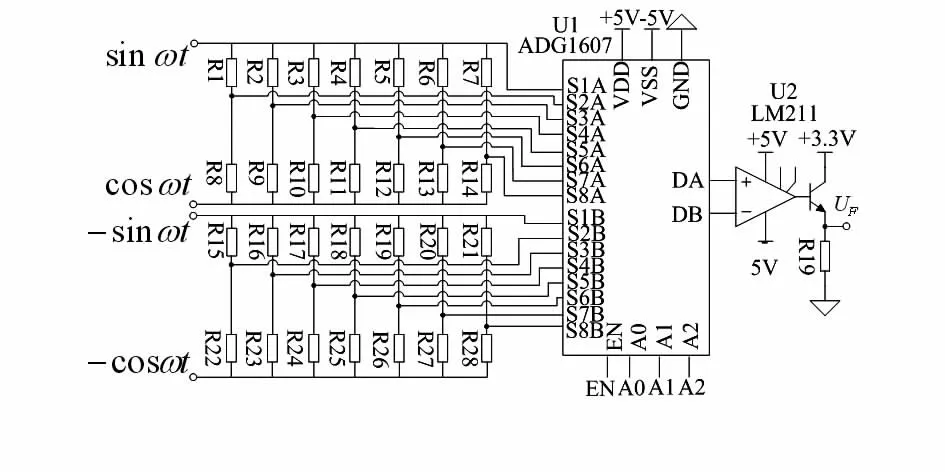

移相處理電路原理圖如圖5所示,電阻鏈移相網(wǎng)采用并聯(lián)的方式設(shè)計(jì),其優(yōu)點(diǎn)在于每個(gè)支路輸出信號(hào)的移相角只與該支路上兩個(gè)電阻的比值相關(guān),而不受其他支路電阻的影響,便于計(jì)算。將兩對(duì)時(shí)柵差分信號(hào)經(jīng)移相網(wǎng)絡(luò)移相后輸出32路信號(hào),相鄰兩路信號(hào)之間的相位差為11.25°。現(xiàn)以第一象限為例加以介紹,為抑制共模干擾,減小零點(diǎn)漂移,整形輸出電路采用差分輸入的接法。根據(jù)電阻鏈移相的原理可知,移相后第一象限的輸出信號(hào)和第三象限的輸出信號(hào)對(duì)應(yīng)正好構(gòu)成一對(duì)差分信號(hào),因此,利用差分多路模擬選擇器(ADG1607)將該差分信號(hào)分時(shí)輸出到整形輸出電路進(jìn)行轉(zhuǎn)換,得到一系列方波信號(hào)。多路選擇器的時(shí)序控制信號(hào)由FPGA的時(shí)序控制電路提供。

圖5 移相處理電路原理圖

3.2 軟件設(shè)計(jì)

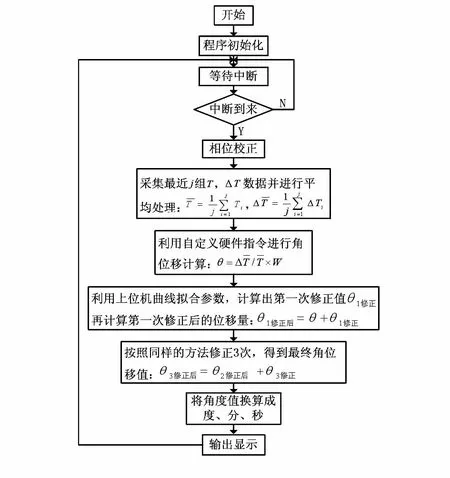

通過(guò)Eclipse集成開(kāi)發(fā)環(huán)境完成相關(guān)軟件程序設(shè)計(jì)。利用高頻時(shí)鐘插補(bǔ)電路對(duì)動(dòng)、定測(cè)頭正向過(guò)零點(diǎn)的時(shí)間差進(jìn)行時(shí)鐘插補(bǔ),將所得的計(jì)數(shù)值送入Nios II嵌入式軟核處理器,在CPU中計(jì)算當(dāng)前的角位移大小。因?yàn)榻?jīng)過(guò)移相后的信號(hào)與實(shí)際信號(hào)之間有一個(gè)固定的相位差,所以,在進(jìn)行角度計(jì)算之前要先對(duì)每路信號(hào)完成相應(yīng)的相位校正,得到真實(shí)的角位移值。為提高CPU的運(yùn)算速度,通過(guò)在Nios II指令系統(tǒng)中增加自定義指令,把復(fù)雜的標(biāo)準(zhǔn)指令序列中的乘法指令運(yùn)算轉(zhuǎn)換為一條用硬件實(shí)現(xiàn)的單個(gè)指令,以提高軟件處理的實(shí)時(shí)性[11]。利用諧波修正技術(shù)對(duì)角度誤差進(jìn)行修正[12],極大提高測(cè)量精度。系統(tǒng)軟件流程圖如圖6所示。

圖6 軟件設(shè)計(jì)流程圖

4 實(shí)驗(yàn)研究

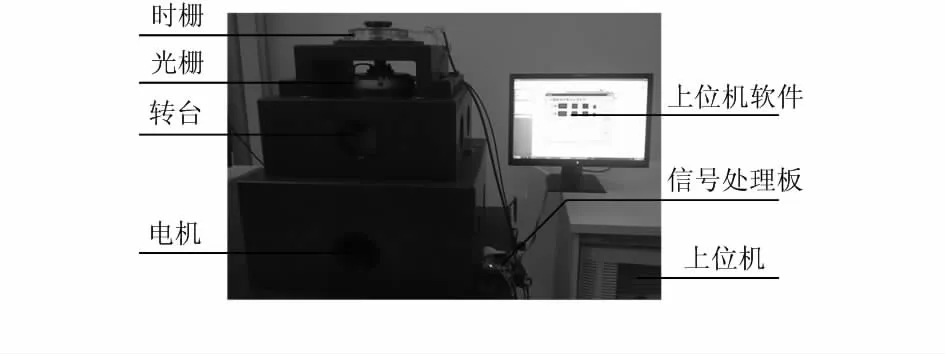

為驗(yàn)證設(shè)計(jì)的時(shí)柵信號(hào)處理系統(tǒng)的性能,對(duì)所研制的時(shí)柵信號(hào)處理板做如下實(shí)驗(yàn),實(shí)驗(yàn)平臺(tái)如圖7所示。

圖7 實(shí)驗(yàn)平臺(tái)

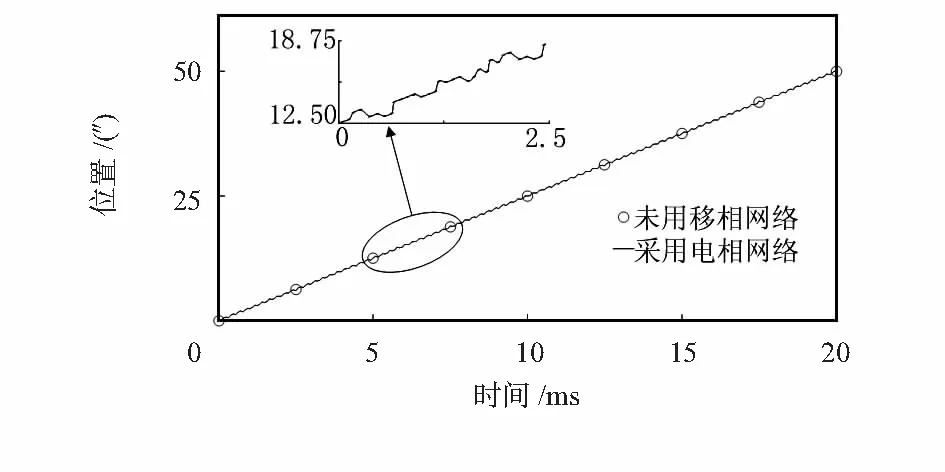

利用一元線性回歸對(duì)所采集的時(shí)柵數(shù)據(jù)進(jìn)行擬合,得到時(shí)柵傳感器頻率響應(yīng)曲線,如圖8所示。當(dāng)未使用電阻鏈網(wǎng)絡(luò)時(shí),依照時(shí)柵傳感器時(shí)間測(cè)量原理,在8個(gè)時(shí)間周期,即20 ms內(nèi),只能完成8次測(cè)量,得到8個(gè)采樣點(diǎn)。當(dāng)采用具有32路輸出的電阻鏈移相網(wǎng)絡(luò)之后,在相同8個(gè)時(shí)間周期可以完成256次測(cè)量,得到256個(gè)采樣點(diǎn)。采樣頻率從之前的400 Hz增加到12.8 kHz,實(shí)現(xiàn)高速測(cè)量。圖8中小圖表示1個(gè)時(shí)間周期內(nèi),因測(cè)量點(diǎn)數(shù)增多所反映的時(shí)柵角位移細(xì)節(jié)變化情況。從圖中明顯看出:因傳感器頻率響應(yīng)的提高,得到更加精確的時(shí)柵角位移變化曲線。

圖8 頻率響應(yīng)曲線圖

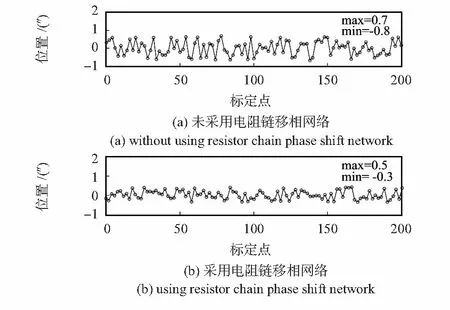

對(duì)比實(shí)驗(yàn)以高精度的Heidenhain 圓光柵(精度為±1″)作為基準(zhǔn),以分度轉(zhuǎn)臺(tái)作為測(cè)量對(duì)象。光柵與時(shí)柵同軸安裝,轉(zhuǎn)臺(tái)轉(zhuǎn)動(dòng)的同時(shí),時(shí)柵和光柵進(jìn)行同步采樣,兩者測(cè)量值之差即為誤差值。圖9為72對(duì)極的時(shí)柵位移傳感器對(duì)極內(nèi)的誤差曲線。從圖中可以看出:采用電阻鏈移相網(wǎng)絡(luò)后時(shí)柵對(duì)極內(nèi)的誤差峰—峰值由之前的1.5″降低為0.8″,實(shí)現(xiàn)高精度測(cè)量。

圖9 誤差曲線圖

5 結(jié)束語(yǔ)

通過(guò)采用電阻鏈移相網(wǎng)絡(luò)提高了時(shí)柵位移傳感器的頻率響應(yīng),實(shí)現(xiàn)高速測(cè)量。利用多路選擇電路解決了整形輸出電路的冗余問(wèn)題,在節(jié)約系統(tǒng)成本的同時(shí),也實(shí)現(xiàn)了系統(tǒng)的小型化設(shè)計(jì)。基于SOPC技術(shù)定制符合需求的專(zhuān)用Nios II軟核處理器對(duì)時(shí)柵信號(hào)進(jìn)行處理,系統(tǒng)僅集成在一片高性能的FPGA上,即簡(jiǎn)化了電路的結(jié)構(gòu)設(shè)計(jì),降低系統(tǒng)功耗,又提高了傳感器的動(dòng)態(tài)性和實(shí)時(shí)性。實(shí)驗(yàn)結(jié)果表明:該方法大幅度提高了現(xiàn)階段時(shí)柵位移傳感器的頻率響應(yīng),同時(shí)使測(cè)量誤差減小近1倍,峰—峰值僅為0.8″。

[1] 彭東林,張興紅,劉小康.場(chǎng)時(shí)時(shí)柵位移傳感器研究[J].儀器儀表學(xué)報(bào),2003,24(3):321-323.

[2] 彭東林,陳錫侯,朱 革,等.時(shí)柵的波動(dòng)方程分析和行波形成新辦法[J].機(jī)械工程學(xué)報(bào),2006,42(11):113-115.

[3] 湯其富,彭東林,武 亮,等.時(shí)柵角位移傳感器中的多普勒效應(yīng)影響及其抑制方法研究[J].儀器儀表學(xué)報(bào),2014,35(3):620-626.

[4] 彭東林,劉小康,譚為民.時(shí)空坐標(biāo)轉(zhuǎn)換理論與時(shí)柵位移傳感器研究[J].儀器儀表學(xué)報(bào),2002,21(4):338-342.

[5] 強(qiáng)錫富.傳感器[M].3版.北京:機(jī)械工業(yè)出版社,2001:188-194.

[6] 于 耕,馬曉梅,郭華鵬.圓光柵測(cè)角系統(tǒng)信號(hào)細(xì)分電路設(shè)計(jì)[J].電子設(shè)計(jì)工程,2012,20(15):99-102.

[7] Tan K K,Zhou H X,Lee T H.New interpolation method for quadrature encoder signals[J]. IEEE Transactions on Instrumentation and Measurement,2002,51(5):1073-1079.

[8] 楊繼森,許 強(qiáng),馮濟(jì)琴.基于STM32F4 的時(shí)柵位移傳感器信號(hào)處理系統(tǒng)集成化設(shè)計(jì)[J].傳感器與微系統(tǒng),2013,32(12):113-116.

[9] Birch K P.Optical fringe subdivision with nanometric accura-cy[J].Precision Engineering,1990,12(4):195-198.

[10] 蔣麗雁.基于FPGA的光柵信號(hào)處理電路設(shè)計(jì)[J].工具技術(shù),2010,44(5):100-102.

[11] 鄭方燕.基于SOPC的時(shí)柵位移傳感器信號(hào)處理系統(tǒng)設(shè)計(jì)[J].傳感技術(shù)學(xué)報(bào),2012,25(10):1429-1432.

[12] 高忠華,陳錫侯,楊繼森,等.直線時(shí)柵傳感器全誤差模型與誤差修正方法研究[J].傳感器與微系統(tǒng),2012,31(8):87-89.

陳錫侯,通訊作者,E—mail:cxh0458@163.com。

Study on method for time-grating high-speed measurement =based on phase-shifting of resistance chains*

SUO Long-bo, CHEN Xi-hou, GOU Li, ZHANG Tian-heng, CAO Huan

(Engineering Research Center of Mechanical Testing Technology and Equipment,Ministry of Education,Chongqing Key Laboratory of Time-Grating Sensing and Advanced Testing Technology,Chongqing University of Technology,Chongqing 400054,China)

Aiming at the problem that measuring rate of time-grating displacement sensor is affected due to slow frequency response,,a method combining data processing and phase-shifting of resistance chains is proposed.The output signal of time-grating is phase-shifting processed by resistance chains and timeshare output by multiplexers and shaping output circuit,and the SOPC technology is used for data processing and error compensation .Experimental results show that the original sampling frequency of 400 Hz can be improved up to 1.28 kHz,which can substantially increase the frequency response of the time-grating displacement sensor ,and high-speed real-time measurement is achieved.Meanwhile the random error is effectively reduced,the peak-peak value of error is decreased from 1.5″ to 0.8″ within antipode,and the measurement precision is nearly double improved.

time-grating; resistor chain; multiplexers; SOPC

2015—01—12

國(guó)家高科技研究發(fā)展計(jì)劃(“863”計(jì)劃)資助項(xiàng)目 (2012AA041202)

10.13873/J.1000—9787(2015)09—0051—04

TP 206

A

1000—9787(2015)09—0051—04

索龍博(1988-),男,陜西寶雞人,碩士研究生,主要研究方向?yàn)橛?jì)算機(jī)輔助測(cè)試技術(shù)與儀器。