寬帶正交基帶信號的采樣與存儲技術

路 延

(陜西職業技術學院,710100)

0 引言

寬帶正交基帶信號是數字偵察接收機和數字射頻存儲(DRFM)干擾技術中常用到的信號形式,本文來源于雷達偵察信號處理機和干擾機的一部分,本文屬于雷達偵察信號處理機中系統硬件設計部分—寬帶正交基帶信號的采樣和存儲技術設計,也可以用作DRFM干擾機的一部分。

在了解寬帶正交基帶信號采集基本原理的基礎上,設計了一個對其進行采集和存儲的全數字化系統。根據寬帶正交基帶信號的特點,選擇了ADC與FPGA結合的方案。設計采用的ADC是Atmel公司生產的AT84AD001B,在交錯模式下,采樣速率達到750Msps。選用LVDS邏輯作為ADC與FPGA高速數據接口邏輯電平,選用LVTTL邏輯作為FPGA外圍電路接口邏輯電平。FPGA選擇Altera公司的StratixII系列的EP2S90F780C4。

1 信號接收的全數字化設計

1.1 利用ADC與FPGA實現的數據采集與存儲系統

整個系統是通過FPGA對ADC的三線串行接口進行設置,使得ADC按照設置的工作方式進行工作,采樣得到的數據通過I、Q兩路傳輸到FPGA,FPGA內部的LVDS模塊進行接收和降速,再通過FIFO模塊緩沖存儲數據,最后將數據存儲到較低時鐘頻率的雙端口RAM中。FPGA的配置方式選擇了JTAG+AS的方案。

1.2 FPGA內部邏輯功能

FPGA內部具有多個模塊協調工作,來控制ADC,對ADC采樣的數據進行接收和降速存儲等。ADC轉化完的375M的2路數據(共16bit),在同步時鐘的觸發下,送進FPGA,FPGA通過內部專門的差分接收模塊對數據進行接收和降速,使其成為64bit并行數據,經過FPGA內部設計通過一個FIFO模塊進行數據緩沖存儲,最后存儲到雙端口RAM中。

2 高速ADC的電路設計

2.1 ATA84AD001B的三線串行接口的配置和電路設計

三線串行接口采用SPI(高速串行接口)協議來進行配置的接口。其AT84AD001B的三線串行接口對應著8個16bit的內部寄存器,通過sdata接口寫入19bit的數據。這個寫過程由sclk端口的時鐘上升沿決定,sldn和sdata只在時鐘的上升沿被采樣。

當寫過程結束時,sldn必須被設置成1,當再次啟動時至少需要一個時鐘上升沿。所以在連續設置三線串行接口時,每一個設置過程至少需要21個時鐘周期。

ADC默認為采用常規設置:雙通道可用,一個時鐘I,0dB增益,1:1多路選擇器模式,二進制輸出,批量測試模式關閉,數據準備為Fs/2,內部設置調整為0ps,精確采樣延時調整為0ps等。當Mode管腳被設置成1(2.25V)時,表示三線串行接口處于活動狀態,此時三線串行接口內部寄存器可通過地址進行設置。

本系統采用的是利用FPGA的控制程序,使用FPGA的4個管腳去配置ADC的三線串行接口。這種設計下,需要在FPGA的管腳與ADC的三線串行接口之間加入50?的電阻來緩沖數據。

2.2 AT84AD001B的外圍電路設計

AT84AD001B的模擬輸入采用的是差分模式,它的模擬輸入被設計成雙焊盤輸入,其中一個焊盤直接連接模擬信號,另外一個焊盤應該通過一個50?的電阻接地。

AT84AD001B在本系統采用的為差分輸入方式,輸入的時鐘為差分時鐘。ADC為I路和Q路分別提供了輸入管腳,每路的輸入管腳正反兩端必須連接一個100nF的交流耦合電容。

ADC的電源供需要添加一些旁路電路、去耦電路和接地電路。其中VCCD、VCCA和VCCO的旁路電路和接地電路需要注意的是1uF和100pF的旁路電容必須接近板連接器。

3 基于FPGA三線串行接口控制、數據接收和存儲設計

3.1 利用FPGA對ADC采樣得到的數據進行接收和降速

由于ADC的采樣數據速率較高容易產生噪聲干擾而導致誤碼,故采用LVDS接口標準來作為ADC到FPGA的數據通道。

本系統的數據接收FPGA采用的是EP2S90F780C4,器件本身支持LVDS邏輯接口,可以實現最高1GHz數據的收發,在QuartusII軟件進行設計時,可以通過采用Megafunction模塊來設計LVDS的收發模塊。本系統通過LVDS接收模塊對數據接收降速,最后通過一個發送模塊將數據以LVDS邏輯發送出去。

本系統ADC輸出的采樣數據共16bit,分為IQ兩路進行傳輸,故使用兩個LVDS接收模塊來進行接收,每一個接收模塊接收8bit數據,然后數據進行降速4倍的處理。分配管腳時,將通道I的8bit數據分配到FPGA左側的BANK6,將通道Q的8bit數據分配到FPGA左側的BANK5,FPGA只需要一路時鐘,而ADC只輸出了I路時鐘,則可以直接將差分的I 路時鐘輸入到左側的BANK。

一路LVDS時鐘信號,數據的傳輸速率為375MHz,時鐘頻率為187.5MHz。利用Megafunction模塊設計出的LVDS模塊可以實現數據的接收并降速4倍,通過兩個LVDS降速模塊,將16bit 375MHz的數據轉換成64bit、3.75MHz的數據。

3.2 數據存儲

ADC采樣完的375M的兩路數據(16bit),在經FPGA接收和降速模塊處理后,成為93.75M的64bit并行數據,經過FPGA內部設計的64bit寬度的FIFO模塊,使得數據進行緩沖,以匹配LVDS模塊輸出數據與RAM存儲模塊的速率。RAM存儲模塊采用的雙端口設計,以滿足以后對數據的讀取。

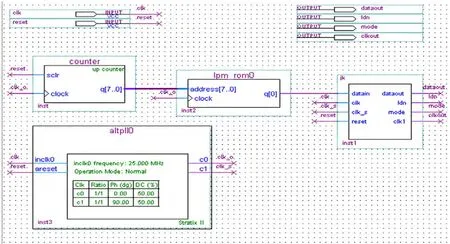

圖1 ADC三線串行接口配置模塊設計

信號經FIFO模塊緩沖后經模塊KZ分路,產生讀使能、讀時鐘信號和數據長度,控制FIFO的讀取,然后時鐘經過一個計數器產生地址,供后續RAM寫入數據提供地址。

3.3 FPGA內的三線串行接口配置模塊的設計

本系統的設計將配置三線串口的數據存儲在ROM中,然后通過對ROM的讀取來將配置數據逐位輸出,對ROM輸出的數據有一個起始位檢測,將起始位后的數據每19位為一組數據,讀取完19位數據后需要兩個時鐘周期來將數據讀入ADC的寄存器和為開始下一個周期做準備。為了驗證配置模塊的功能正確性,用QuartusII軟件建立模塊工程如圖1所示。波形仿真圖如圖2所示。

4 結論

本系統利用高速ADC和高性能FPGA實現了對寬帶正交基帶信號的數字化采樣和存儲的設計。通過仿真驗證了系統的可行性。針對這個系統,本文主要研究了其ADC電路及數據存儲的設計部分,具體如下:

在分析寬帶正交基帶信號的各項指標情況下對ADC進行選型并得到AT84AD001B滿足條件。AT84AD001B具有多種工作模式,本系統選擇了其中一種工作模式,使得采樣率能夠滿足設計要求的750MHz/8bit。AT84AD001B具有三線串行接口功能,能方便的利用FPGA對ADC進行配置。

在分析對AT84AD001B采樣得到的數據進行降速和存儲的基礎上,本系統選擇了StratixII系列的EP2S90F780C4作為ADC采樣數據的處理器件。

[1]Atmel Corporation.Dual 8-bit 1 Gsps ADC AT84AD001B Smart ADC.2004:36~42

[2]Atmel Corporation.AT84AD001B-EB Evaluation Kit User Guide.2004:35~49

[3]Altera Corporation.PLL&Timing Glossary.2002:1~11

[4]Altera Corporation.Config_handbook.2004:23~119

[5]Altera Corporation.My First FPGA Design Tutorial.2004:1~44