一種高速數(shù)據(jù)接口的設計方法*

章 睿,楊瑞瑞,張文沛

0 引言

隨著數(shù)字通信業(yè)務的蓬勃發(fā)展導致通信系統(tǒng)對傳輸帶寬提出了更高的挑戰(zhàn),例如10 Gb/s高速并行接口在光纖通信、數(shù)據(jù)交換、網(wǎng)絡通信等方面有著廣泛的應用。目前主流元器件解決方案中,主要采用高速串行接口(SerDes)實現(xiàn)高速接口,但SerDes接口工作頻率高、設計復雜、價格昂貴。文中設計了一種高速并行差分接口方式,利用國內(nèi)流片廠商IP,結合自行設計的控制和同步邏輯,可以實現(xiàn)雙向10 Gb/s數(shù)據(jù)接口,滿足高速接口的國產(chǎn)化需求。

1 簡介

高速并行傳輸?shù)钠款i之一是對數(shù)據(jù)的有效恢復,數(shù)據(jù)恢復中主要存在兩個問題:一是當單線傳輸速率越來越快時,相應的每位數(shù)據(jù)所占的時間窗口不斷減小,導致時鐘很難在數(shù)據(jù)的有效窗口準確采樣;二是由于并行傳輸?shù)母鳁l數(shù)據(jù)路徑延遲不同,導致接收端無法有效的同步接收并行傳輸?shù)母髀窋?shù)據(jù)。

文中描述一種基于數(shù)字的高速并行數(shù)據(jù)恢復和同步的設計方法,通過對訓練數(shù)據(jù)采樣時鐘相位的計算反饋輸出到DLL鎖相環(huán)從而改變時鐘的采樣相位,使時鐘采樣發(fā)生在數(shù)據(jù)有效窗口的中央,因此能夠保證時鐘、數(shù)據(jù)在外界溫度、濕度和干擾等情況下正確地采樣和恢復出數(shù)據(jù)。

2 系統(tǒng)結構

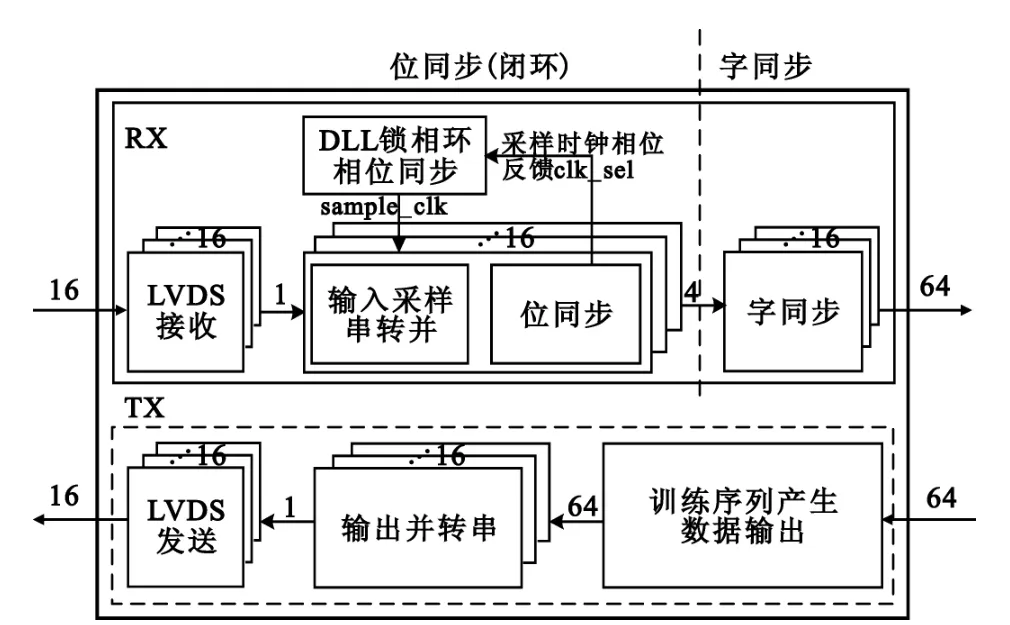

系統(tǒng)結構如圖1所示,其包括接收RX與發(fā)送TX兩個獨立部分。

圖1 系統(tǒng)結構框Fig.1 System structure

接收部分包括每個通道的低電壓差分信號(LVDS)接收電路[1],每個通道的接收串行轉并行電路,每個通道的數(shù)據(jù)采樣時鐘相位計算和調(diào)整模塊以及所有通道的字同步模塊。其中采樣時鐘相位調(diào)整模塊包括一個DLL鎖相環(huán)和每個通道對應的時鐘相位調(diào)整無毛刺選擇電路MUX。

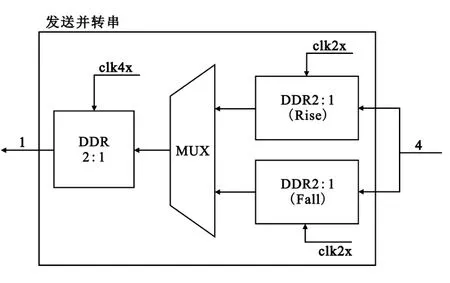

發(fā)送部分包括訓練序列產(chǎn)生器[2]和數(shù)據(jù)輸出,每個通道的并行轉串行電路,每個通道的低電壓差分信號(LVDS)發(fā)送電路,見圖2。

發(fā)送部分的電路設計比較簡單,控制好640 MHz、320 MHz、160 MHz這三組時鐘的相位關系[3],保證64位并行數(shù)據(jù)通過兩次并串轉換壓縮到16位并行數(shù)據(jù),從160 MHz時鐘域逐級進入320 MHz時鐘域、640 MHz時鐘域,最終數(shù)據(jù)以DDR方式伴隨320 MHz隨路時鐘輸出。

圖2 并串轉換電路Fig.2 P-to-Scircuit

下文重點介紹數(shù)據(jù)接收部分電路的設計。

3 輸入電路

3. 1 串轉并電路

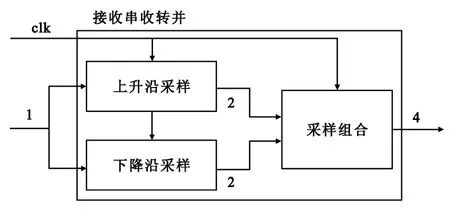

在10G高速并行接收電路中,以16對低電壓差分信號(LVDS)差分對接收10G并行數(shù)據(jù)流[4]。每對LVDS管腳通道的數(shù)據(jù)為雙沿串行數(shù)據(jù)(DDR),隨路時鐘320 MHz,經(jīng)過圖3描述的串并轉換電路后轉換為4位并行數(shù)據(jù),并降頻進入160 MHz時鐘域。

圖3 串并轉換電路Fig.3 S-to-P circuit

如圖3所示,串行數(shù)據(jù)流進入串并轉換電路后,同時接入一個上升沿采樣寄存器和一個下降沿采樣寄存器[5],采樣時鐘320 MHz。然后對采樣后的數(shù)據(jù)進行組合,由下一級160 MHz時鐘將4 bit的并行數(shù)據(jù)輸出。

3. 2 相位同步電路

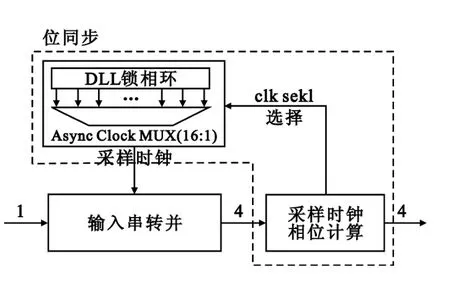

圖4為采樣時鐘相位同步電路框圖,包括一個采樣時鐘相位計算模塊和一個由DLL與異步無毛刺時鐘切換MUX組成的時鐘相位調(diào)整模塊。

DLL可以對每個數(shù)據(jù)通道的采樣時鐘進行1/16精度的相位調(diào)整,每個通道每次調(diào)整的相位由相位計算模塊對采樣數(shù)據(jù)進行處理后反饋給相位調(diào)整模塊。在高速并行接口正常工作前,發(fā)送端與接收端首先發(fā)送多組訓練數(shù)據(jù),選擇與每個通道數(shù)據(jù)相位匹配的時鐘信號。

圖4 相位同步電路Fig.4 Phase synchronization circuit

高速并行接口正常工作之前,外部器件首先按照約定的方式發(fā)送訓練數(shù)據(jù)“0000_0000_0000_0000_0011_1111_1111_1111_1111”,重復發(fā)送多次訓練數(shù)據(jù)。

接收端將串行數(shù)據(jù)轉為并行4位數(shù)據(jù)進行處理,其過程如下:

1)首先通過相位計算電路搜索出串行數(shù)據(jù)電平的變化沿即對4為數(shù)據(jù)進行異或,如以“0001”為例得到右邊沿“001”。

2)然后每次對采樣時鐘相位加1/16,即選擇DLL的一個相鄰輸出,直到數(shù)據(jù)沿變化為“010”的中間沿,此時記下移相次數(shù)counter1。

3)重復上述移相過程直到得到左邊沿“100”,同樣記下移相次數(shù)counter2。

4)最終計算出采樣時鐘移相位(counter1+counter2)/2。

3. 3 字同步電路

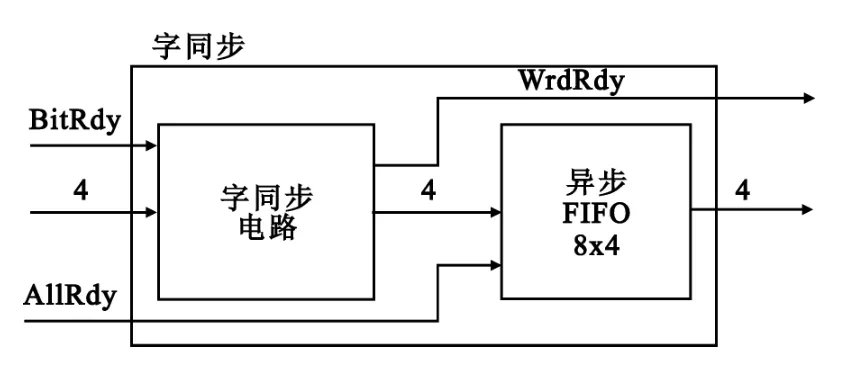

圖5為并行數(shù)據(jù)字同步框圖,包括一個移位計算模塊和一個基于流處理的異步FIFO。

每個通道數(shù)據(jù)相位調(diào)整完成后給出BitRdy信號,字同步模塊即可以對數(shù)據(jù)進行處理。字同步同樣會用到訓練數(shù)據(jù)的跳變沿,且以“0011”為同步字,例如,當接收到并行數(shù)據(jù)是“0001”時則移位計算模塊會將數(shù)據(jù)向左移一位。

當每個通道都計算出移位數(shù)后會產(chǎn)生WrdRdy,將所有通道的WrdRdy作邏輯與處理得到AllRdy信號,如圖5所示。

圖5 字同步電路Fig.5 Word synchronization circuit

當AllRdy有效且同步字到來時將數(shù)據(jù)存入到異步FIFO中,對于異步FIFO的讀信號則在AllRdy有效至少一個周期同時在將FIFO寫滿之前有效,因此理論上本字同步方法能夠糾正的周期偏差在于FIFO深度,即將FIFO寫滿的周期數(shù)。

4 仿真結果分析

采用文中設計的高速接口方法,在中芯國際(SMIC)的0.13μm工藝上,已經(jīng)設計實現(xiàn)了雙向10 Gb/s傳輸速率的高速接口芯片。

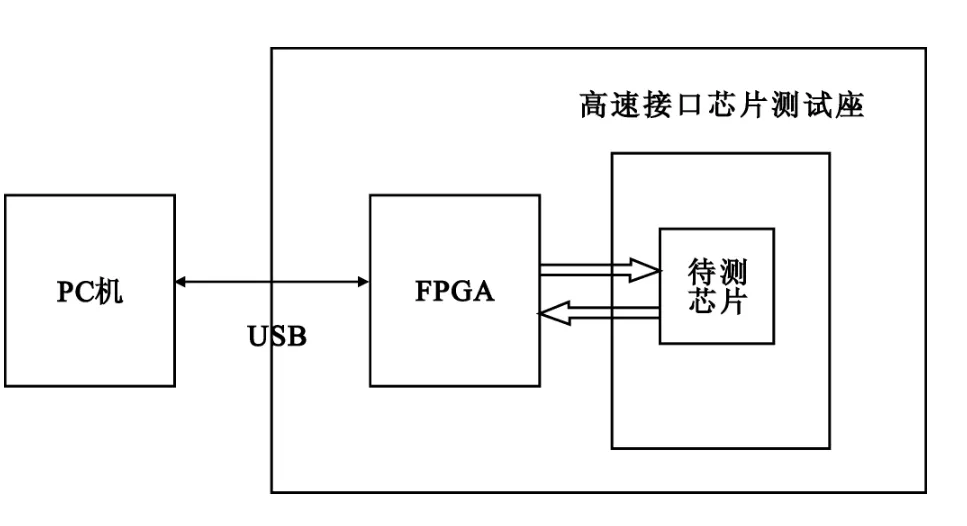

為驗證文中設計的高速接口方法的正確性,設計了高速接口芯片專用測試板,如圖6所示。

圖6 測試板框Fig.6 Test circuit diagram

1)用FPGA對接所設計的高速接口芯片。

2)用PC機通過USB接口,與FPGA通信。

3)由FPGA發(fā)起數(shù)據(jù)傳輸,將內(nèi)置于FPGA內(nèi)的待處理數(shù)據(jù),分成大數(shù)據(jù)包,通過FPGA發(fā)送給高速接口芯片的10G數(shù)據(jù)接收口(其中數(shù)據(jù)總線16位,時鐘320 MHz,DDR采樣方式,傳輸帶寬達10 240 Mb/s,即10.24 Gb/s,超過了10 G光纖信道接口規(guī)范要求的10 Gb/s)。

4)高速接口芯片接收到FPGA發(fā)送的數(shù)據(jù)后,進行算法運算處理。

5)運算結果通過高速接口芯片的10 G數(shù)據(jù)發(fā)送口輸出給FPGA。

6)FPGA接收高速接口芯片發(fā)送的運算結果,與FPGA內(nèi)置的理想結果對比,如一致則證明在傳輸過程中沒有發(fā)生數(shù)據(jù)錯誤。

7)因數(shù)據(jù)量較大,循環(huán)使用FPGA內(nèi)置的數(shù)據(jù)來實現(xiàn)接口上的大數(shù)據(jù)量傳輸。

8)一旦有一個數(shù)據(jù)包發(fā)生數(shù)據(jù)錯誤,F(xiàn)PGA將出錯信息通過USB接口發(fā)給PC機報警。

經(jīng)48小時實際測試,高速接口芯片連續(xù)傳輸數(shù)據(jù)無錯誤產(chǎn)生。

該設計方法已用于某款“核高基”高速芯片,該芯片經(jīng)過第三方測試機構測試證明接口性能超過雙向10 Gb/s,并以成功應用于10 G SDH光纖信道設備。

5 結語

文中首次公開披露利用國內(nèi)流片廠商IP,結合自行設計的控制和同步邏輯,可以實現(xiàn)雙向10 Gb/s數(shù)據(jù)接口的方法。

文中研究內(nèi)容基礎上,今后將通過擴展數(shù)據(jù)位寬、提高接口隨路時鐘頻率等方法,進一步提升接口帶寬,實現(xiàn)10 Gb/s以上,甚至40 Gb/s的高速數(shù)據(jù)接口。

[1] IEEE1596.3 ,1996[S].USA:IEEE.

[2] WAKERLY J F.Digital Design:Principles and Practices[M].Third Edition.NJ,USA:Prentice-Hall,2000.

[3] 陳春章,艾霞,王國雄.數(shù)字集成電路物理設計[M].北京:科學出版社,2008:60.

CHEN Chun-zhang,AI Xia,WANG Guo-xiong.Digital Integrated Circuit Design[M].Beijing:Science Press,2008:60.

[4] 唐杉,徐強,王莉薇.數(shù)字IC設計-方法、技巧與實踐[M].北京:機械工業(yè)出版社,2006:50.

TANG Shan,XU Qiang,WANG Li- wei.Method,the Design of Digital ICSkills and Practice[M].Beijing:Machinery Industry Press,2006:50.

[5] 王彬,任艷穎.數(shù)字IC系統(tǒng)設計[M].西安:西安電子科技大學出版社,2005:22.

WANG Bin,REN Yan-ying.Digital IC System Design[M].Xi'an:Xi'an Electronic and Science University press,2005:22.