基于VPX平臺的數(shù)字波束形成實現(xiàn)

吳 衛(wèi),章文星

(中國船舶重工集團公司第七二四研究所,南京211153)

基于VPX平臺的數(shù)字波束形成實現(xiàn)

吳 衛(wèi),章文星

(中國船舶重工集團公司第七二四研究所,南京211153)

數(shù)字波束形成一直是雷達和通信工程中的關鍵技術。本文對數(shù)字波束形成原理作了簡單的介紹,并在基于VPX開發(fā)平臺上進行了數(shù)字波束形成的硬件實現(xiàn)。

數(shù)字波束形成;VPX;FPGA

0 引 言

隨著作為雷達觀測對象的各種飛行器性能的不斷提高、雷達工作環(huán)境的不斷惡化以及雷達應完成任務的增多,對雷達的發(fā)展提出了新的要求。老體制雷達已經(jīng)無法適應時代的發(fā)展規(guī)律,必須要發(fā)展新體制雷達,而波束形成技術在這種情況下被提出來。傳統(tǒng)的波束形成無論是在高頻還是在中頻實現(xiàn)都是硬件的模擬方法。這種方法的設備量大,硬件復雜,波束指向不易改動。數(shù)字波束形成(Digtal Beam Forming,DBF)是在原來模擬波束形成原理的基礎上引入數(shù)字信號處理方法后建立起來的一門雷達新技術。這種技術充分利用了陣列天線所檢測到的空間信息,可以方便地獲得超分辨和低副瓣的性能,實現(xiàn)波束掃描、自校準和自適應波束形成等。DBF技術的成功應用必將對現(xiàn)代雷達技術的發(fā)展產(chǎn)生重大影響。本文充分利用FPGA資源豐富、處理靈活的優(yōu)勢,在基于VPX開發(fā)平臺上進行了DBF的硬件設計實現(xiàn)。

1 DBF的基本原理

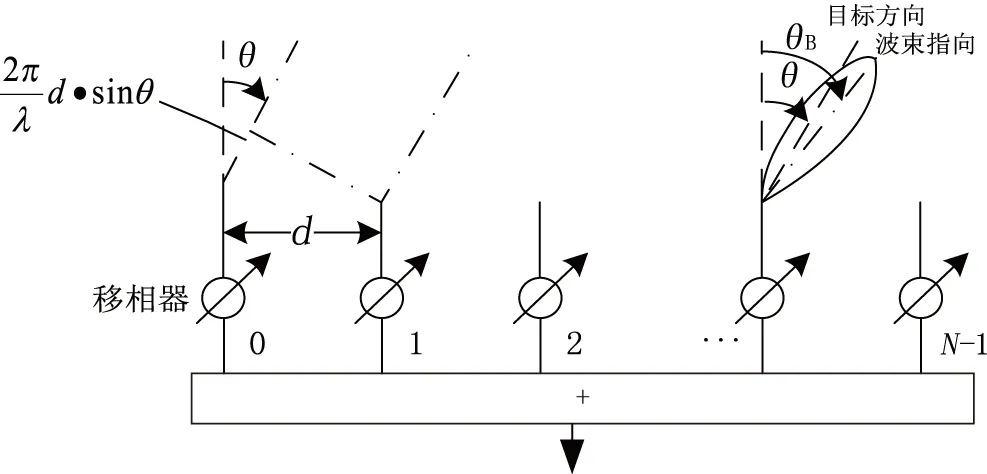

數(shù)字波束形成就是用數(shù)字處理方法, 對于某一方向入射信號, 補償由于天線單元在空間位置不同帶來的電磁波傳播路程差而導致的通道間相位差, 實現(xiàn)信號同相疊加, 從而實現(xiàn)該方向的最大能量接收。傳統(tǒng)的模擬波束形成過程是在中頻載波或射頻載波上對各陣元信號進行移相和模擬合成,而數(shù)字波束形成則采用數(shù)字電路實現(xiàn)這個模擬過程。圖1為簡化的線陣示意圖。

圖1 N單元陣列圖

這里對數(shù)字波束形成的實現(xiàn)過程作一簡單的理論推導。圖1 所示的線陣單元之間的“空間相位差△φ”與“陣內(nèi)相位差△φB”分別為

(1)

(2)

在用數(shù)字方法形成接收波束時,△φB按預定的波束指向θB由計算機或數(shù)字信號處理機提供。對于第i單元,在某時刻的接收信號為

Ii=ai0cos[△φ0+i△φ]

(3)

Qi=ai0sin[△φ0+i△φ]

(4)

式中,△φ0為回波信號與本振信號的相位差,ai0為各單元的幅度信息。

如果要形成多個波束,每個波束指向不同,設第K個波束指向為θBK,則應提供的陣內(nèi)相位補償值應為△φBK:

(5)

進行相位補償后,I,Q路信號輸出為

Ii′=ai0cos[△φ0+i△φ-i△φBK]

(6)

Qi′=ai0sin[△φ0+i△φ-i△φBK]

(7)

由式(3)、(4)、(6)和(7)可得下式:

Ii′=Iicos(i△φBK)+Qisin(i△φBK)

(8)

Qi′=-Iisin(i△φBK)+Qicos(i△φBK)

(9)

將式(8)和(9)寫成矩陣形式為:

(10)

因此,由上文的推導可以看出,作一次矩陣變換、4次實數(shù)乘法與2次加法即可完成一個相位補償。

在線陣單元波束掃描范圍內(nèi),線陣天線方向函數(shù)F(θ)可表示為

(11)

2 硬件實現(xiàn)

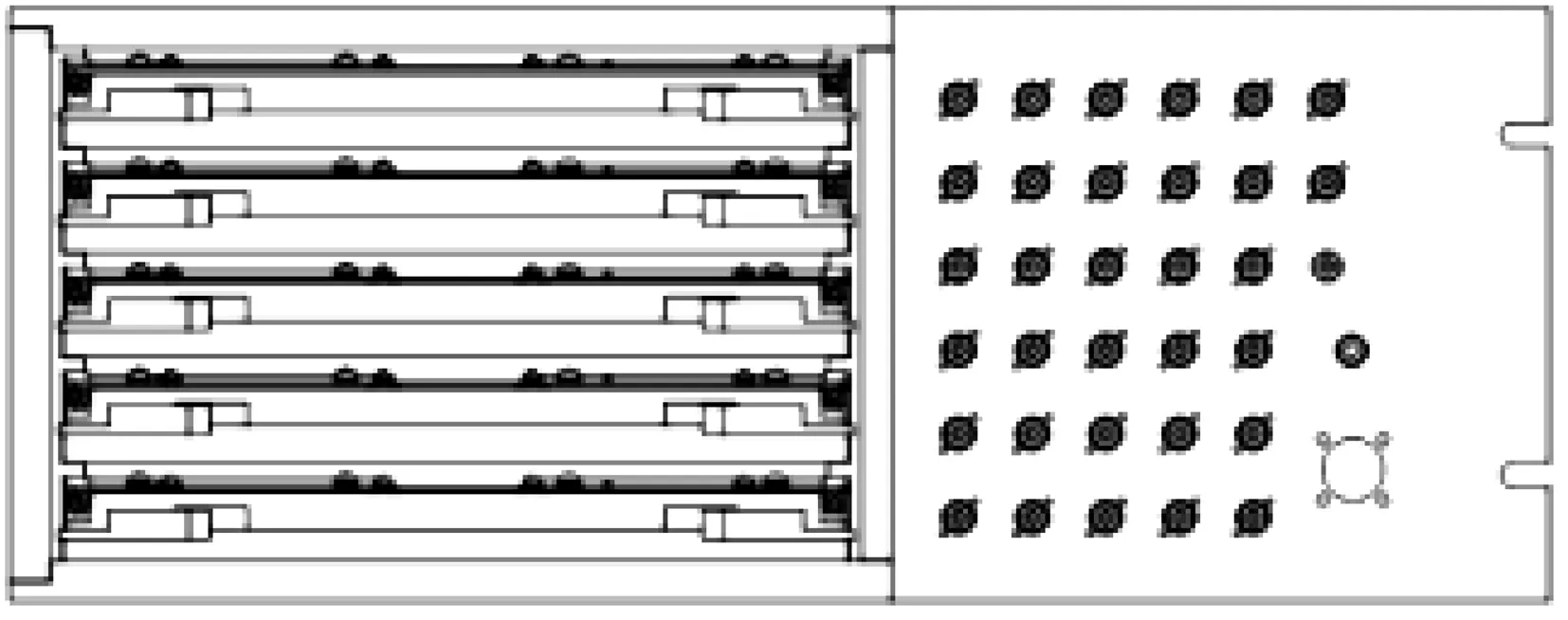

數(shù)字波束形成的硬件部分主要由基于FPGA芯片的VPX平臺實現(xiàn)。硬件平臺前視圖如圖2所示。

圖2 硬件平臺前視圖

5塊VPX板卡水平放置,由上到下依次是PowerPC處理板、光纖接口板、FPGA信號處理板0、FPGA信號處理板1和FPGA信號處理板2。

FPGA信號處理板是基于XILINX公司VIRTEX5系列FPGA信號處理芯片的高性能高速信號處理板,在VPX硬件平臺中總共有3塊。該板采用6片XC5VSX95T FPGA芯片,可以接受光纖板輸出接口的數(shù)據(jù),可以對信號進行板內(nèi)緩存、大規(guī)模的預處理算法的實現(xiàn)、實時數(shù)據(jù)的發(fā)送等功能。

光纖接口板是基于AVAGO公司QSFP光電轉(zhuǎn)換模塊的接口板卡。該板采用9個QSFP光電轉(zhuǎn)換模塊,實現(xiàn)電信號與光信號的轉(zhuǎn)換。本系統(tǒng)中用8個QSFP模塊實現(xiàn)單向數(shù)據(jù)接收,1個QSFP模塊實現(xiàn)單向數(shù)據(jù)發(fā)送。

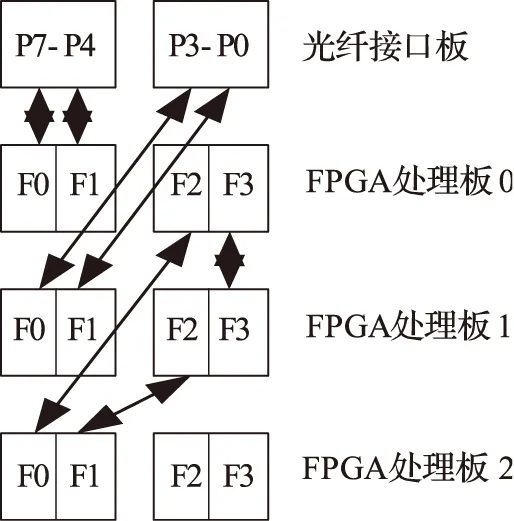

各個FPGA信號處理板同光纖接口板之間的互連關系如圖3所示。光纖接口板上載有1片XC5VLX50T以及9個AVAGO公司QSFP光電轉(zhuǎn)換模塊,其中一個QSFP模塊直接連接到XC5VLX50T上,其余8個QSFP模塊通過光纖接口板的P2和P3槽連到FPGA信號處理板0及FPGA信號處理板1上。3塊FPGA信號處理板上各載有6片XC5VSX95T FPGA芯片,分別標記為FPGA0到FPGA5,其中FPGA0和FPGA1接收來自光纖處理板上8個QSFP模塊通過GTP協(xié)議送入的數(shù)據(jù),F(xiàn)PGA2和FPGA3主要實現(xiàn)的是3塊FPGA處理板之間的數(shù)據(jù)通過GTP協(xié)議進行傳輸,F(xiàn)PGA4和FPGA5暫未用到。

圖3 光纖接口板和FPGA信號處理板之間的連接關系

圖3中P0~P7表示光纖處理板上的8個光模塊,F(xiàn)0~F3表示FPGA處理板上的4片F(xiàn)PGA。

3 軟件設計

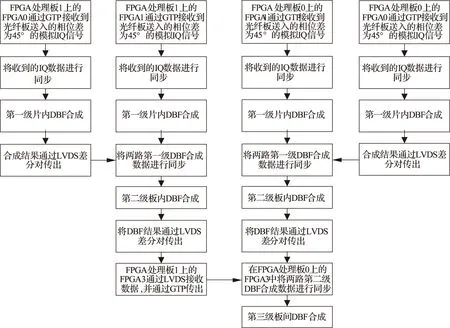

軟件設計整個流程為:首先在光纖接口板中模擬16路前端TR組件送來的I/Q信號,并設置該16通道間信號相位差為45°,以假設目標從45°方向向線陣照射。FPGA處理板0和1的FPGA0和FPGA1同時接收由光纖板送入的相位差為45°的16bit的16路IQ信號也就是每片F(xiàn)PGA接收4路IQ信號,之后將各路數(shù)據(jù)進行同步,并進行第一級片內(nèi)的DBF合成。將FPGA0的第一級DBF合成結(jié)果通過LVDS傳送到FPGA1上,并和FPGA1上的第一級DBF合成結(jié)果進行同步,之后進行第二級板內(nèi)的DBF合成,并將第二級DBF合成結(jié)果都通過LVDS送到FPGA3上,將FPGA處理板1的FPGA3收到的第二級DBF合成結(jié)果通過GTP送往FPGA處理板0的FPGA3上,在FPGA處理板0的FPGA3中將通過GTP收到的FPGA處理板1的第二級DBF合成結(jié)果和通過LVDS收到的FPGA處理板0的第二級DBF合成結(jié)果進行同步,之后進行第三級板間的DBF合成,得到最終的數(shù)字波束合成結(jié)果。

圖4為整個VPX硬件平臺實現(xiàn)板間數(shù)據(jù)流收發(fā)、同步、DBF合成等流程的框圖。

圖4 軟件設計流程的框圖

下面以FPGA處理板0上的FPGA0為例介紹軟件設計流程。

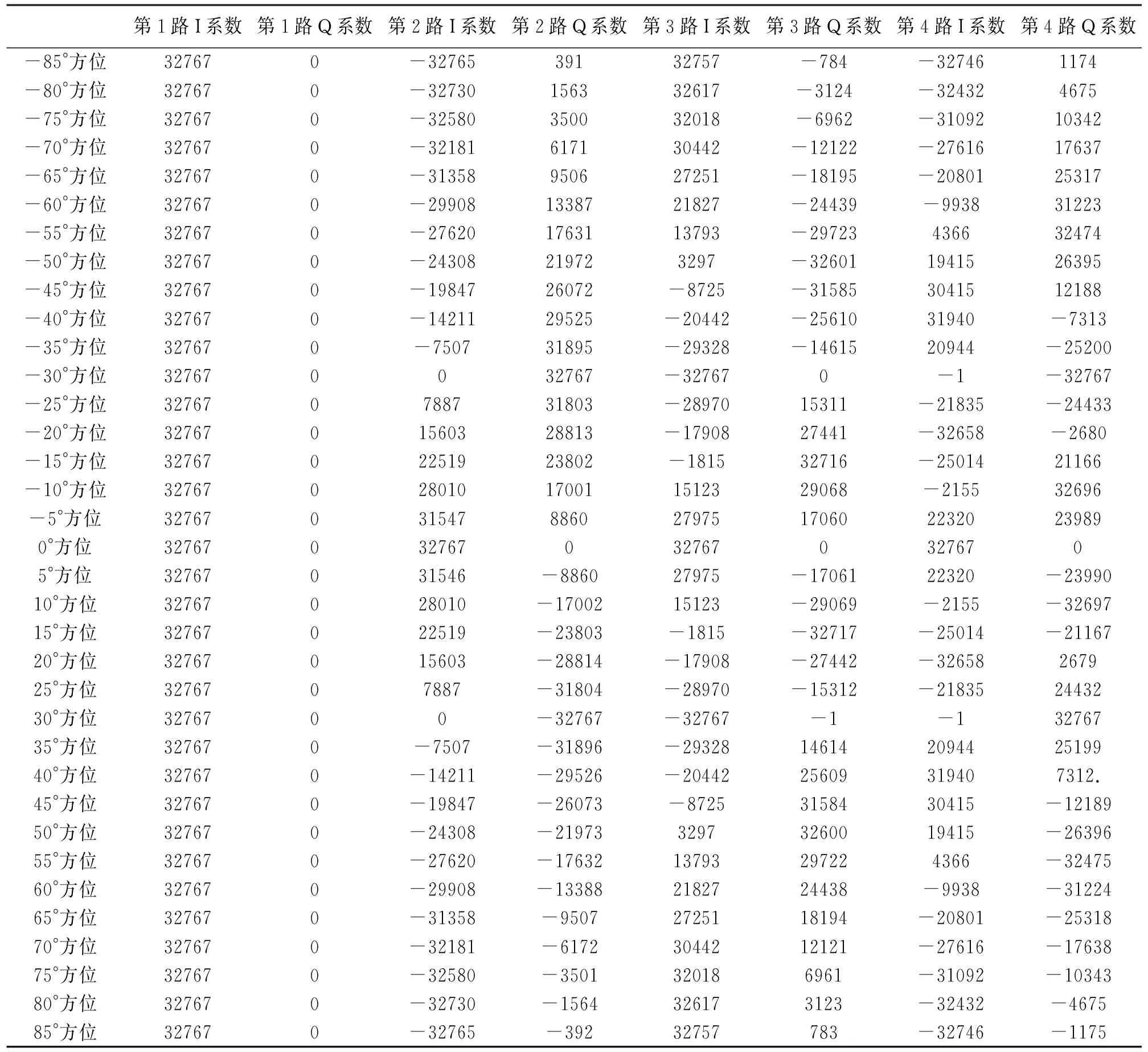

FPGA處理板0上的FPGA0前端送入為四路入射角相差45°的模擬IQ信號,信號的脈寬和頻率均為0.4 μs和5 MHz,采樣率為125 MHz,天線單元間距為半波長即d/λ=1/2, 入射角θ為45°。將各參數(shù)帶入式(1),分別計算出-85°~85°共35個波位對應的DBF系數(shù)(幅度采用矩形窗進行加權(quán))。由于FPGA一般不支持浮點運算,所以計算結(jié)束后還要將各組系數(shù)乘以215,并取整,從而完成16位量化。所得的系數(shù)如表1所示。

FPGA處理板0上的FPGA0前端接收到的四路信號分別為I1+jQ1、I2+jQ2、I3+jQ3和I4+jQ4。

由式(10)所示,分別將這四路信號和某一方位的波束對應的四路系數(shù)進行復數(shù)乘法運算,則求得DBF在該方位的第一級DBF合成結(jié)果。

(I1+jQ1)×(I第一路系數(shù)+jQ第一路系數(shù))

(12)

(I2+jQ2)×(I第二路系數(shù)+jQ第二路系數(shù))

(13)

(I3+jQ3)×(I第三路系數(shù)+jQ第三路系數(shù))

(14)

(I4+jQ4)×(I第四路系數(shù)+jQ第四路系數(shù))

(15)

同樣方法可以先計算出FPGA處理板0上的FPGA1、FPGA處理板1上的FPGA0及FPGA處理板1上的FPGA1的其他3組35個DBF系數(shù),再使用同樣方法求得各FPGA片上的第一級DBF合成結(jié)果。

第二級DBF合成是將FPGA0的第一級DBF合成結(jié)果通過LVDS送入FPGA1中,并同F(xiàn)PGA1中的第一級合成結(jié)果相加而得。

表1 FPGA處理板0上的FPGA0中對應的35個DBF系數(shù)

第三級DBF合成是將FPGA處理板1的第二級DBF合成結(jié)果通過GTP結(jié)果送入FPGA處理板0中,并同F(xiàn)PGA處理板0中的第二級DBF合成結(jié)果相加而得。

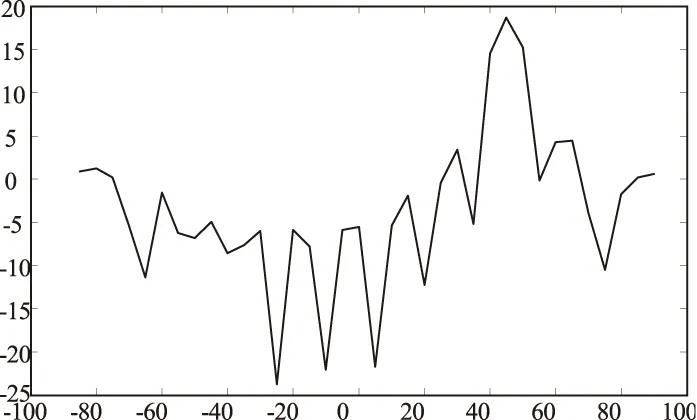

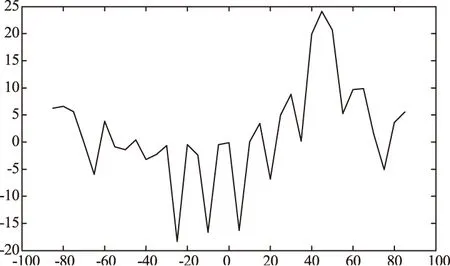

4 試驗結(jié)果

將收到的16路信號分別和-85°-80° -75° -70° -65° -60°-55° -50° -45° -40° -35° -30° -25° -20° -15° -10° -5° 0° 5° 10° 15° 20° 25° 30° 35° 40° 45° 50° 55° 60° 65° 70° 75° 80° 85°共35個方位波束對應的DBF系數(shù)進行DBF合成,再在合成結(jié)果的基礎上求出相對功率。這樣每個DBF系數(shù)就對應一個相對功率值。將這35個值做圖如圖5所示。再根據(jù)線陣方向圖函數(shù)式(11),在MATLAB中進行仿真,仿真結(jié)果如圖6所示。可見,所得到的DBF方向圖和理論的DBF方向圖基本一致,從而驗證了DBF結(jié)果的正確性。

圖5 試驗所得的DBF方向圖

圖6 理論的DBF方向圖

5 結(jié)束語

本文首先介紹了DBF合成的理論算法,并在基于VPX硬件平臺上實現(xiàn)了DBF合成,并且驗證了DBF合成結(jié)果的正確性。隨著信號處理器和FPGA 的高速發(fā)展,數(shù)字波束形成技術在現(xiàn)代雷達與通信等領域中將得到廣泛的應用。

[1] 張光義.相控陣雷達原理[M].北京:國防工業(yè)出版社,2009.

[2] 曹鋼.基于FPGA的數(shù)字波束形成研究[D].西安:西安電子科技大學,2007.

[3] 朱榮新,方姚生.雷達數(shù)字波束形成器的研究與實現(xiàn)[J].現(xiàn)代雷達,2003(2).

Implementation of digital beam forming based on VPX platform

WU Wei, ZHANG Wen-xing

(No. 724 Research Institute of CSIC, Nanjing 211153)

Digital Beam Forming (DBF) is the key technology in radar and communication engineering. The basic principle of the DBF is briefly introduced, and its hardware implementation is accomplished based on the VPX platform.

DBF; VPX; FPGA

2014-04-03;

2014-05-24

吳衛(wèi)(1977-),男,工程師,碩士,研究方向:雷達信號處理;章文星(1969-),男,高級工程師,研究方向:雷達結(jié)構(gòu)設計。

TN957.51

A

1009-0401(2014)03-0011-04