基于FPGA的鐵路語音記錄系統的設計與實現

唐 琳,黃建剛

(成都大學 電子信息工程學院,四川 成都 610106)

0 引 言

隨著我國經濟的不斷發展,交通工具也在不斷的更新,高鐵動車的實際應用,使鐵路交通技術又上了新的臺階,但列車種類的更新與行車速度的提高,對于列車運行的安全保障也提出了更高的要求.先進的交通工具需要先進的安全保障手段,在列車行進過程中的電調、列調、行調、機站、站段等各個部門之間相互的通話記錄都必須存儲保留,以利于日后安全防范和事故取證[1].鐵路語音記錄系統主要用于鐵路上各個站點的語音調度監聽.傳統的鐵路語音記錄設備往往都是用普通單片機作為核心處理器處理監聽的語音數據,因此具有存儲容量小、在線播放實時性能差的特點.本研究提出一種基于FPGA的鐵路語音記錄系統,給出硬件和軟件的設計方式,并詳細介紹了系統的測試過程和測試結果.

1 系統總體方案

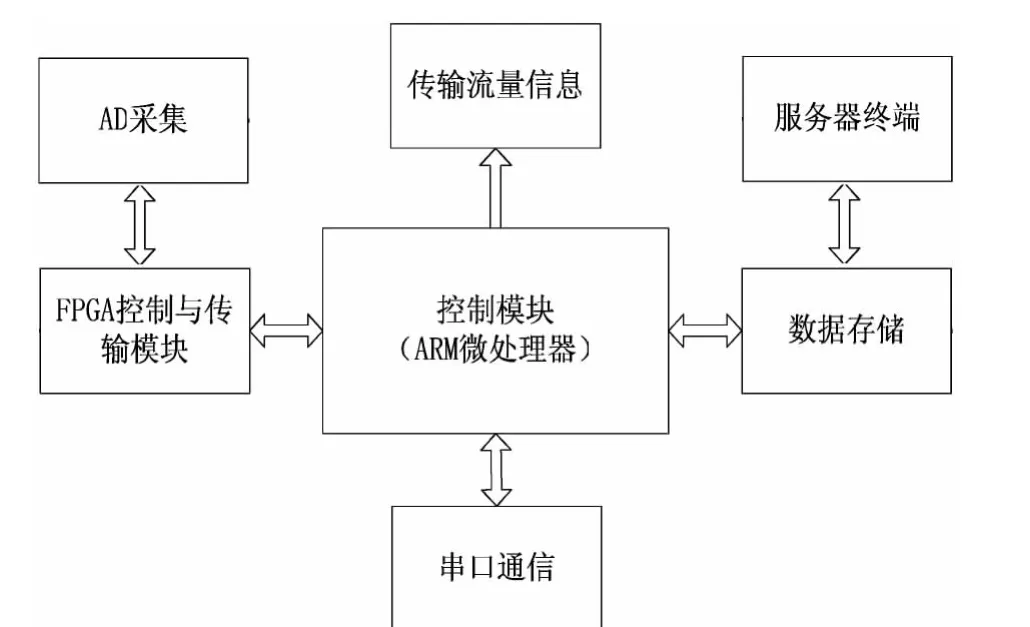

本系統采用ARM +FPGA +聲卡的架構、硬件上各個功能模塊獨立運行與調試的設計方式,系統總體結構框圖如圖1 所示.

圖1 系統總體結構框圖

ARM 微處理器[2]是整個系統的核心,ARM 處理器芯片選用三星ARM9 內核的S3C2440,該芯片外設接口資源豐富,內部集成IIS 接口、SPI 接口、UART 接口、LCD觸摸屏接口和以太網接口.其中,IIS 接口可直接與聲卡芯片UDA1341 進行數據傳遞.UDA1341是飛利浦公司的一款專業級語音處理、語音編解碼芯片,自帶2 路AD/DA,內部集成了PGA(可編程增益調節器)和濾波器.本系統僅利用聲卡的DA 來播放監聽的語音信息,語音記錄采用FPGA 控制AD1974 來實現,AD1974 是ADI 公司一款專業級的語音采集芯片,最多支持4 個通道同時錄音.為了擴大語音記錄系統的存儲容量,增加了USB 接口和SD 卡接口作為本地存儲設備.同時,主控模塊上的以太網接口還可以實現本地存儲信息的在線同步功能,使得互聯網上任何一臺權限設備都可以訪問并獲得該設備的語音記錄信息.

2 硬件與軟件設計

2.1 系統硬件設計

語音記錄系統采用模塊化的硬件設計,其包括主控模塊、本地存儲模塊、電源模塊和數據處理模塊.其中:主控模塊上完成語音信號的前端處理、語音編解碼、和以太網通訊;本地存儲模塊主要包含SD 卡和USB 接口設備,與主控模塊通過排線連接,除電源板之外,整個監聽系統由核心板、主板、數據采集板以及轉接板構成;電源模塊完成220 AC 到5 V DC 的轉換,由集成的電源轉換模塊實現,性能更加穩定可靠;數據處理模塊以FPGA 和AD1974 為核心,完成數據采集、數據緩存和數據處理.

2.2 FPGA 的應用

在本系統中,數據采集板完成的功能包括語音監聽信息的采集、處理和傳輸,其中采集部分由AD電路完成,數據處理和傳輸由FPGA 實現,此外,FPGA 還要負責與主板進行通信,對AD 進行配置[3-5].

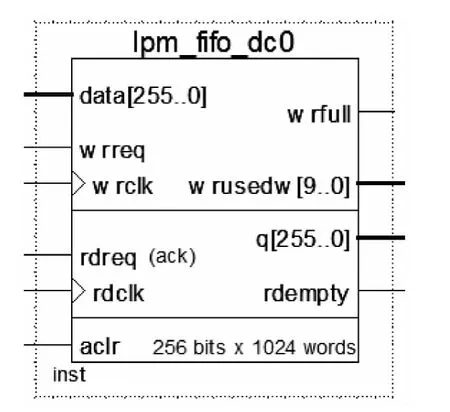

系統硬件設計的重點在于數據處理模塊,加入FPGA 控制語音信息的采集并對采集到數據進行處理,這也是區別于傳統語音記錄系統的地方.數據處理模塊核心芯片為 1 片 Altera IV 系列的EP4CE6C22C8N 和1 片ADI 公司的模數轉換芯片AD1974,FPGA 控制AD1974 完成語音數據采集,并采用IP Core 實現一個128 KB 的DC FIFO 對采集到的數據進行緩存,加上IIS FIFO 就構成了語音記錄系統的雙緩沖池結構.DC FIFO 與微處理器之間通過SPI 總線進行數據傳輸,處理器作為主設備,當需要取數的時候給DC FIFO 一個使能信號,開啟數據傳輸.當處理器不需要取數的時候,FIFO 丟棄溢出數據,確保微處理器取數時保留最新數據,DC FIFO如圖2 所示.

圖2 FPGA 構造的DC FIFO 示意圖

2.3 系統軟件設計

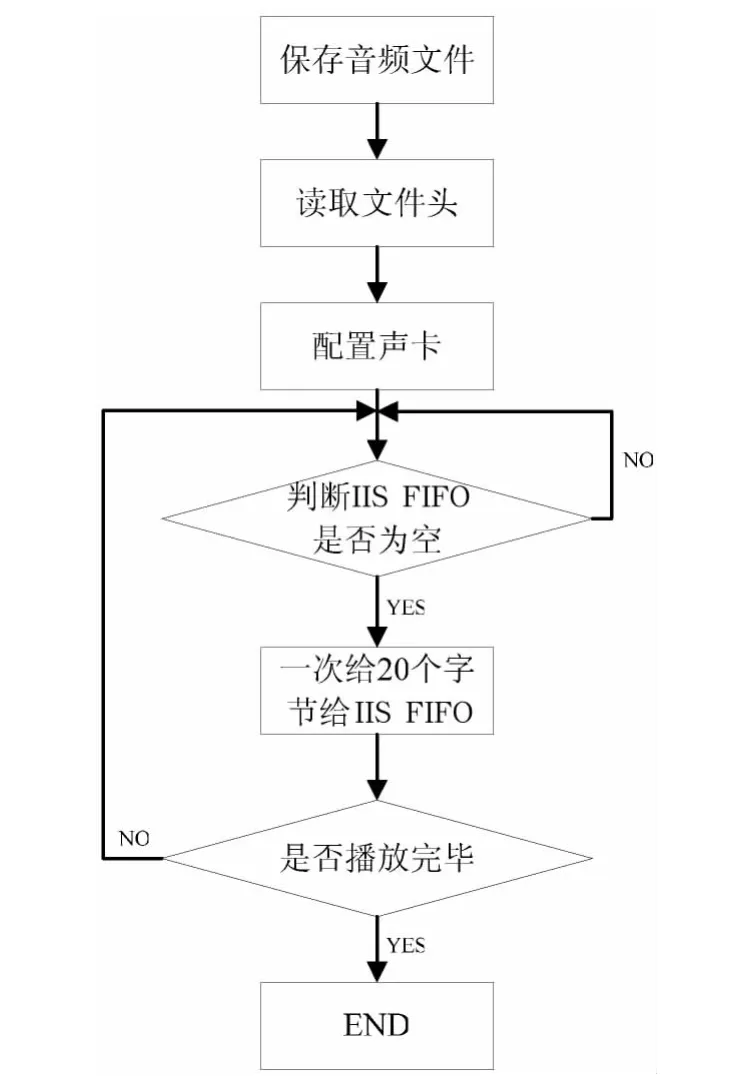

系統的軟件在Linux 操作系統平臺下進行編寫,SPI、IIS、UART、L3 總線等接口的驅動可移植開源的代碼,再將對Linux 內核進行剪裁并重新編譯得到目標Image 文件燒寫到ARM 微處理器的NAND FLASH 中運行[2].系統軟件設計的流程如圖3 所示.

圖3 軟件設計流程圖

3 測 試

語音記錄系統的測試包括多個方面的內容,本研究重點驗證了對FPGA 部分電路的測試.

3.1 FPGA 測試平臺

在對FPGA 的測試之前,必須保證測試工具的聲卡和AD 芯片是可靠的,然后搭建測試平臺對FPGA 的存儲和緩沖功能進行測試.測試平臺包括:主控模塊,1 個;電源模塊,1 個;數據采集模塊,1 個;PC 機,2 臺;鐵路調度電話機,1 臺;USB 線;USB 接口的串口線.

在本系統中,FPGA 構建了1 個256 bit* 1 024 words(內存大小為32 KB)的緩沖池,對AD 采集的數據進行緩沖,這種緩沖機制可以較好地改善在線播放性能.

3.2 FPGA 測試內容及結果

3.2.1 FIFO 溢出后的通信狀態.

在本系統中構建的FIFO 容量為32 KB,聲卡采樣頻率為8 kHz,量化位數為16 bit,假如1 次采集4個通道,1 s 的數據量為64 KB,相當于FIFO 每次最多可以存放0.5 s 的數據量.FIFO 裝滿溢出后的通信狀態測試步驟為:讓AD1974 不停的采集語音數據,并把數據存放到FIFO 中,當FIFO 的滿標志FF第10 次被置位的時候,說明FIFO 已經溢出了10次,同時丟棄了約5 s 的數據,通過判斷空標志EF的狀態來從FIFO 中取數,每次只取1 幀數據(4 個通道8 個Byte).

測試結果顯示,錄音對象為一段10 s 的音頻文件,播放出來為前面的一部分(約5 s)因溢出丟失,后面的5 s 音頻播放正常.測試表明,FIFO 溢出后只是丟失溢出的數據,不會對后面取數造成影響.

3.2.2 FIFO 半滿后的通信狀態.

把AD 采集的數據打入FIFO,ARM 通過判斷FIFO 的半滿標志HF 來判斷FIFO 里面的數是否達到16 KB,只要FIFO 里的數達到了16 KB 就把數取回來,每次取16 KB 存到ARM 緩存,因為ARM 運行的主頻在500 MHz 左右,取16 KB 數據所耗時間幾乎可以忽略,取完之后就等待下一個半滿標志的到來.這樣連續的取數10 s 后將ARM 緩存里的數據逐個給聲卡的IIS FIFO,聲卡就以8 kHz 的頻率將采集到的數據播放出來.

測試結果表明,錄音對象為一段10 s 的音頻文件,播放出來完全正常,無任何數據丟失的情況.

3.2.3 系統在線實時播放功能驗證.

前2 個實驗驗證了FPGA 的存儲功能,實現了系統的本地回放.為了驗證系統的在線實時播放功能,測試中把AD 采集到的語音數據存入FIFO,只要FIFO 不空,微處理器就開始取數,每次取1 幀數據傳遞給IIS FIFO,聲卡按照錄音時8 kHz 的頻率、16 bit 的量化位數進行在線播放.在線播放的關鍵就在于FPGA FIFO 和IIS FIFO 的雙緩沖池設計,該設計極大的減小了數據丟失的概率.只要錄音和播放的速率、量化位數保持一致,主頻為400 MHz 的處理器取數的時間是可以忽略不計的.

測試結果表明,系統在錄音的同時可完成在線回放(延時為ms 級可以忽略不計).

4 結 論

本研究設計的鐵路語音記錄系統增加了FPGA器件,系統的可編程性能得到了提升,同時也提高了系統的存儲容量并改善了在線播放的性能.模塊化的設計方式使得系統運行更加穩定可靠,也為今后系統升級改造提供了方便.現場測試結果表明,本語音記錄系統在精度、可靠性、功耗與穩定性等方面都優于以前的同類系統.

[1]唐琳.網絡化嵌入式鐵路調度監聽系統的研究[D].成都:成都理工大學,2013.

[2]邵貝貝.嵌入式實時操作系統uCOS-II 版[M].北京:北京航空航天大學出版社,2003.

[3]吳小平.差壓流量計的發展現狀[J].常州工學院學報,2007,20(4):50-51.

[4]楊小軍,陳保東,王劍橋,等.差壓流量計的發展和展望[J].工業計量,2010,20(3):27-28.

[5]孫茂一,趙普俊.基于ARM 的科氏質量流量計的遠程監控系統[J].中國測試,2014,40(2):63-67.