基于FPGA狀態(tài)空間方程解算器的HIRFL-CSR電源控制器設(shè)計(jì)

楊 鋒 喬衛(wèi)民 張 瑋 李桂花 安 石顧可偉 武俊奇 姜子運(yùn) 陳 云

1(中國(guó)科學(xué)院近代物理研究所 蘭州 730000)

2(中國(guó)科學(xué)院研究生院 北京 100039)

數(shù)字PI控制的數(shù)字電源[1]在加速器技術(shù)中得到快速發(fā)展與應(yīng)用,然而,電源控制時(shí)的動(dòng)態(tài)性能及負(fù)載擾動(dòng)抑制方面,尚存在不足。微處理器的發(fā)展使計(jì)算機(jī)功能日益強(qiáng)大,成本日益降低,使基于現(xiàn)代控制理論的許多復(fù)雜算法的實(shí)現(xiàn)成為可能。基于狀態(tài)空間模型的最優(yōu)狀態(tài)反饋控制系統(tǒng),可解決PI調(diào)節(jié)器響應(yīng)速度慢、易出現(xiàn)超調(diào)的缺點(diǎn),提高系統(tǒng)的響應(yīng)速度與魯棒性,且在完成多個(gè)狀態(tài)反饋時(shí)也不會(huì)構(gòu)成分立的多閉環(huán)控制系統(tǒng)。為實(shí)現(xiàn)以狀態(tài)反饋為主的復(fù)雜算法,我們?cè)O(shè)計(jì)了基于ARM與現(xiàn)場(chǎng)可編程邏輯門陣列(FPGA)的電源數(shù)字控制器,并在FPGA中設(shè)計(jì)了適用于狀態(tài)反饋控制系統(tǒng)的硬件狀態(tài)空間方程解算器。通過上層軟件對(duì)控制器參數(shù)的修改,便可控制不同磁鐵電源輸出電流的高速、高精度、高穩(wěn)定性。

1 數(shù)字電源控制系統(tǒng)總體結(jié)構(gòu)設(shè)計(jì)

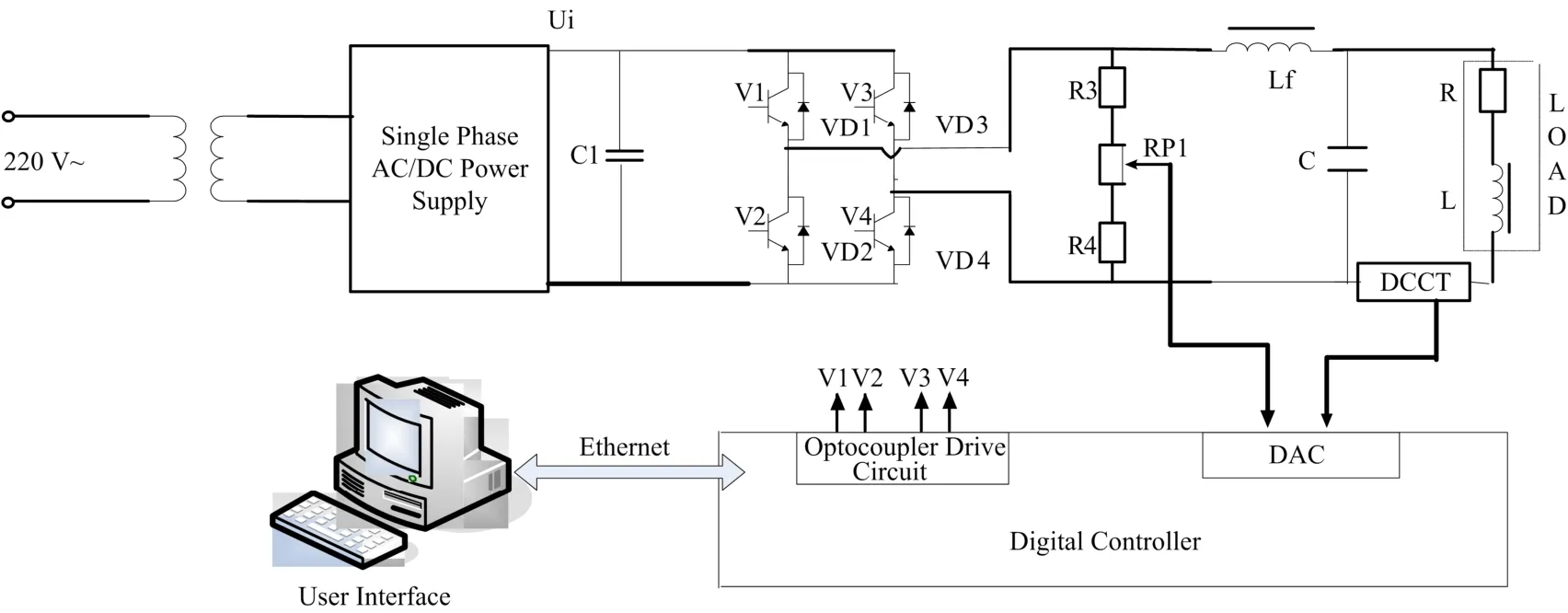

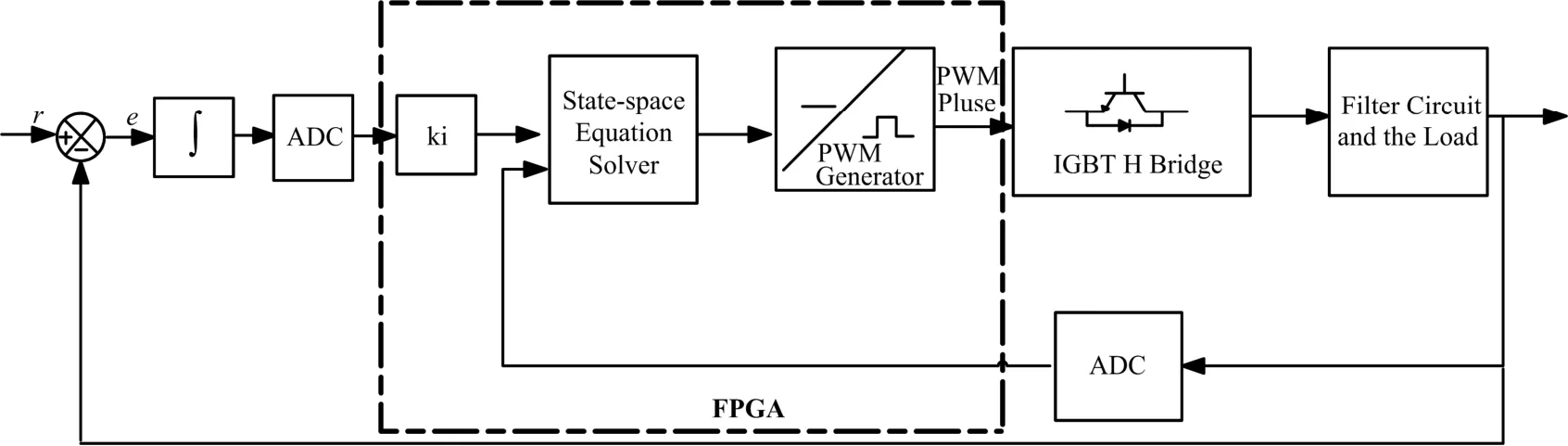

電源控制系統(tǒng)由上層服務(wù)器、智能數(shù)字控制器、采樣反饋電路、功率變換器、濾波器及負(fù)載等組成,整個(gè)數(shù)字電源控制系統(tǒng)如圖1所示。

圖1 電源數(shù)字控制系統(tǒng)硬件結(jié)構(gòu)圖Fig.1 Power supply control system hardware configuration.

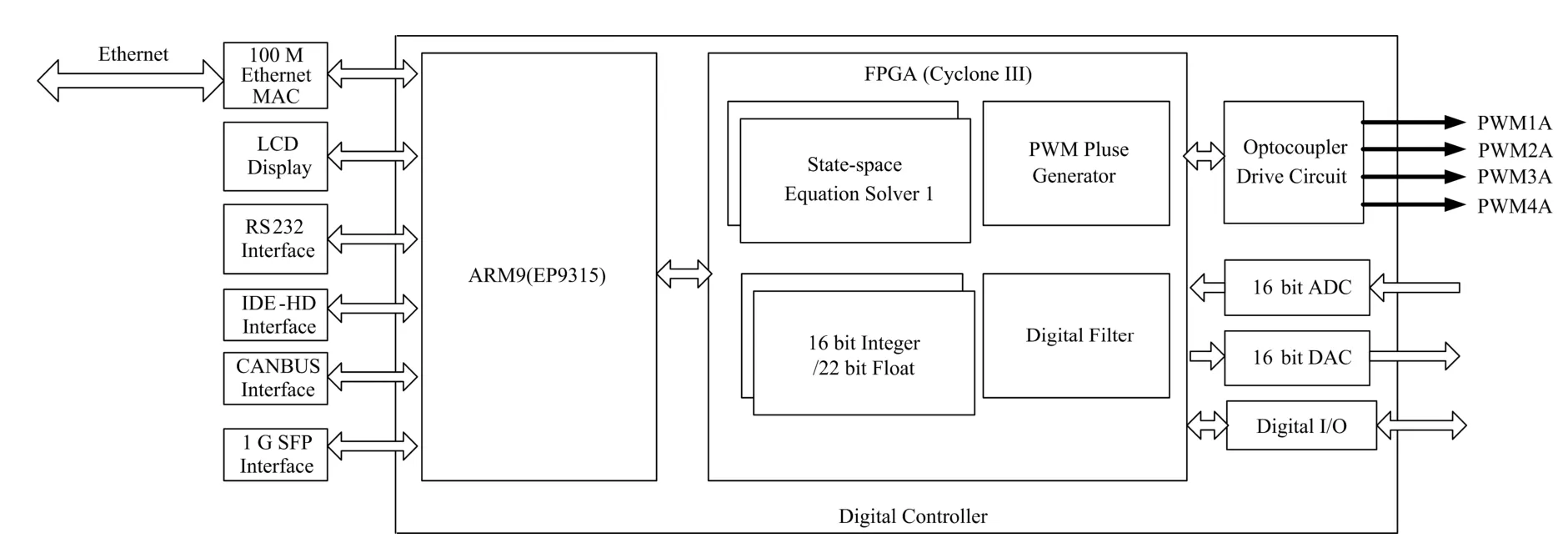

考慮磁鐵電源系統(tǒng)對(duì)精度、響應(yīng)速度、遠(yuǎn)程控制、網(wǎng)絡(luò)傳輸及進(jìn)行高速?gòu)?fù)雜算法的要求,加速器電源控制系統(tǒng)要滿足以下四點(diǎn):(1) 擁有高速數(shù)據(jù)處理和實(shí)時(shí)、高精度的矩陣運(yùn)算能力,并能夠?qū)崿F(xiàn)對(duì)五階及五階以下離散狀態(tài)空間方程的實(shí)時(shí)求解;(2) 擁有高速、高精度的數(shù)據(jù)采集能力;(3) 高分辨率的數(shù)字 PWM 輸出能力;(4) 能夠?qū)崿F(xiàn)良好的人機(jī)交互界面。因此,采用ARM+FPGA嵌入式結(jié)構(gòu)的控制器(圖2)。

圖2 狀態(tài)空間控制器硬件結(jié)構(gòu)框圖Fig.2 Hardware block diagram of state-space controller.

數(shù)字控制器由ARM處理器及FPGA兩大模塊組成,另外配以高精度ADC/DAC模塊、PWM輸出通道以及數(shù)字通訊等外設(shè)。ARM選用ARM9系列的EP9315作為微處理器。主要運(yùn)行嵌入式Linux操作系統(tǒng),并在操作系統(tǒng)上完成系統(tǒng)的多線程任務(wù)處理,包括FPGA數(shù)控單元的數(shù)據(jù)傳輸、外界接口的擴(kuò)展控制及并行完成網(wǎng)絡(luò)通信、觸摸屏接口驅(qū)動(dòng)等任務(wù)。

高速、高精度 ADC是加速器電源數(shù)字化的關(guān)鍵技術(shù),加速器電力電子開關(guān)元器件的開關(guān)頻率高達(dá)20 kHz以上。若ADC采樣頻率小于5倍開關(guān)頻率,控制器的調(diào)節(jié)效果就大打折扣,甚至完全失效。鑒此,選取AD7656作為控制器的模擬/數(shù)字采樣設(shè)備,采樣頻率可達(dá)250 kHz,完全適應(yīng)開關(guān)電源對(duì)高速采樣的要求。

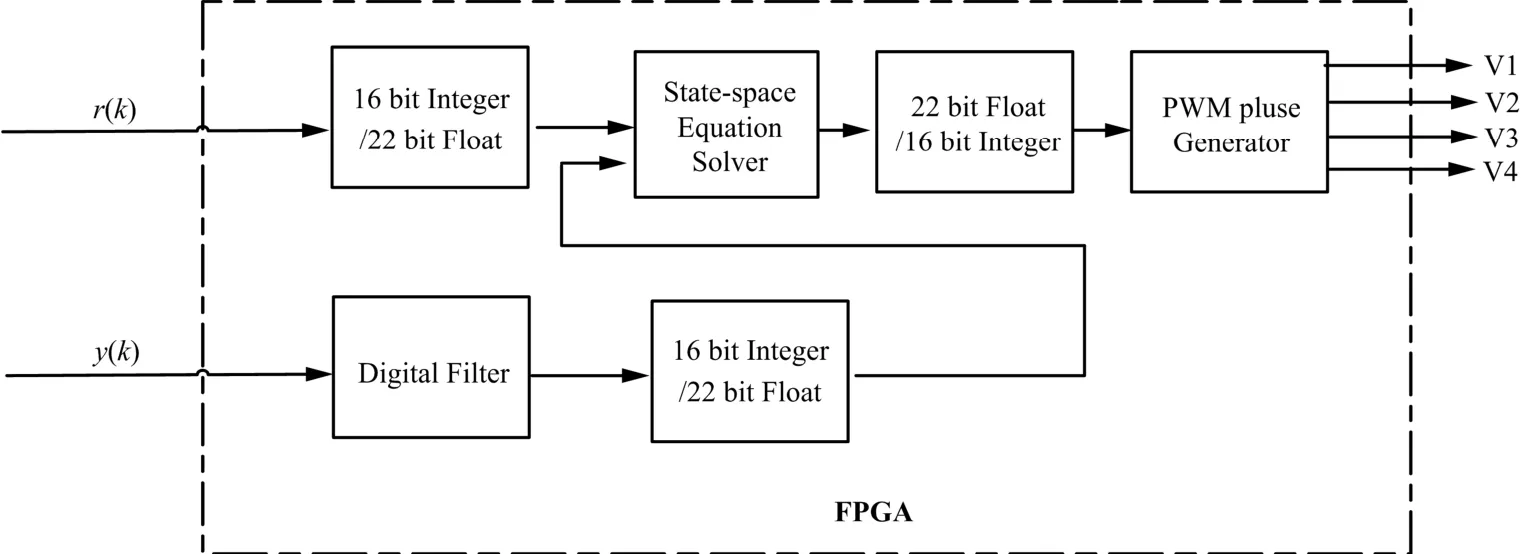

FPGA是整個(gè)控制器中完成電源閉環(huán)控制、進(jìn)行控制算法的核心元件。為滿足高速?gòu)?fù)雜算法的需求,選用Altera公司新一代低成本、大容量、高性能的Cyclone? III EP3C25F256 FPGA。其獨(dú)特的體系結(jié)構(gòu)及豐富的硬件邏輯資源,可設(shè)計(jì)高速浮點(diǎn)數(shù)狀態(tài)空間方程解算模塊、高精度PWM(pulse width modulation)波生成模塊、數(shù)字濾波模塊、ADC/DAC控制模塊、定點(diǎn)轉(zhuǎn)浮點(diǎn)及浮點(diǎn)轉(zhuǎn)定點(diǎn)模塊,F(xiàn)PGA中主要的功能模塊組成如圖3所示。r(k)為給定參考信號(hào),y(k)為AD采樣信號(hào),F(xiàn)PGA將16位定點(diǎn)數(shù)格式的參考給定及經(jīng)過數(shù)字濾波模塊處理的 ADC采樣信號(hào)轉(zhuǎn)化為22位的浮點(diǎn)數(shù),通過狀態(tài)空間方程解算器的高速實(shí)時(shí)運(yùn)算以及PWM波生成模塊的處理,生成固定頻率的PWM波形。

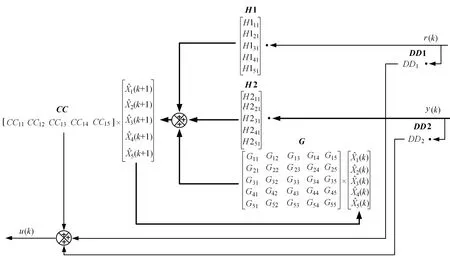

圖3 FPGA系統(tǒng)結(jié)構(gòu)原理框圖Fig.3 FPGA block diagram.

上述結(jié)構(gòu)的數(shù)字控制器,可實(shí)現(xiàn)對(duì)磁鐵電源的各種狀態(tài)反饋控制。對(duì)于不同負(fù)載,可通過上層操作界面修改控制器所需的參數(shù),并通過網(wǎng)絡(luò)接口將參數(shù)及電源基準(zhǔn)信號(hào)傳輸給數(shù)字控制器。數(shù)字控制器經(jīng) 1個(gè)運(yùn)算周期后,輸出控制量。控制量經(jīng)過FPGA的PWM波形生成模塊處理后,轉(zhuǎn)換為高精度的PWM脈寬調(diào)制信號(hào),以此控制H橋開關(guān)管的占空比,實(shí)現(xiàn)對(duì)電源輸出電壓或電流的閉環(huán)控制。

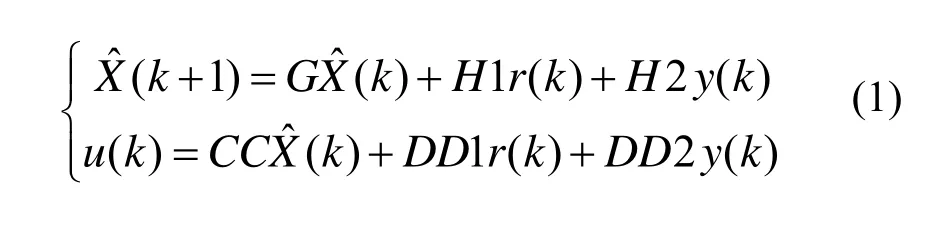

2 狀態(tài)空間解算器在FPGA的實(shí)現(xiàn)

控制算法是影響電源性能的關(guān)鍵因素,圖3 FPGA中的狀態(tài)空間方程解算器是實(shí)現(xiàn)控制算法的關(guān)鍵。為實(shí)現(xiàn)基于現(xiàn)代控制理論的帶觀測(cè)器的狀態(tài)反饋控制[2,3],并確保系統(tǒng)的跟蹤性能及穩(wěn)態(tài)精度良好,綜合基于狀態(tài)空間理論的各種狀態(tài)反饋形式,我們用硬件描述語言VHDL,在FPGA中設(shè)計(jì)了硬件狀態(tài)空間方程解算器:

式中,G、H1、H2、CC、DD1、DD2為 FPGA狀態(tài)空間方程解算器中的常系數(shù)矩陣,r(k)為參考輸入信號(hào),y(k)為系統(tǒng)的輸出反饋信號(hào),u(k)為系統(tǒng)的控制信號(hào)。為能實(shí)現(xiàn)五階及五階以下單輸入、單輸出系統(tǒng)的控制,我們將狀態(tài)向量(k)的維數(shù)最大設(shè)計(jì)為5維,并在FPGA中實(shí)現(xiàn)大量的矩陣運(yùn)算,包括:系數(shù)矩陣G(5×5矩陣)與狀態(tài)向量?(k)的矩陣浮點(diǎn)數(shù)乘加運(yùn)算?(k),系數(shù)矩陣H1(5×1矩陣)與輸入r(k)的矩陣浮點(diǎn)數(shù)乘法運(yùn)算H1r(k),系數(shù)矩陣H2(5×1矩陣)與系統(tǒng)輸出y(k)的矩陣浮點(diǎn)數(shù)乘法運(yùn)算H2y(k),系數(shù)矩陣CC(1×5矩陣)與狀態(tài)向量矩陣?(k)的矩陣浮點(diǎn)數(shù)乘加運(yùn)算(k),系數(shù)矩陣DD1(1×1矩陣)與輸入r(k)的浮點(diǎn)數(shù)乘法運(yùn)算DD1r(k),系數(shù)矩陣DD2(1×1矩陣)與系統(tǒng)輸出y(k)的浮點(diǎn)數(shù)乘法運(yùn)算DD2y(k)。整個(gè)狀態(tài)空間方程在FPGA中的矩陣運(yùn)算流程如圖4所示。

狀態(tài)空間方程解算器中的常系數(shù)矩陣G、H1、H2、CC、DD1、DD2由上層參數(shù)設(shè)計(jì)程序配置,并通過網(wǎng)絡(luò)接口傳輸?shù)?FPGA固定的矩陣存儲(chǔ)器中。當(dāng)控制器接收到觸發(fā)信號(hào)時(shí),則開始根據(jù)給定輸入及輸出反饋信號(hào)進(jìn)行高速的狀態(tài)空間方程解算過程。由于解算器采用流水線技術(shù),最終整個(gè)狀態(tài)空間方程解算器在FPGA的解算周期為200 ns。實(shí)際電源為0型系統(tǒng),為消除由于模型參數(shù)不準(zhǔn)或階躍型干擾引起的穩(wěn)態(tài)誤差,在控制器參考輸入端引入一積分控制,整個(gè)電源控制系統(tǒng)結(jié)構(gòu)如圖5所示。

圖4 狀態(tài)空間方程解算器的數(shù)據(jù)流程圖Fig.4 Data flow diagram of the state-space equation solver.

3 仿真及試驗(yàn)結(jié)果

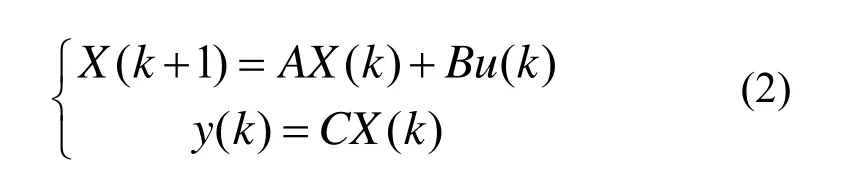

為驗(yàn)證該控制器對(duì)電源系統(tǒng)的控制效果,由圖1所示的試驗(yàn)平臺(tái),選取實(shí)驗(yàn)參數(shù)為[1]:平波電感Lf=0.68 mH,濾波電容C=30 μF,負(fù)載電阻R=0.766?,負(fù)載電感L=0.34 mH(實(shí)驗(yàn)負(fù)載為電抗器串聯(lián)電阻),PWM模塊輸出頻率設(shè)置為20 kHz。為簡(jiǎn)化試驗(yàn)過程,在滿足輸出功率、輸出電壓紋波、輸出電壓精度及穩(wěn)定度的前提下,用直流穩(wěn)壓電源代替電壓預(yù)穩(wěn)電路,穩(wěn)壓電源輸出電壓Ut=15 V。設(shè)電源系統(tǒng)平均狀態(tài)空間[4,5]方程為:

式中,X(k)為狀態(tài)向量,y(k)為輸出量,u(k)為控制量,A為狀態(tài)矩陣,B為輸入矩陣,C為輸出矩陣。

圖5 帶積分控制的電源狀態(tài)反饋控制系統(tǒng)結(jié)構(gòu)框圖Fig.5 Block diagram of the state-feedback control system with integral action.

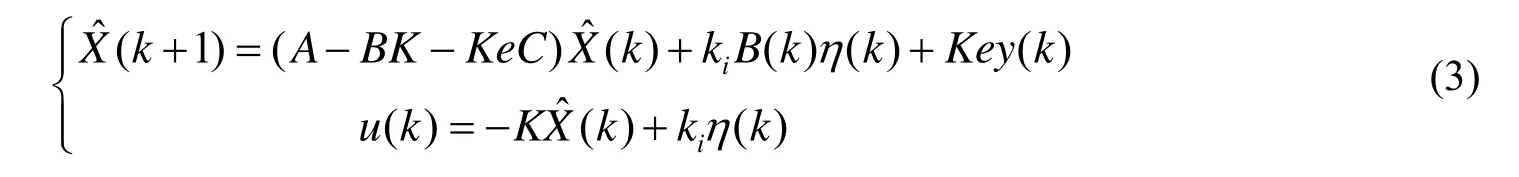

對(duì)該電源進(jìn)行線性二次型最優(yōu)[2,3](LQR)狀態(tài)反饋設(shè)計(jì),在控制器算法中構(gòu)造觀測(cè)器,并在控制器參考輸入前端引入了積分控制。利用現(xiàn)代控制理論的狀態(tài)反饋設(shè)計(jì)方法,經(jīng)過轉(zhuǎn)換及計(jì)算,可得控制器的結(jié)構(gòu)為:

式中,K為利用LQR方法確定的系統(tǒng)狀態(tài)反饋增益矩陣,Ke為狀態(tài)觀測(cè)器的增益矩陣,為積分增益常數(shù)。比較式(3)與式(1),可得狀態(tài)空間解算器矩陣參 數(shù) :G=A–BK–KeC,H1=kiB,H2=Ke,CC=–K,DD1=ki,DD2=0。

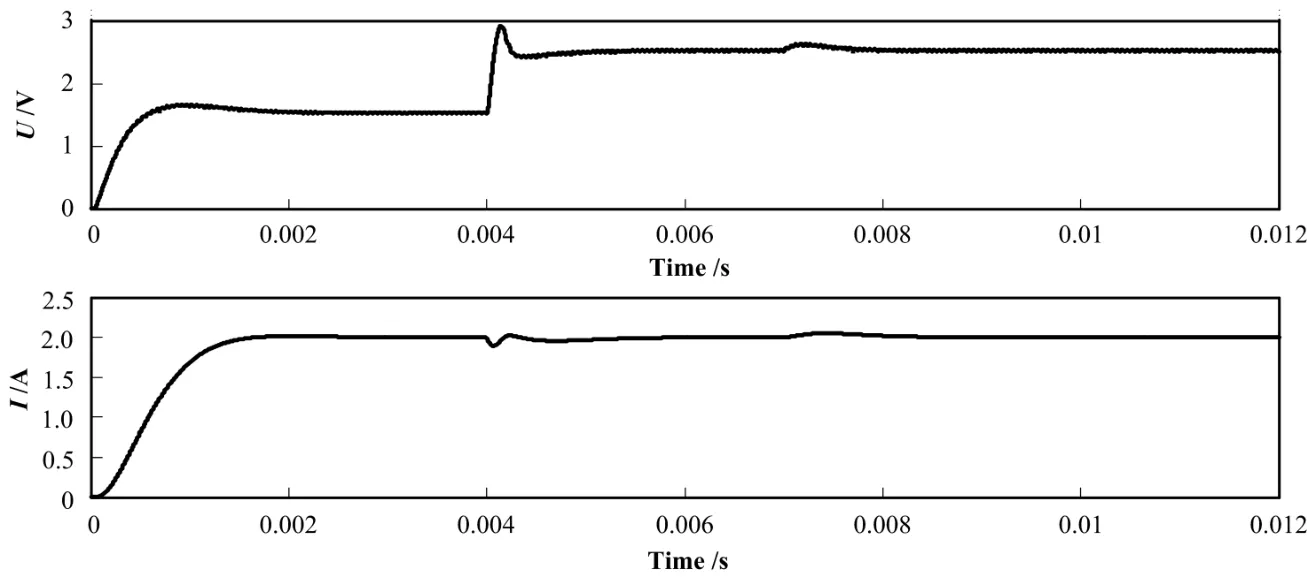

本文用Simulink和SimPower System工具箱[6],對(duì)上述電源控制系統(tǒng)進(jìn)行仿真,其閉環(huán)系統(tǒng)動(dòng)態(tài)特性曲線如圖6所示。閉環(huán)系統(tǒng)在2 ms時(shí),輸出就可無靜差地穩(wěn)定于給定值。在4 ms時(shí),將負(fù)載R由0.766 ?瞬間跳變?yōu)?.266 ?;在7 ms時(shí),將輸入電壓Ui從15 V跳變?yōu)?0 V,擾動(dòng)幅度為20%以上,而系統(tǒng)在2 ms內(nèi)可消除干擾影響,使負(fù)載端電壓穩(wěn)定在新的平衡點(diǎn),并始終保持輸出電流穩(wěn)態(tài)值不變。

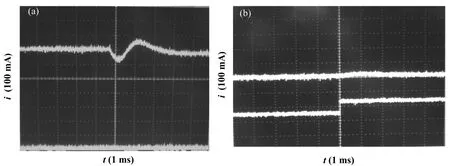

圖7為電源在負(fù)載與輸入電壓發(fā)生階躍性跳變時(shí)的測(cè)試結(jié)果。圖7(a)為電阻發(fā)生跳變時(shí)的電源電流輸出回讀曲線,干擾在3 ms內(nèi)消除;圖7(b)為輸入電壓發(fā)生跳變時(shí)的電源電流輸出回讀曲線,干擾在2 ms內(nèi)消除。由于實(shí)際電路參數(shù)與仿真參數(shù)有誤差,響應(yīng)時(shí)間有所差異,響應(yīng)曲線與仿真基本一致。

圖6 狀態(tài)反饋電源控制系統(tǒng)輸出電壓/電流的仿真動(dòng)態(tài)響應(yīng)曲線Fig.6 Transient response curve of the state feedback control system simulation.

圖7 狀態(tài)反饋電源控制系統(tǒng)輸出電壓/電流的試驗(yàn)動(dòng)態(tài)響應(yīng)曲線圖Fig.7 Transient response curve of the state feedback control system.

4 結(jié)語

本文采用基于ARM+FPGA結(jié)構(gòu)的全數(shù)字控制器,以帶有狀態(tài)空間解算器的FPGA作為控制器的核心,實(shí)現(xiàn)對(duì)開關(guān)電源高速、實(shí)時(shí)的狀態(tài)反饋控制。其系統(tǒng)仿真及試驗(yàn)的結(jié)論以下:

(1) 基于FPGA狀態(tài)空間方程解算器的最優(yōu)狀態(tài)反饋系統(tǒng)能夠無靜差地跟蹤電源給定值,大大提高了開關(guān)電源的動(dòng)態(tài)響應(yīng)速度、穩(wěn)態(tài)精度、抗干擾性及魯棒性;

(2) 運(yùn)用VHDL語言設(shè)計(jì)的基于FPGA狀態(tài)空間解算器的數(shù)字控制器,可以很好地實(shí)現(xiàn)對(duì)五階及五階以下被控對(duì)象的觀測(cè)-狀態(tài)反饋閉環(huán)控制,這在加速器控制器的設(shè)計(jì)中是一種全新的嘗試;

(3) 基于 ARM+FPGA的控制器集成度高,結(jié)構(gòu)布局合理,適用性強(qiáng),對(duì)于不同的電源負(fù)載,無需重新配置硬件,只需通過上層軟件修改控制器的參數(shù)(G、H1、H2、CC、DD1、DD2)來滿足指標(biāo)要求,大大縮短控制系統(tǒng)設(shè)計(jì)的周期。

(4) 該控制器不僅可以在線修改控制參數(shù),而且可根據(jù)不同的控制對(duì)象在線修改控制算法。使控制系統(tǒng)的設(shè)計(jì)主要集中在FPGA程序的設(shè)計(jì)上,為對(duì)加速電源進(jìn)行智能控制等更復(fù)雜的控制系統(tǒng)設(shè)計(jì)奠定了基礎(chǔ)。

該控制系統(tǒng)的研制與實(shí)現(xiàn),將為加速器束流品質(zhì)和運(yùn)行效率的提高起到重要作用。在FPGA高速狀態(tài)空間解算器的基礎(chǔ)上,還可進(jìn)一步進(jìn)行自適應(yīng)控制、智能控制等現(xiàn)代復(fù)雜控制策略的研究。期待在系統(tǒng)優(yōu)化的基礎(chǔ)上,對(duì)該控制器實(shí)現(xiàn)產(chǎn)品化及規(guī)模化,為加速器的發(fā)展作出貢獻(xiàn)。

1 王進(jìn)軍. 加速器電源的數(shù)字化研究與設(shè)計(jì)[D]. 蘭州:中國(guó)科學(xué)院近代物理研究所, 2010 WANG Jingjun. Digital Power Supply for Accelerator Researching and Design [D]. Lanzhou: Institute of Modern Physics, Chinese Academy of Sciences, 2010

2 Katsuhiko Ogata. Modern Control Engineering [M].Englewood: Prentice Hall, 2009: 64–66, 767–771

3 Katsuhiko Ogata. Discrete Time Control Systems [M].Upper Saddle River: Prentice Hall, 1995: 317

4 Sherif Hammad, Mentor Graphics. H1 field bus network delay, a digital pole placement control design[C].Proceedings of the 17thCongress of the International Federation of Automatic Control, Seoul, Korea, 2008,6-11: 9433–9436

5 Maksimovic. Automated small-signal analysis of switching converters using a general-purpose timedomain simulator. Applied Power Electronics Conference and Exposition, APEC'98, Conference Proceedings 1998,Thirteenth Annual, 1998, 1: 357–362

6 洪乃剛. 電力電子技術(shù)基礎(chǔ)[M]. 北京: 清華大學(xué)出版社, 2008: 49–51 HONG Naigang. Fundamentals of Power Electronics [M].Beijing: Peking University Press, 2008: 49–51