Geffe流密碼分析與實現

段志剛 ,佟 晶

(1.深圳市龍圖軟件有限公司,黑龍江 哈爾濱 150001;2.中航工業哈爾濱軸承有限公司 研發中心,黑龍江 哈爾濱150036)

1 前言

流密碼(stream cipher)也稱序列密碼,它是對稱密碼算法的一種。由于流密碼長度可靈活變化,且具有運算速度快、密文傳輸中沒有差錯等優點,目前仍是國際密碼應用的主流,而基于偽隨機序列的流密碼是當今最通用的密碼系統。本文采用基于LFSR和非線性組合函數的方法設計密鑰流生成器,不僅便于從理論上分析其安全性,而且易于硬件實現。經嚴格測試表明,該加密設計能產生高質量、高速的偽隨機密鑰流,它在保密學領域有廣泛的應用。

2 流密碼相關原理

流密碼有以下優勢:密鑰的產生與使用簡單,流密碼按單個字符加密,不需要太多的緩存,不會在明文中產生錯誤擴散,實時性好,運算速度快,硬件實現的復雜度要低等,因此,流密碼在相當長的時間內是人們使用的主要加密方法,目前仍是各國政府、軍事、外交等核心部門使用的主流密碼。流密碼加密、解密框圖如圖1所示。

圖1 流密碼加密解密框圖

3 Geffe流密碼模塊

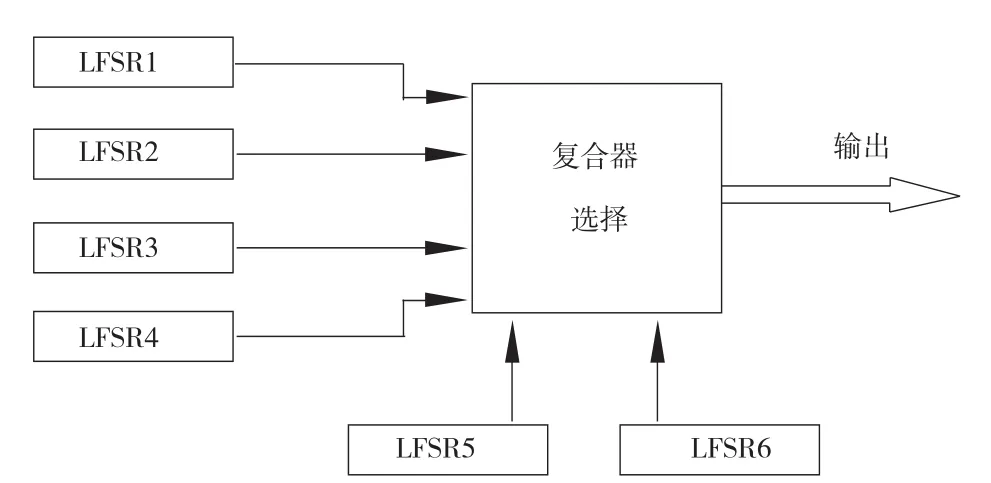

Geffe流密碼電路框圖如圖2 所示。這個發生器使用了六個LFSR,他們以非線性方式組合而成,LFSR1、LFSR2、LFSR3、LFSR4作為復合器的輸八,LFSR5、LFSR6控制復合器的輸出。LFSR5、LFSR6在四個LFSR中進行選擇,且LFSR5、LFSR6比其它四個運行快1倍。

圖2 Geffe模塊

為了實驗簡易方便,六個LFSR的級數分別選為:2,3,4,5,6,7;它們的特征多項式分別為 f1(x)=x2+x+1,f2(x)=x3+x+1 ,f3(x)=x4+x+1 ,f4(x)=x4+x2+1 ,f5(x)=x6+x+1 ,f6(x)=x7+x3+1 ,并通過數據選擇器控制輸出。所有輸入均共用同一個CP脈沖。這樣既能使得該序列某些統計特性不被破壞,如偽隨機序列重要特性0與1的平衡性、序列相關性等,又能對多個LFSR進行控制輸出,起到非線性系統作用;可設置密鑰的控制參數,改變此參數可改變相應的輸出,這樣可使整個密碼系統構成多級密鑰關系,使流密碼的保密性進一步加強。

Geffe模塊共六組輸入,這樣較單個m序列相比提高其輸出周期和增加密鑰空間。

六個LFSR的周期分別為 22-1,23-1,24-1,25-1,26-1,27-1 ,而Geffe發生器的周期是這六個LFSR的周期的最小公倍數。

4 Geffe模塊的設計

用Quartus II來實現Geffe模塊電路原理設計圖如圖3 所示。

圖3 Geffe模塊電路圖

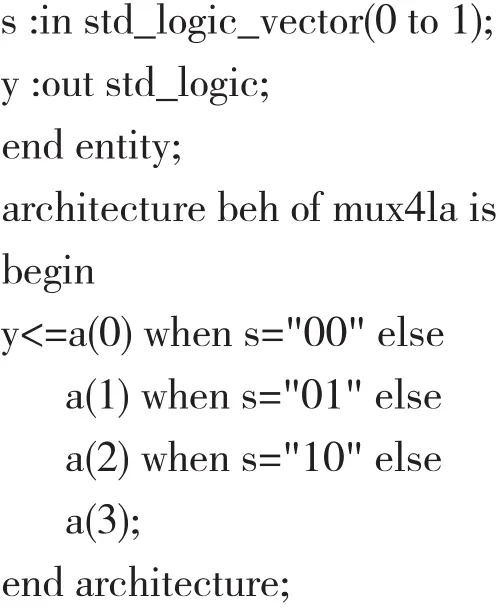

設計中用到的LFSR1至LFSR6都是在Quartus II環境下由原理圖輸入法D觸發器形成的。圖4選擇器MUX是用VHDL語言生成的。程序設計如下:

編完程序后在“File”中選擇“Create/-Update—Create Symbol Files for Current file”即生成選擇器,見圖3。設計完成后對其進行仿真,仿真結果如圖4 所示。

圖4 仿真結果

其中cp為時鐘信號,rst為復位信號。m2至m7為初始密鑰輸入,其中初始密鑰分配如下:m2提供給了LFSR1; m3提供給了LFSR2; m4提供給了LFSR3;m5提供給了LFSR4;m6提供給了LFSR5;m7提供給了LFSR6。Out為Geffe流密碼序列輸出,可從仿真結果可以看出:輸出序列為一偽隨機序列,利用此序列可與明文序列進行加密然后傳輸,利用Geffe流密碼產生的偽隨機碼較傳統m序列有周期長,輸出序列復雜等良好性能。

此模塊可以下載到FPGA器件中設計成加密芯片,考慮到FPGA配置文件數據比較大,為了加快配置速度,采用的是EPFlOK20生成Geffe流密碼模塊,該模塊可應用于計算機網絡和通信系統中,提高信息傳輸的安全性。通過改變輸入參數可以模擬不同的非線性函數,避免了在傳統電路設計中,模擬不同的非線性函數須變換不同電路的缺點。

5 結束語

本論文在深入學習和研究現代密碼學理論特別是流密碼理論與技術的基礎上,完成了Geffe流密碼分析與實現。利用FPGA工具對Geffe流密碼進行設計,用Quartus II來實現Geffe模塊的設計,并用VHDL語言實現了其功能,為流密碼輸出奠定了基礎,利用VHDL設計了數據選擇器并完成其功能,通過實驗可看出產生輸出序列,驗證了所設計電路的正確性,為流密碼芯片的實際開發與應用奠定了基礎。

[1]C.E.Shannon. Communication theory of secrecy systems[J].Bell System Technology Jounal Vol.28.1949,20(2): 656-715.

[2]丁存生,肖國鎮.流密碼及其應用[M].上海:國防工業出版社,1994:163-224.

[3]張文政.布爾函數若干設計準則的研究[C].張文政.通信保密.北京:清華大學出版社,1994(2):105-138.