綜合化通信設備信號流程設計與實現

黃嘉春,曹永剛

(1.中國西南電子技術研究所,成都 610036;2.解放軍駐沈陽飛機工業(集團)公司軍事代表室,沈陽110034)

傳統的航電系統中,通信、導航等功能都是以分離式的單一設備完成其相應的功能,而近幾年出現的綜合化航電系統是將通信、導航等功能作為整體進行設計,其特點是系統架構開放化,軟硬件模塊化、通用化,通過采用開放式系統架構和模塊化通用設計標準,達到降低研制和生產成本、縮短開發周期、減少現役飛機的維護和保障成本的目的[1]。本文基于綜合化航電系統通信設備的硬件框架,提出了綜合化通信設備的信號處理流程設計,并給出了其流程的實現,分析了其具有的優點。

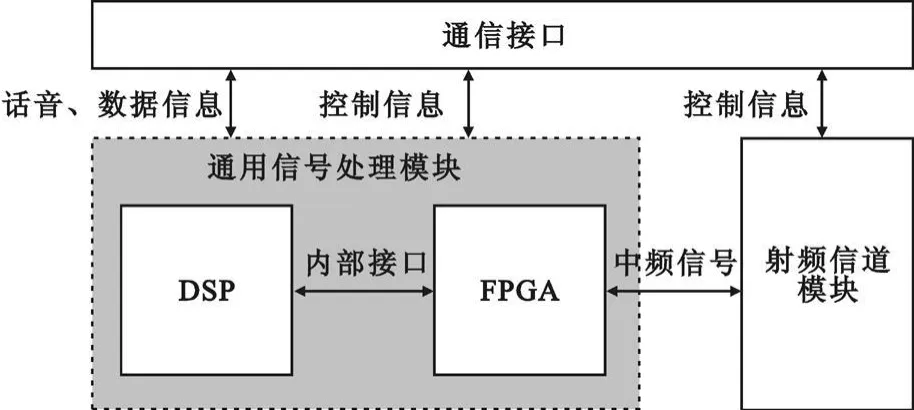

1 通用信號處理的硬件框架

綜合化航電系統通用信號處理的硬件框架如圖1所示。其硬件資源即通用信號處理模塊主要包括DSP芯片、FPGA芯片、數據信息和控制信息通信接口、中頻接口,以及間接控制射頻信道模塊的控制信息接口[2]。

圖1 通用信號處理模塊的硬件框架示意圖Fig.1 Hardware framework of universal signal processing

綜合化通信設備的信號處理模塊主要完成以下功能:

(1)完成通用信號處理模塊和系統的控制信息交互,主要包括狀態參數、自檢狀態等信息的交互;

(2)完成通用信號處理模塊和系統的數據信息交互,即數據信息的接收和上報;

(3)完成相應工作模式下的信號處理功能,即信源編解碼、信號處理調制和解調,以及和射頻信道模塊交互中頻信號;

(4)完成相應工作模式下對射頻信道模塊的工作參數、收發狀態以及頻率信息的控制。

綜合化通信設備的主要工作就是將傳統獨立設備中的信號處理功能快速、穩定地移植到綜合化設備的通用信號處理模塊。

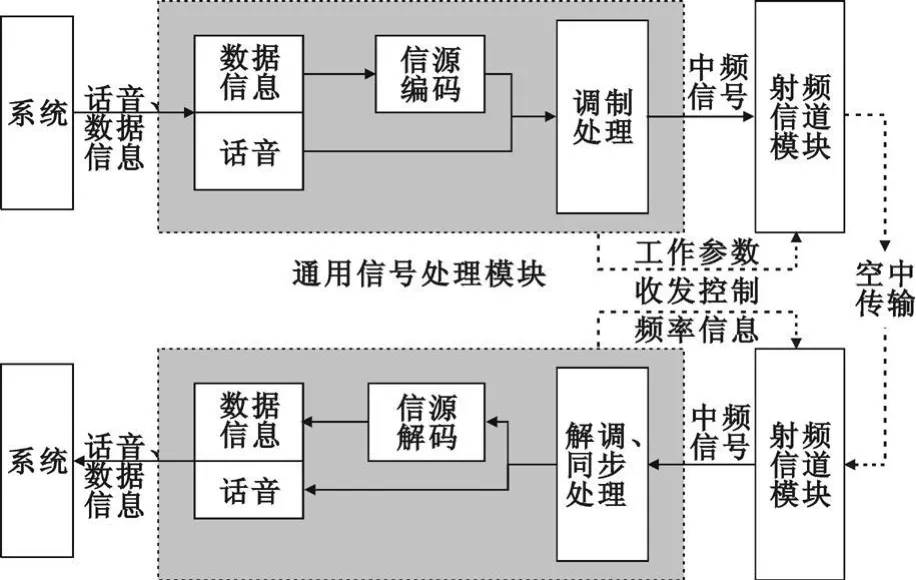

2 綜合化通信設備信號流程的設計

縱觀綜合化通信設備通用信號處理模塊需要完成的功能,存在兩個信號流程:一個控制信號流程,一個話音和數據信號流程。控制信號流程比較清晰,即接收系統控制信息后,回傳系統控制信息;如果需要轉發射頻信道模塊,那么將相應的控制信息轉發給射頻信道模塊;如果通用信號處理模塊有及時的控制信息需要上傳,直接上傳系統。另一個信號流程即話音和數據信號流程,如圖2所示。

圖2 綜合化通信設備話音、數據信息處理流程圖Fig.2Flowchart of signal of voice and data in integrated communication equipment

如圖2所示,通信設備信號處理發送流程如下所述。通用信號處理模塊收到系統下發的信息后,如果是數據信息,進行信源編碼(如RS編碼/Turbo編碼等),如果是話音,不做處理;然后對話音和已編碼的數據信息進行調制處理到中頻信號;最后發送到射頻信道模塊,即完成了通用信號處理模塊的通信設備信號處理發送功能。

通信設備信號處理接收流程如下所述。通用信號處理模塊收到射頻信道模塊的中頻信號后,首先進行解調、同步處理;如果是數據信息,進行信源解碼處理,如果是話音,不做處理;然后將恢復的話音和數據信息上報給系統,即完成了通用信號處理模塊的通信設備信號處理接收功能。

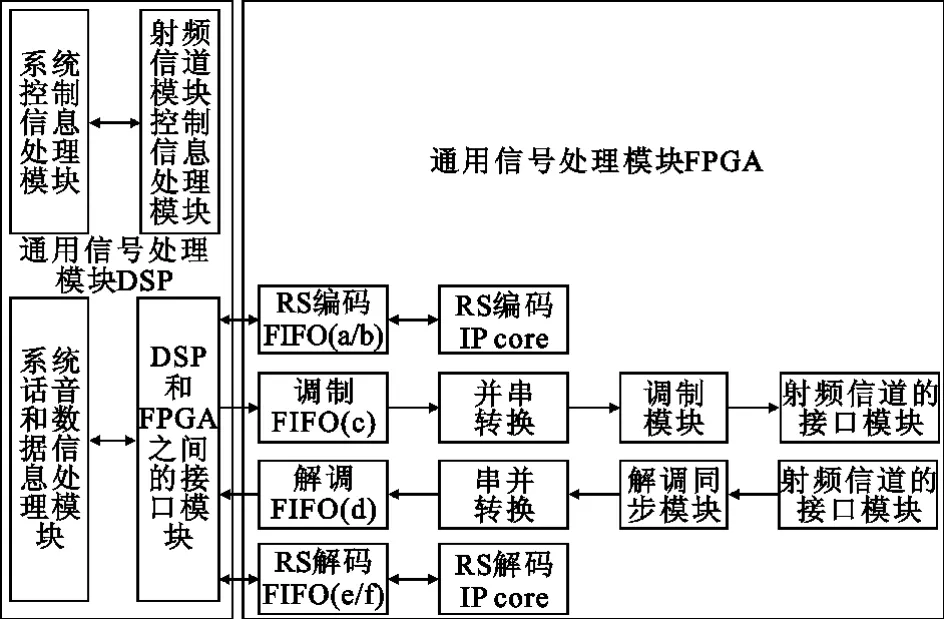

綜合化通信設備要完成上述功能,需要DSP和FPGA協同工作。換言之,其軟件開發工作包括兩部分:DSP程序和FPGA程序。DSP程序包括以下模塊:系統控制信息處理模塊、系統話音和數據信息處理模塊、DSP和FPGA之間的接口模塊(包括信源編碼和信源解碼)、射頻信道模塊控制信息處理模塊。FPGA程序包括以下模塊:FPGA和DSP的接口模塊(包括信源編碼和信源解碼)、信號調制模塊、信號解調模塊、FPGA和射頻信道的中頻接口模塊。

DSP和FPGA功能模塊劃分不僅充分體現了兩者各自的優點,而且巧妙地回避了兩者各自的缺點。DSP的優點在于采用C語言開發,周期短,靈活性高,開發速度快,移植性好,其調試方便是工程應用中最大的亮點,缺點在于不能并行處理信息。FPGA的優點在于速率高、進程并行執行、IP Core資源豐富且使用便捷,缺點在于開發速度相對較慢、難度高、調試不如DSP方便。

3 綜合化通信設備信號流程的實現

根據上節綜合化通信設備信號流程的設計,首先給出其實現的示意圖,如圖3所示。RS碼特別適合于糾正突發錯誤,是通信設備中最常使用的信源編碼方式[3],因此本文以RS碼作為例子描述信號流程。

圖3 綜合化通信設備信號流程實現示意圖Fig.3 Realization of signal flow in integrated communication equipment

如圖3所示,綜合化通信設備信號流程包括兩個信號流程,一個是控制信息流程,該信號流程雖然看似簡單明了,但在實際工程應用中,因為綜合化系統協議不統一,因此該部分是需要隨著系統更改并聯試的。另外一個流程即話音、數據信息處理流程。該流程實際體現的就是通信設備的信號處理流程。該流程看似復雜,但因為屬于底層物理通信,因此只要功能和性能穩定可靠,程序不需要隨著系統而更改。下面將著重描述話音、數據信息處理流程的實現。

3.1 綜合化通信設備信號處理發送流程的實現

綜合化通信設備中,DSP收到系統的話音信息,直接將話音信息通過DSP和FPGA之間的接口發送到FPGA的調制FIFO中。收到系統的數據信息,DSP則發送到FPGA的RS編碼FIFO(a)中,FPGA調用內部的IP core完成RS編碼處理后,再返回到RS編碼的FIFO(b)中;DSP從FIFO(b)中讀取RS編碼結果并發送到FPGA的調制FIFO(c)中。FPGA從調制FIFO(c)中讀取數據,進行并串轉換后,在調制模塊中進行調制處理,并通過射頻信道的接口模塊將中頻信號發送給射頻模塊。以上處理即完成了綜合化通信設備的信號處理發送流程。

3.2 綜合化通信設備信號處理接收流程的實現

FPGA首先通過射頻信道的接口模塊接收中頻信號,進行解調和同步處理,再進行串并轉換,將解調接收的數據發到解調FIFO(d)中。DSP從解調FIFO(d)中讀取數據,并區分是否需要作RS解碼處理。如果是話音數據,直接上報系統;如果是數據信息,將數據發送至 RS解碼FIFO(e)中,FPGA從FIFO(e)讀取數據,調用內部的IP core完成RS解碼處理后,再返回到RS解碼的FIFO(f)中。DSP從 RS解碼FIFO(f)中讀取數據信息,上報給系統。以上處理即完成了綜合化通信設備的信號處理接收流程。

4 信號流程的總結與分析

本文基于綜合化通信設備通用信號處理模塊給出的通信設備信號流程的設計,已應用于多個綜合化通信設備的工程。實際應用結果表明,該信號流程設計科學,實現容易,工程實現時便于問題定位,并且移植方便。

(1)信號流程清晰,易于實現

綜合化通信設備信號流程主要有兩個流程,即控制信息流程、話音和數據信息流程。控制信息流程按照系統要求處理即可。話音和數據信息流程清晰明了,DSP和FPGA實現容易。軟件開發初期,首先定義DSP和FPGA之間的接口,然后DSP和FPGA各自將程序編寫并調試。在系統聯試前,DSP和FPGA在通用信號處理板上,模擬完成話音和數據信息的中頻聯試。系統聯試時,主要完成控制和數據信息交互的聯試,以及話音和數據信息的射頻聯試。

(2)工程調試和聯試定位問題快速、準確

綜合化通信設備信號流程設計和實現,無論在通用信號處理板上調試中頻還是在系統中聯試,很大的優點體現在問題定位快速、準確。DSP在調試過程中,隨時可監測流程中間的數據是否正確,如FPGA的RS編解碼模塊功能是否正確、DSP接收或上報系統的話音或數據信息是否正確等。

(3)程序移植方便,通用性強

該流程還有一個優點就是程序移植方便、通用性強。在流程中,即使不同的通信設備模式,DSP程序只需針對該模式進行局部改動(例如幀數據結構的改動等)。FPGA程序的編解碼模塊、FIFO模塊,以及串并轉換模塊都是可以通用的。如果只是系統平臺不同,即從系統A移植到系統B時,DSP只需要更改跟系統的控制和數據信息交互處理,以及和FPGA之間的接口地址,FPGA只需要更改與DSP之間的接口地址,以及和射頻信道之間的接口。

[1]張建軍.輕型射頻傳感器系統高度綜合化設計[J].電訊技術,2010,50(12):1-3.ZHANG Jian-jun.High Integration Design of Light RF Sensor System[J].Telecommunication Engineering,2010,50(12):1-3.(in Chinese)

[2]楊小牛,樓才義,徐建良.軟件無線電原理與應用[M].北京:電子工業出版社,2001.YANG Xiao-niu,LOU Cai-yi,XU Jian-liang.The Principles and Applications of Soft Defined Radio[M].Beijing:Publishing House of Electronics Industry,2001.(in Chinese)

[3]曹志剛,錢亞生.現代通信原理[M].北京:清華大學出版社,1992:364-365.CAO Zhi-gang.Modern Communication Theory[M].Beijing:Tsinghua University Press,1992.(in Chinese)