基于NiosII的DDS數控信號源研究

溫錫懷,元澤懷

(肇慶學院 電子信息與機電工程學院,廣東 肇慶 526061)

基于NiosII的DDS數控信號源研究

溫錫懷,元澤懷

(肇慶學院 電子信息與機電工程學院,廣東 肇慶 526061)

針對傳統頻率合成技術結構復雜、成本高、體積大的缺點,采用SOPC片上系統的設計方法,實現了DDS數控信號源系統設計.該系統設計的DDS具有穩定度高、分辨率高、轉換速度快、抗干擾能力強等特點.以Nios II軟處理器為控制核心,系統的集成度高,易于維護和更新.

Nios II軟核;DDS;SOPC片上系統;信號源

目前,數字頻率合成技術被廣泛運用于生產與科研實踐中,該技術的發展也越來越迅速.它已從傳統的直接頻率合成技術、基于PLL的頻率合成技術,發展到現代的直接數字頻率合成技術(DDS),DDS具有集成度高、體積小、可輸出寬帶信號等特點.DDS信號的產生在數字域中實現,其精度高,容易實現調頻(FSK)、調相(PSK)及靈活的數字調制,因此DDS技術在信號源設計中被廣泛采用[1].

根據DDS的技術原理,筆者利用ALTERA公司Cyclone II器件芯片內部的大量邏輯資源,調用FPGA片上的ROM存儲單元,對任意波形數據進行存儲,將用累加器累加輸出的結果作為波形數據的地址進行尋址,輸出所需的波形,整個邏輯過程全用Verilog語言描述實現.它可根據波形種類、波形頻率的要求,對系統進行裁剪和配置.

Nios II處理器是世界上最通用的嵌入式處理器,它是可由用戶根據系統需要進行合理配置的軟處理器核[2].筆者通過嵌入Nios II軟處理器核,將其作為整個系統的控制核心,控制DDS模塊信號的輸出及LCD液晶的顯示等,利用SOPC片上系統的設計方法,可實現設計最優化.該系統具有穩定度和靈活性高、開發周期短、系統容易升級維護等特點.

1 系統各模塊的設計分析

1.1 Nios II軟核處理器

Nios II具有可定制和可以重新配置的特性.采用Nios II處理器,開發者將不會局限于預先制造的處理器技術,而是根據自己的標準定制處理器.他們可以通過Avalon交換架構調整系統性能,該架構是Altera的專有互聯技術,支持多種并行數據通道,實現數據大吞吐量的應用.利用SOPC Builder軟件中的用戶邏輯接口向導,生成自己的定制外設,并將其集成在DDS數控信號源系統中,組合實現現有處理器無法達到的嵌入式處理器配置.

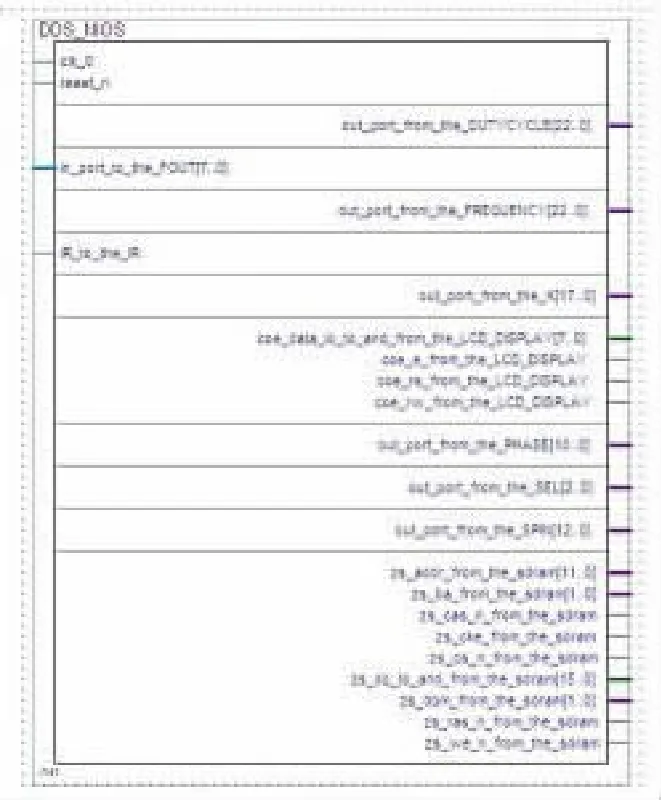

本設計的Nios II軟核處理器如圖1所示.

Nios II軟核處理器配置了LCD12864顯示器驅動核、SDRAM核和PIO核,PIO核用作控制信號的輸出,包括占空比DUTYCYCLE[22..0]、頻率FREQUENCY[22..0]、頻率 控 制 字K[17..0]、波 形 選 擇 SEL[2..0]和 相 位 SPIN[10..0]等 控 制信號[3].

1.2 DDS波形產生的模塊設計

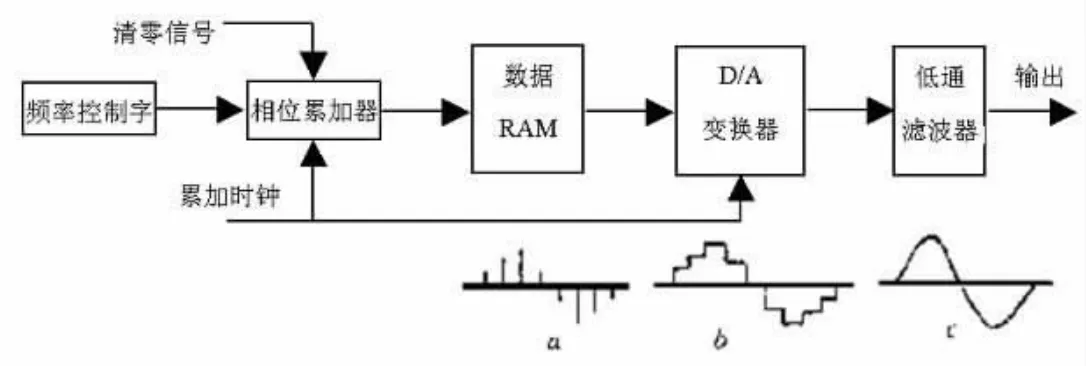

DDS模塊的原理:一個給定頻率的數字化波形能被以更高頻率的累加相位方式合成,不同的頻率對應于不同的相位累加步進量.在參考時鐘的推動下,相位累加器通過查找存儲器中的波形查找表中相應的地址,得到輸出頻率的離散化振幅值,經過D/A轉換及低通濾波,即可得到所需的模擬信號,其原理如圖2所示.

圖1 Nios II軟核處理器

圖2 DDS模塊內部原理框圖

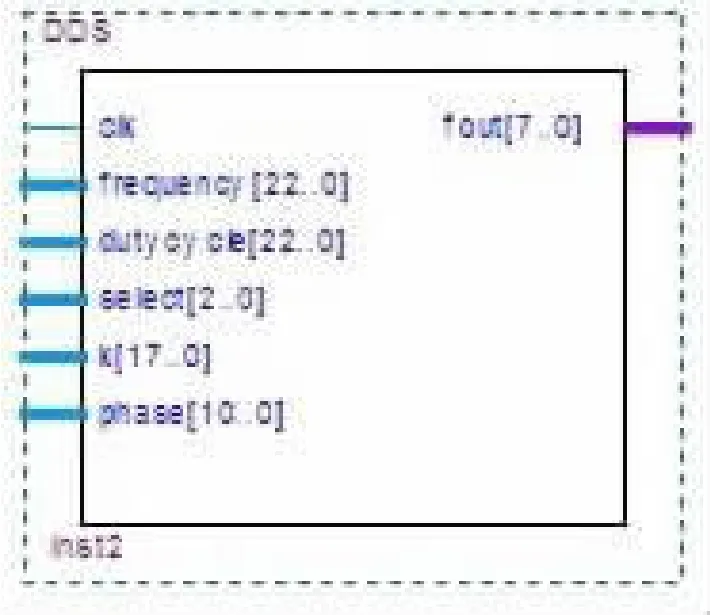

本系統的DDS模塊采用Verilog語言編寫[4],在Quartus II中封裝成元器件,在頂層圖形中進行調用,DDS模塊如圖2所示.其信號有頻率數據frequency[22..0]、占空比數據dutucycle[22..0]、波形選擇信號select[2..0]、頻率控制字[17..0]、相位數據phase[10..0]和波形輸出fout[7..0].

DDS模塊可以輸出正弦波、方波、三角波、鋸齒波、階梯波和矩形波等波形.頻率、相位和幅度可調,矩形波占空比可調,輸出頻率可按任意步進值進行頻率自動步進.DDS模塊中clk為系統50 MHz時鐘,對系統時鐘分頻后得到DDS的采樣時鐘fclk=8.333 333 MHz,累加器的位數N=23,頻率控制字為k,則輸出頻率

f=k×(fclk/223).

由于223=8 388 608,故在軟件里經過處理之后,輸入的控制字k才約等于輸出的頻率.

圖3 DDS模塊

1.3 D/A轉換模塊的設計

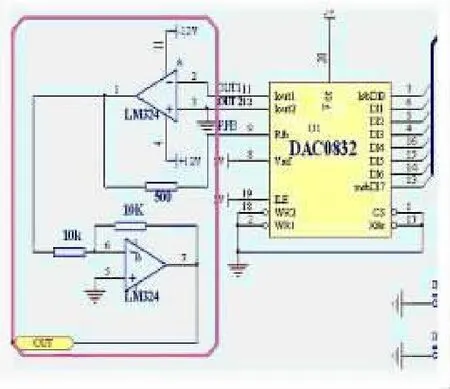

D/A轉換模塊采用DAC0832轉換芯片,該轉換芯片轉換位寬為8,電流建立時間為1 μs,電路如圖4所示.

DAC0832為電流型數模轉換器,需要通過轉換電路間接將電流信號轉換為電壓信號.轉換電路的第一級運放將DAC0832輸出的電流轉化為電壓形式;第二級運放對前一級運放輸出進行反相處理;最后得到輸出所需的電壓信號.

圖4 數模轉換電路

2 系統軟件程序設計分析

本系統程序利用Nios II IDE開發工具進行開發,采用AVALON總線協議,軟件利用中斷實現控制信息的接收和各種控制信息處理與數據的顯示[5].

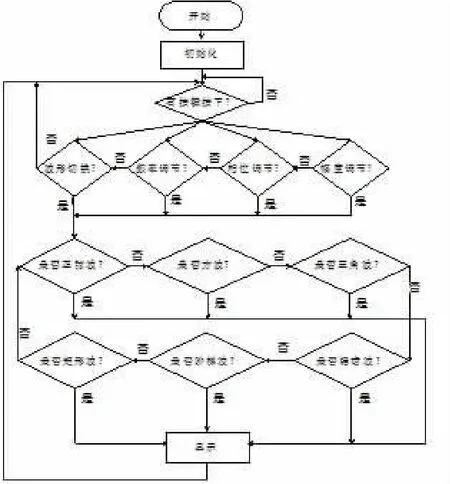

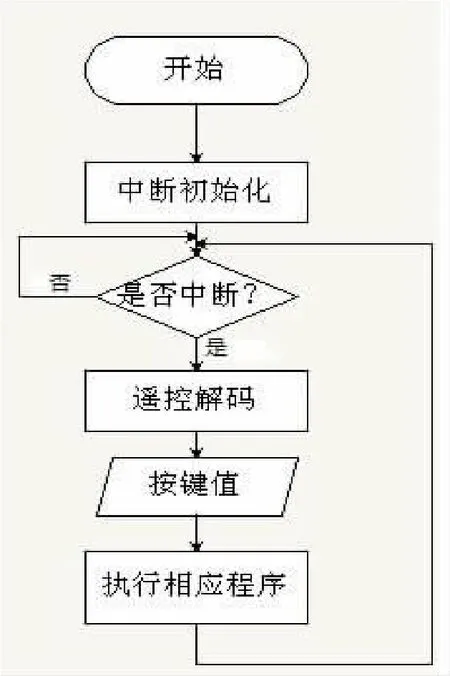

軟件實現的基本功能如下:波形頻率可由用戶設定任意值(在有效范圍內);波形頻率自動步進,步進值可以修改;波形相位可調;波形幅度可以設定任意值(在規定范圍內),同時可以步進調整,步進值為100 mV;矩形波占空比可調.系統程序流程圖及紅外遙控中斷子程序流程圖如圖5~6所示.

圖5 系統程序流程圖

圖6 紅外遙控中斷子程序流程圖

3 測試結果分析

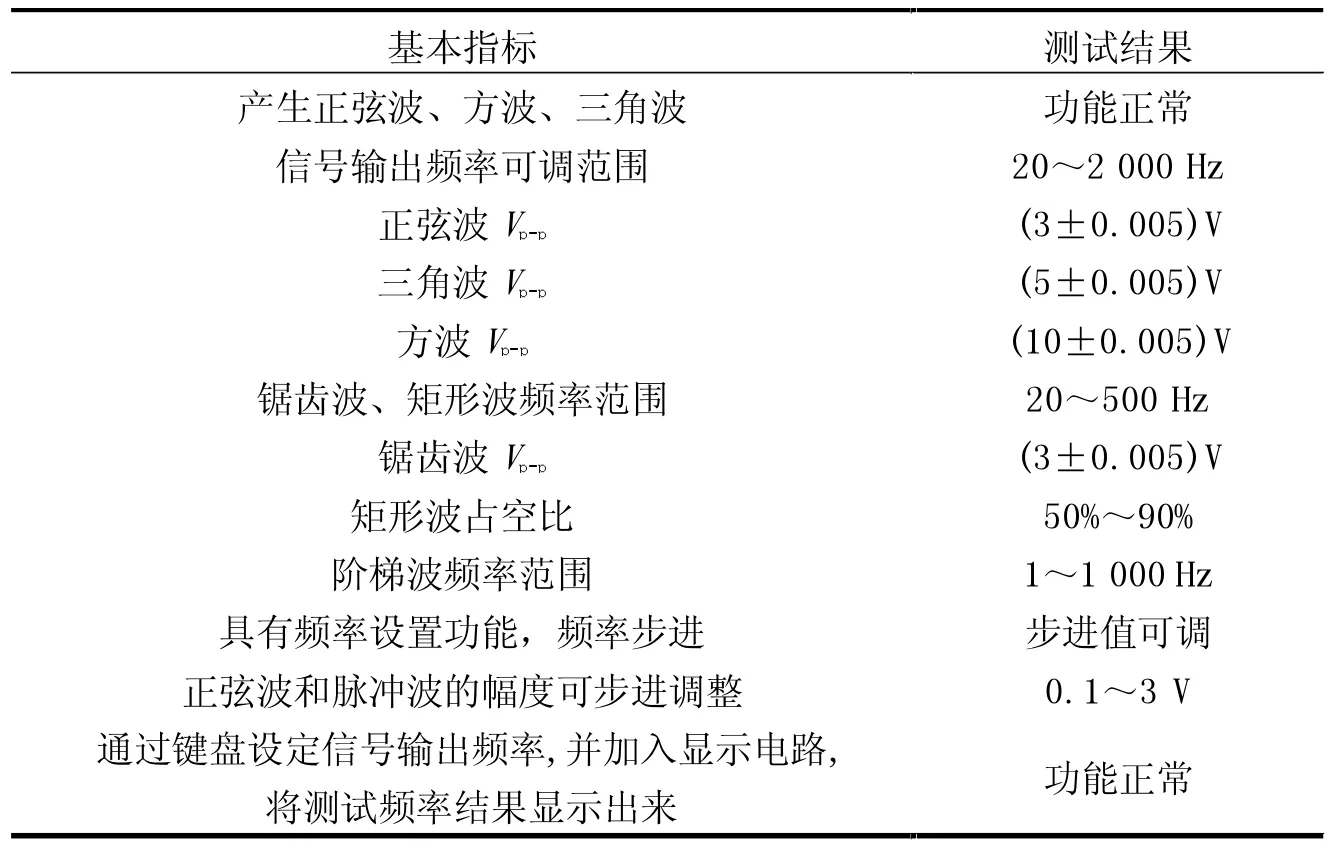

測試數據如表1所示.

表1 測試數據

由表1的測試結果可以看出,輸出信號頻率低的時候無失真,頻率穩定度高,誤差不到1%;當頻率增大到1 K Hz時,波形慢慢開始失真.分析其原因,主要是由D/A轉換部分引起的.因為DDS是在8.333 333 MHz的采樣時鐘頻率下采集數據并輸出的.由于本設計中DAC0832的轉換速率遠遠跟不上DDS產生的頻率,這導致在高頻時段因轉換速率的限制,丟掉了一些采樣點的數據,從而導致波形失真.本系統如采用高速的數模轉換器(如MAX542),可使輸出信號的頻率帶寬更高.

4 結語

本文設計的DDS信號源,采用SOPC片上系統的設計方法,大大提高了系統的性能和系統的集成度,降低了系統的開發成本.該系統軟硬件協同設計,開發周期短,產品更新換代快,該系統及其設計方法是現代電子技術發展的主流.

[1] 劉克剛,陳曦,王衛兵,等.復雜電子系統設計與實踐[M].北京:電子工業出版社,2010:69-77.

[2] 赫建國,倪德克,鄧燕,等.基于Nios內核的FPGA電路系統設計[M].北京:電子工業出版社,2010:71-90.

[3] 王金明.數字系統設計與Verilog HDL[M].北京:電子工業出版社,2009:120-149.

[4] 劉福奇,劉波.Verilog HDL應用程序設計[M].北京:電子工業出版社,2009:84-100.

[5] 湯書森,張北斗,安紅心,等.嵌入式FPGA/SOPC技術實驗與實踐教程[M].北京:清華大學出版社,2011:213-220.

(責任編輯:陳 靜)

Design of a DDS Digital Controlled Signal Generator Based on the Nios II

WEN Xihuai,YUAN Zehuai

(College of Electronic Information and Mechatronic Engineering,Zhaoqing University,Zhaoqing,Guangdong 526061,China)

For the weakness of high technical complexity,high cost and bulkiness of the traditional frequency synthesis method,a DDS numerical control signal generator has been implemented by applying the SOPC system on chip design methods.High stability,high resolution,fast high conversion rate and strong anti-interference capability are the basic characteristics of the DDS system.As the control core,Nios II soft-core processor has a high integration of the system which makes it easy to preserve and update the system.

Nios II soft-core;DDS;SOPC;signal generator

TP39

A

1009-8445(2012)05-0014-04