0.5μm CMOS后段平坦化工藝優化

寇春梅,李洪霞

(中國電子科技集團公司第58研究所,江蘇 無錫 214035)

1 背景介紹

在CMOS器件特征尺寸0.8μm以上時,通常采用2層金屬互連布線,其金屬互連線間隙大,通常采用淀積PECVD(等離子體增強化學氣相淀積)二氧化硅薄膜,旋涂光刻膠后進行Etchback(反腐蝕)的平坦化工藝,如圖1。

隨著CMOS器件特征尺寸減小到0.5μm以內,集成電路規模迅速提升,金屬內連線層數增加,金屬連線間隙繼續收縮,受限于PECVD SiO2工藝臺階覆蓋率50%(@aspect ratio=1:1)的限制[1],這些間隙變得難以完全填充,集成電路頂部形貌變得崎嶇不平。由于急劇增加的高度差使得金屬連線加工難度增加、可靠性降低,因此必須采用SOG(spin on glass旋涂玻璃)和Etchback的平坦化工藝(如圖2)降低集成電路頂部形貌的高度差,以得到合理的金屬互連線工藝。

圖1 Etchback的平坦化工藝

圖2 SOG和Etchback的平坦化工藝

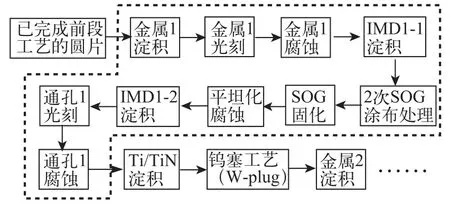

2 平坦化工藝流程

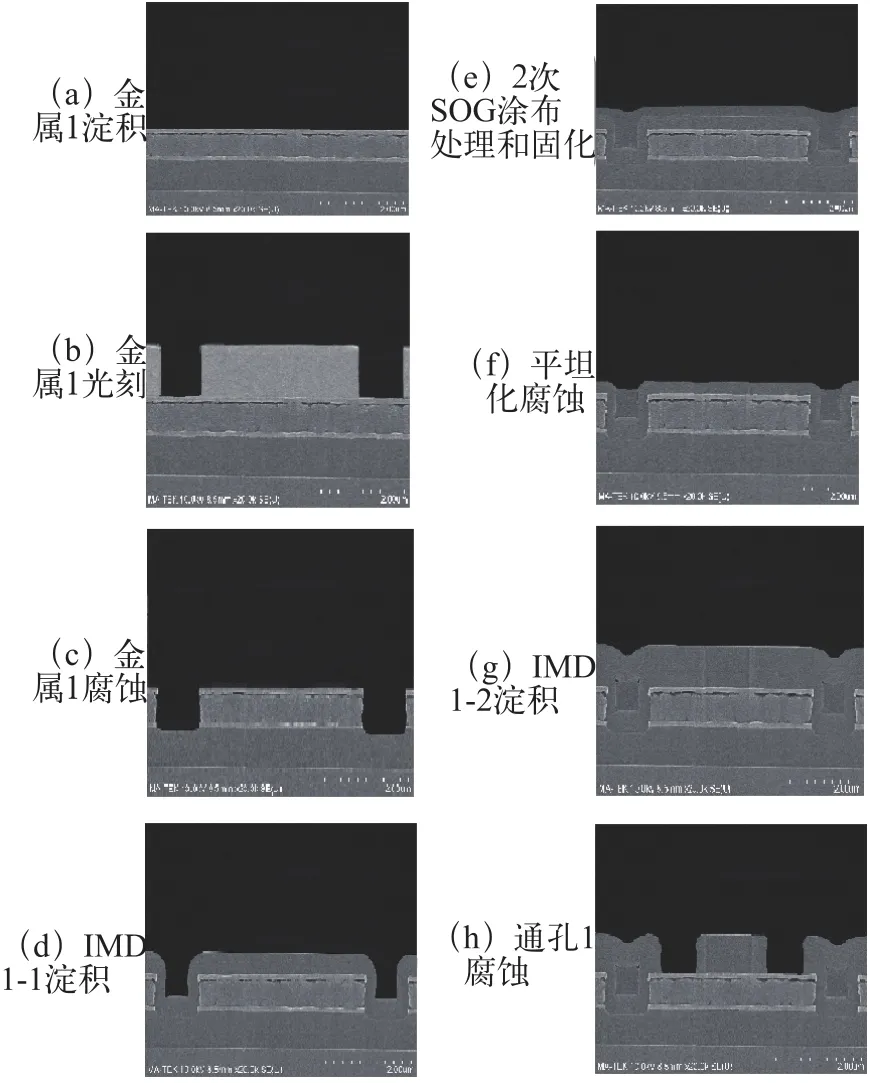

實驗中我們采用的流程如圖3所示。在已經完成前段CMOS器件制造的產品圓片上進行金屬1淀積,通過金屬1光刻和金屬1腐蝕完成第一層金屬層的圖形轉換,此時形成金屬連線層的臺階形貌,其縱寬比達到1:1;為了實現對于金屬臺階和間隙的完全填充,采用了SOG介質平坦化工藝,它主要包括IMD1-1淀積,2次SOG涂布和處理以及后續的SOG固化;接著進行SOG反腐蝕工藝,只留下間隙內和臺階處的SOG材料,金屬1臺階上的SOG材料全部被刻蝕干凈;再進行IMD1-2淀積完成金屬間介質平坦化工藝,后續進行鎢插塞(W-plug)工藝,接著重復上述從金屬1到鎢插塞工藝的循環來完成金屬2工藝,接著循環完成金屬3工藝,鈍化合金后形成完整工藝流程。

3 實驗過程

3.1 實驗一

圖3 平坦化工藝流程

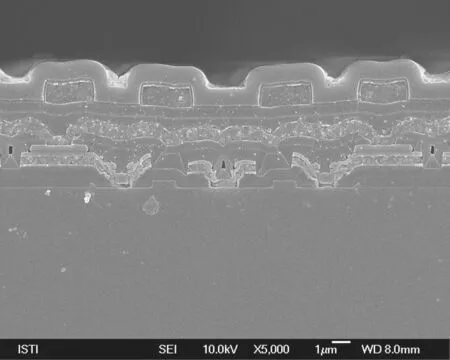

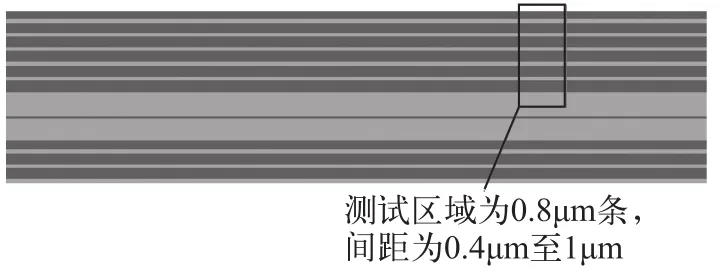

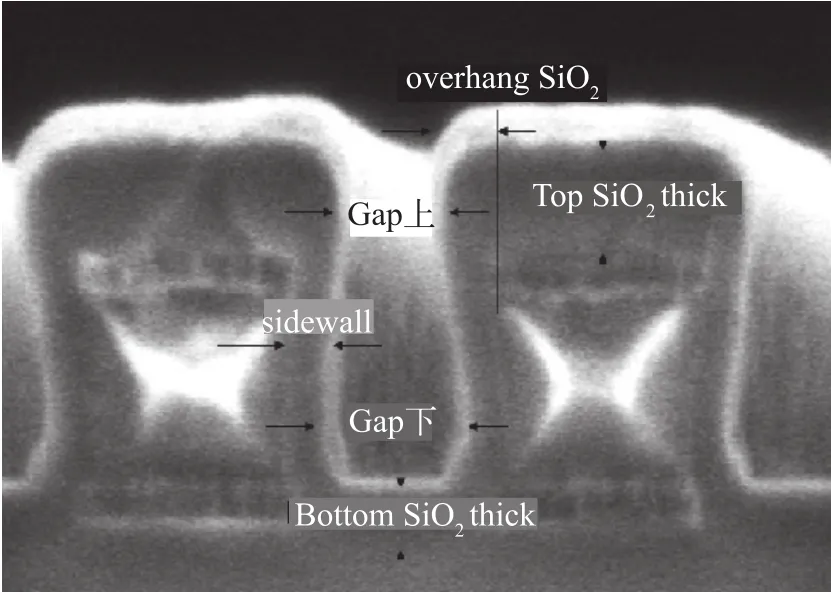

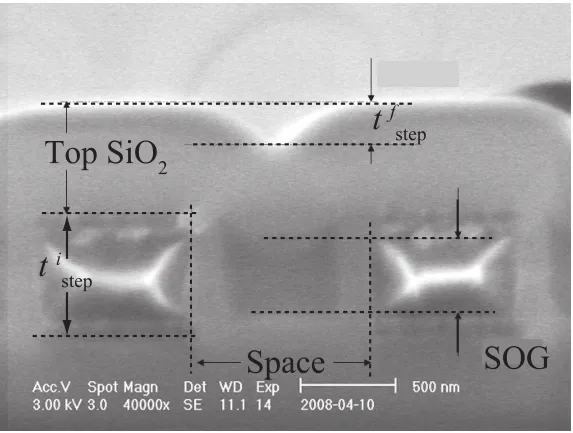

在進行平坦化工藝前,我們對模擬金屬臺階測試結構(如圖4)對IMD1-1的臺階覆蓋情況,以及IMD1-1的厚度對gap(金屬臺階的開口大小)的影響進行測試,通過滿足SOG最小間隙填充能力0.2μm來確定IMD1-1的厚度上限。圖5中采用0.4μm~1.0μm不同的間隙尺寸變化來確定最小設計尺寸0.7μm能夠滿足的IMD1-1厚度,并保證一定的工藝容寬度。實驗中采用IMD1-1的厚度為270nm、400nm和500nm三個厚度條件,SEM(掃描電子顯微鏡)數據測試如圖5所示,臺階上二氧化硅的高度(top SiO2)、金屬間距、Overhang-SiO2、GAP上、Bottom-SiO2以及sidewall-SiO2。

圖4 測試區域示意圖

圖5 測試剖面示意圖

3.2 實驗二

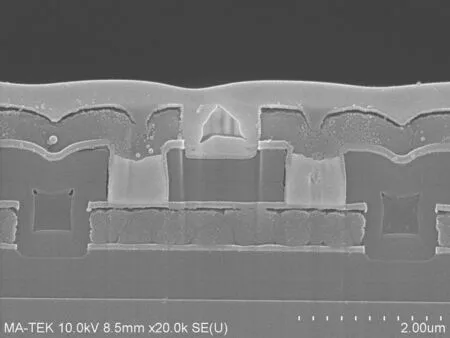

采用產品片對0.5μm CMOS后段平坦化逐步進行SEM剖面測試與分析,其主要工藝步驟如圖6中所示[2]。圓片完成器件層工藝后進行PMD(金屬前介質淀積),打開接觸孔后進行(a)金屬1淀積,(b)金屬1光刻,(c)金屬1腐蝕去膠,(d)IMD1-1淀積,(e)SOG涂布處理和固化,(f)Etchback平坦化腐蝕,(g)IMD1-2淀積,(h)通孔1光刻腐蝕,后續進行鎢插塞工藝和金屬2。金屬2以后的平坦化工藝與金屬1平坦化工藝相通。

圖6 平坦化工藝步驟

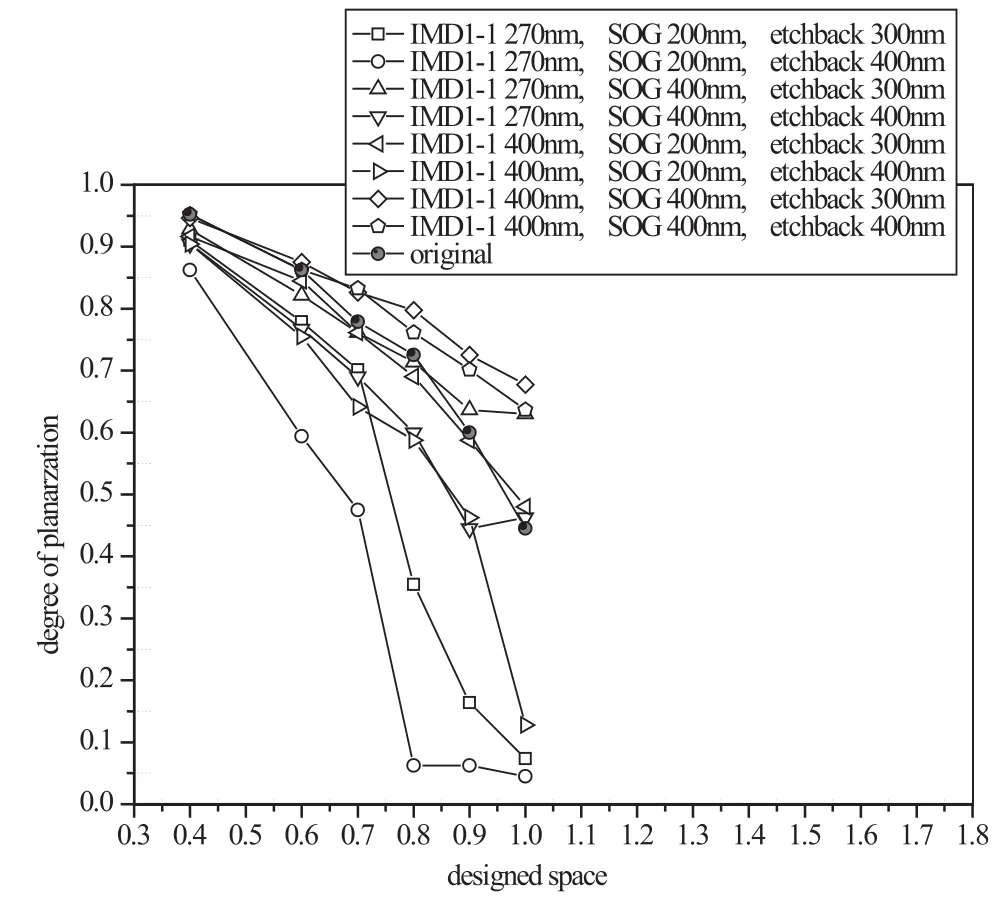

實驗按照DOE(實驗設計)進行3因素2水平[3]分析,3個因素為IMD1-1厚度 270nm和400nm,SOG涂布厚度200nm和400nm以及Etchback反腐蝕量300nm和400nm,它們的變化組合共8個條件。

4 實驗結果

實驗一中我們對金屬臺階的縱寬比與PECVD SiO2工藝的側壁覆蓋能力進行了評估,計算如公式1所示:

結果如圖7所示(x軸表示縱寬比,y軸表示側壁覆蓋率百分比),在縱寬比為1:1時(圖7中x等于1),IMD1-1的側壁覆蓋能力為40%~50%,與應用材料公司提供的資料相同,其變化趨勢隨著縱寬比的降低,側壁覆蓋能力提高,反之則減少。產品電路中采用小于等于1:1的規則,能夠保證IMD1-1的側壁覆蓋能力大于40%。

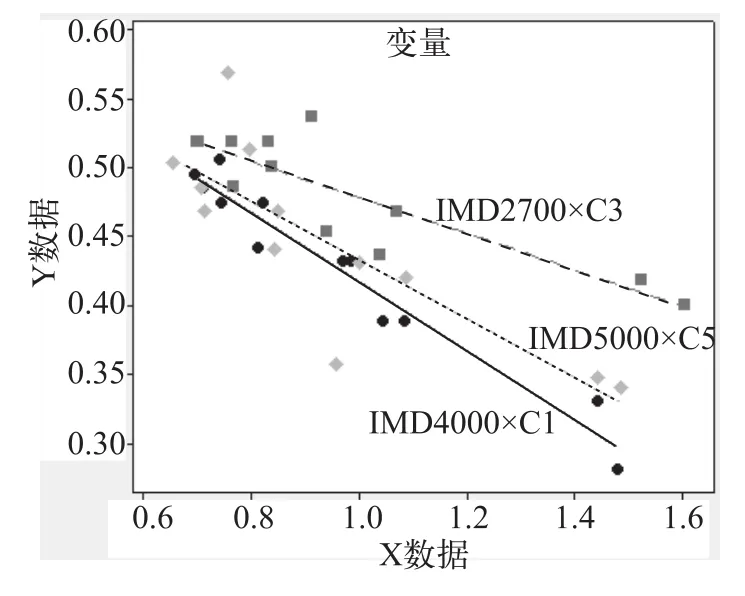

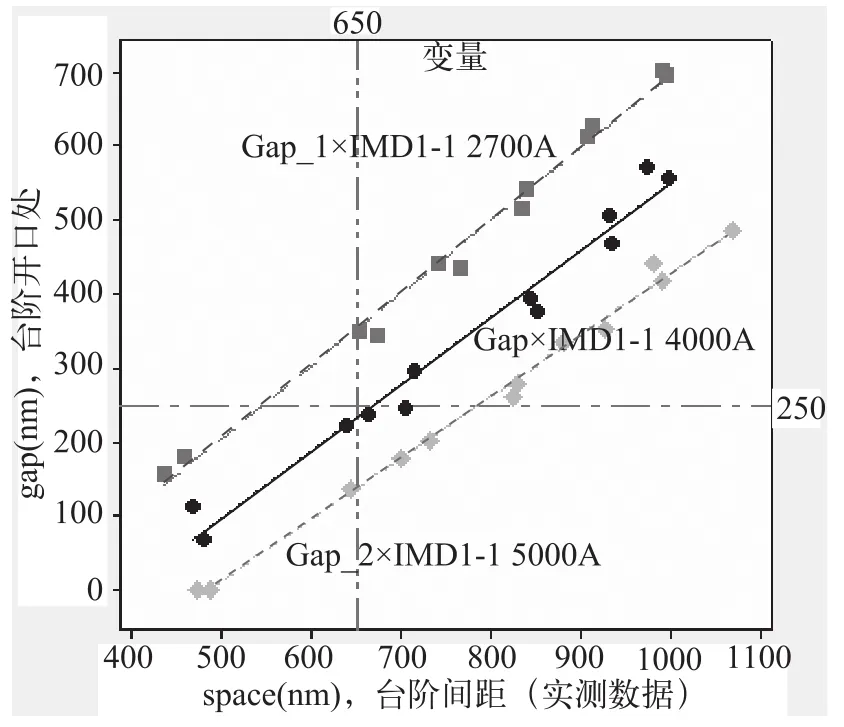

將數據按照金屬間距space與GAP建立散點圖,同時進行線性擬合,將三個IMD1-1的厚度結果顯示在圖8上。實驗數據表明:當IMD1-1的厚度增加時,GAP減少;而space變大時,GAP增加。當我們將GAP的安全限設置在0.25μm(為SOG的填充保留一些容寬)、金屬條間距在0.65μm(加工后尺寸)時,IMD1-1不能大于400nm。當0.5μm金屬間距設計為0.7μm尺寸,實際加工會存在偏差,取下限-10%為0.63μm,能夠滿足GAP大于0.2的要求。因此IMD1-1的厚度不能大于400nm。

圖7 PECVD臺階覆蓋與縱寬比的關系

圖8 不同IMD1-1厚度下金屬間距與GAP的關系

實驗二中為評價平坦化的優化效果我們引入了平坦化因子β,定量考察臺階高度下降的程度,如式(2)所示[4]:

其測試位置如圖9所示,其中tistep表示平坦化工藝前的臺階高度,tfstep表示平坦化工藝后的臺階高度,因此在完全平坦化的工藝中,平坦化因子為1,而沒有平坦化效果則因子為0。

圖9 平坦化實驗測試結構圖

平坦化因子的結果如圖10所示,x軸表示金屬條間距,y軸為平坦化因子。圖中實心圓圈original表示原平坦化工藝的效果,從圖上的變化趨勢表明:總體上IMD1-1厚度增加,SOG涂布厚度增加,etchback反腐蝕減少有利于改善平坦化效果。菱形采用IMD1-1 400nm、SOG涂布400nm、Etchback反腐蝕量300nm的工藝條件平坦化效果好于其他條件。

圖10 平坦化因子結果

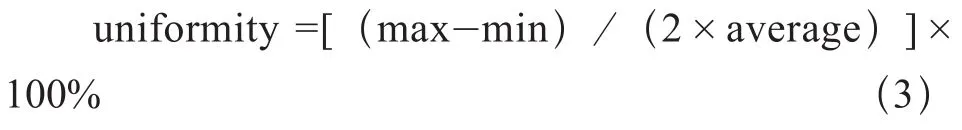

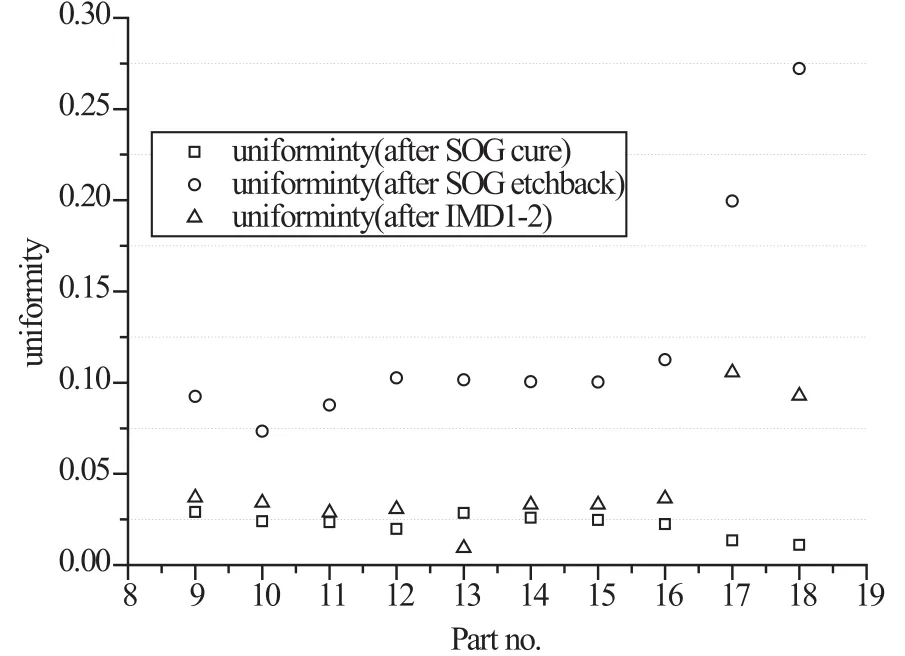

為評價平坦化工藝片內均勻性改善情況,我們引入了5點測試片內均勻性計算公式:

當uniformity數值越小表示片內均勻性越好,這也是希望得到的結果。

圖11 Uniformity數值與片內均勻性變化關系圖

5 結論

文中通過對0.5μm CMOS后段平坦化工藝流程相關工序的變化研究,從實驗角度對平坦化工藝進行了3因素2水平實驗設計,實現結果表明,當IMD1-1淀積厚度變大時,平坦化因子β趨向于大(越大平坦化效果越好),同時平坦化均勻性變好;當SOG涂布采用2次涂布方式時,平坦化效果和平坦化均勻性好;當Etchback量變小時,平坦化效果和平坦化均勻性好。改進后采用IMD1-1厚度為400nm,SOG涂布2次、每次200nm,Etchback 300nm的方式將原有的平坦化效果從70%提高到85%。同時發現金屬間距也是影響平坦化效果的重要因素。對于0.5μm CMOS工藝,其最小間距是固定的,文中沒有對此展開討論。

總體上平坦化工藝受到多個因素影響,需要針對上述3個主要因素合理控制這些因素的變化范圍,得到良好的平坦化效果,為后續的金屬層淀積和通孔工藝打下良好基礎。

致謝:

衷心感謝肖志強、高向東、洪根深、徐靜給我的指導和幫助以及陳海峰、吳曉鶇、李俊、張世權的大力協助。

[1]Robert F.Pierret.Semiconductor Device Fundamentals[M].ISBN:0201543931.

[2]Alan Hastings.The Art of Analog Layout,Second Edition[M].ISBN:013464108.

[3]G.E.P.Box,W.G.Hunter,J.S.Hunter.Statistics for Experimenters.An Introduction to Design,Data Analysis,and Model Building[M].New York:John Wiley & Sons.

[4]Stanley Wolf,Richard N.Tauber Silicon Rrocessing For The VLSI ERA VOLUME1 and VOLUME 2[M].California Sunset Beach.1990.