一種DSP程序控制結構的分析

薛海衛,徐新宇,符士華

(中國電子科技集團公司第58研究所,江蘇 無錫 214035)

1 引言

數字信號處理器DSP廣泛應用于現代通信、信息處理、自動控制等領域中,通過指令程序,DSP能實現濾波、快速傅里葉變換等各種算法,是現代信號處理的關鍵器件之一。DSP通常由CPU、程序控制、尋址地址、存儲器、外設等邏輯部件組成,其中DSP的程序控制實現程序地址的產生與加載、各種指令的執行控制等操作。DSP程序控制調用程序計數器、堆棧、重復計數器等邏輯部件,通過程序地址的加載流程,使得指令能夠正確順利地執行。鑒于程序控制在DSP中起重要的指揮控制作用,弄清DSP程序控制結構對研究DSP性能架構具有重要意義。本文通過分析DSP程序控制的流程與實現方式,從而揭示了程序控制的核心——指令執行中各程序地址的加載關系,為設計DSP程序控制邏輯提供一種參考方法。

2 DSP程序控制結構分析

DSP程序的執行要進行尋址、取址、讀寫各種存儲設備等多項操作,DSP程序除順序執行外還可以實現多種復雜的執行方式,如跳轉、子程序調用返回、循環、程序塊執行等。程序可實現的操作種類越多,程序執行越靈活,可操作性和易開發性越好,則DSP的功能越強大、開發效率越高。程序控制是DSP的指揮中樞和控制核心,它控制了所有程序的執行進程。不同的執行指令導致不同的程序地址加載方式。DSP的程序控制邏輯一般由程序計數器、硬堆棧、程序重復執行計數器和狀態控制寄存器等邏輯電路組成。

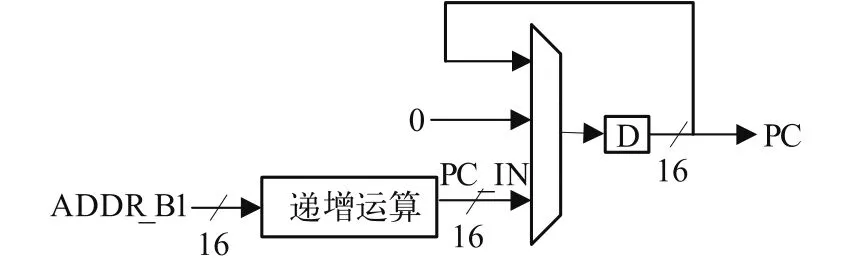

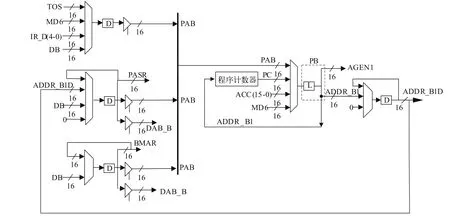

2.1 程序計數器PC

程序計數器PC實際上是一個加一計數器,當程序順序執行時,計數器執行加一遞增運算。程序計數器PC由遞增運算、選擇器和D觸發器組成,其內部邏輯如圖1所示。16位地址總線ADDR_B1作為PC的輸入,經遞增運算后,通過選擇器和寄存器最后輸出16位的PC地址。

圖1 PC邏輯結構圖

PC的遞增運算實現遞增或保持操作,16位輸入地址ADDR_B1經過遞增運算后生成輸出地址PC_IN,當遞增控制信號B為1時,PC_IN=ADDR_B1+1;當信號B為0時,PC_IN=ADDR_B1。當PC復位時,選擇器選0輸入;當PC正常工作時,選擇器選PC_IN作為輸入。

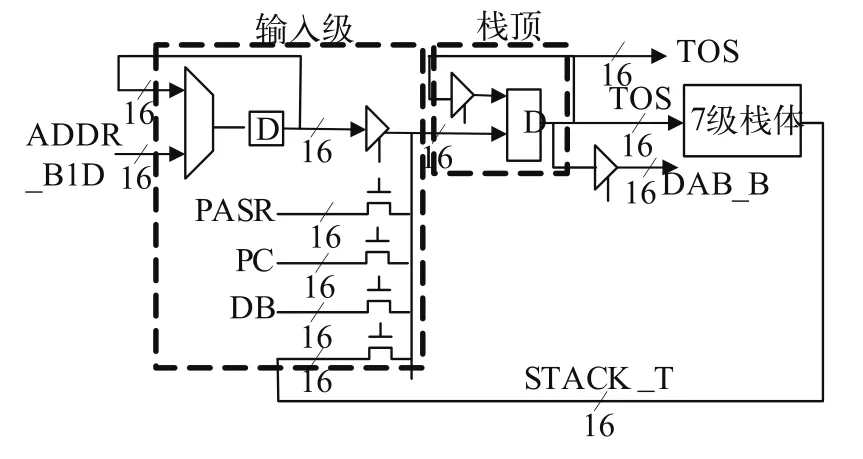

2.2 堆棧STACK

堆棧在子程序的調用和返回時用于暫存地址,典型DSP堆棧深度為8級,可以把8個不同的地址存入堆棧中,也即最多可有8個不同的子程序入口。PUSH和POP指令實現壓棧和彈棧操作。堆棧分為輸入級、棧頂和7級棧體,堆棧的輸入級為五選一的選擇器,其輸入為地址總線ADDR_B1D、PASR、PC、數據總線DB和棧體反饋STACK_T,棧頂TOS經三態門連接到DAB_B總線上。堆棧可以把地址ADDR_B1D、PASR、PC和DB、TOS等數據壓入棧體,堆棧的結構圖如圖2所示。

圖2 堆棧結構圖

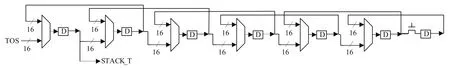

棧體由二選一選擇器和D觸發器構成,深度為7級,加上棧頂深度共8級。棧體的輸入為16位的TOS,輸出為16位STACK_T,二選一選擇器選擇壓棧還是彈棧操作,7級棧體的結構圖如圖3所示。

圖3 7級棧體結構圖

堆棧的操作過程如下:壓棧操作時數據經輸入級壓入棧頂TOS,后由TOS通過選擇器的第二路逐級壓入棧體;彈棧操作時數據從后一級寄存器通過前一級選擇器的第一路彈入前一級的寄存器中,逐級彈出最后經STACK_T從棧頂輸出。

2.3 程序重復執行邏輯

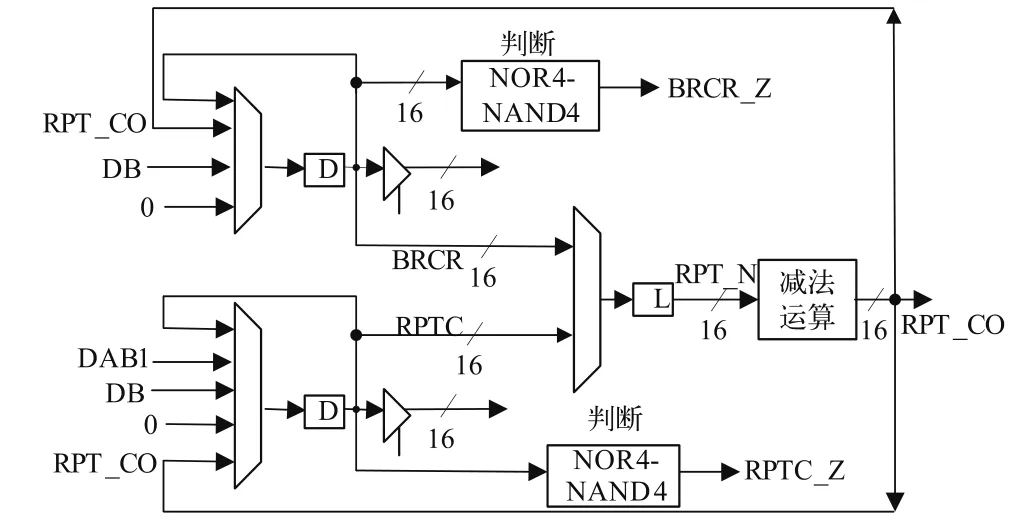

通常DSP可以用程序重復指令實現指令的重復執行,指令重復執行包括單指令的重復執行和指令塊重復執行。單指令重復執行用RPT或RPTZ指令,指令塊重復執行用RPTB指令。相關的16位寄存器有重復計數寄存器RPTC、程序塊重復開始結束寄存器PASR、PAER和程序塊重復計數寄存器BRCR。單指令重復執行時,RPT或RPTZ指令把需要重復執行的數值N載入RPTC寄存器,指令每執行一次,RPTC中的值就減一,直到RPTC中的值達到0為止。選擇器選擇RPTC或BRCR的值給運算單元進行減法運算,當用RPT或RPTZ指令時選擇RPTC值,當用RPTB指令時選擇BRCR值。通過減一計數實現程序重復執行的邏輯功能,如圖4所示。

減法運算得到的16位結果RPT_CO根據不同的選擇返回給RPTC和BRCR寄存器,RPTC和BRCR根據判斷邏輯決定是否再執行減法運算。當RPTC或BRCR中的值減到0時,判斷邏輯的輸出RPTC_Z或BRCR_Z都為0,否則輸出為1。當RPTC_Z或BRCR_Z為0時減法器停止運算,當RPTC_Z或BRCR_Z為1時,減法器繼續運算。

重復計數減法功能實現減一運算,其結構與程序計數器PC的遞增運算相似,每一組減法運算單元AS由傳輸置位邏輯、同或運算邏輯和控制傳輸邏輯組成。重復計數器進行遞減運算,計數器輸入為16位的RPT_N,輸出為16位的RPT_CO。當遞減控制信號B為1時, RPT_CO=RPT_N-1;當B為0時,RPT_CO=RPT_N。

圖4 指令重復執行邏輯

當程序塊需重復執行N+1次時,用RPTB指令把塊重復值N加載入BRCR寄存器中。當執行RPTB指令時,BRAF位置位把緊跟RPTB的下一指令地址載入程序地址開始寄存器PASR,把RPTB指令中的長立即數載入程序地址結束寄存器PAER。塊重復執行過程如下:PAER與PC作比較,如兩者相等則BRCR與0比較,若BRCR大于0,則BRCR減一,PASR載入PC,重新開始循環;若PAER與PC不等,則繼續執行直到塊的最后一條指令。

16位PAER與PC比較,若相等則COMP為0,再判斷BRCR是否達到0;若不同則COMP為1,PC繼續遞加。

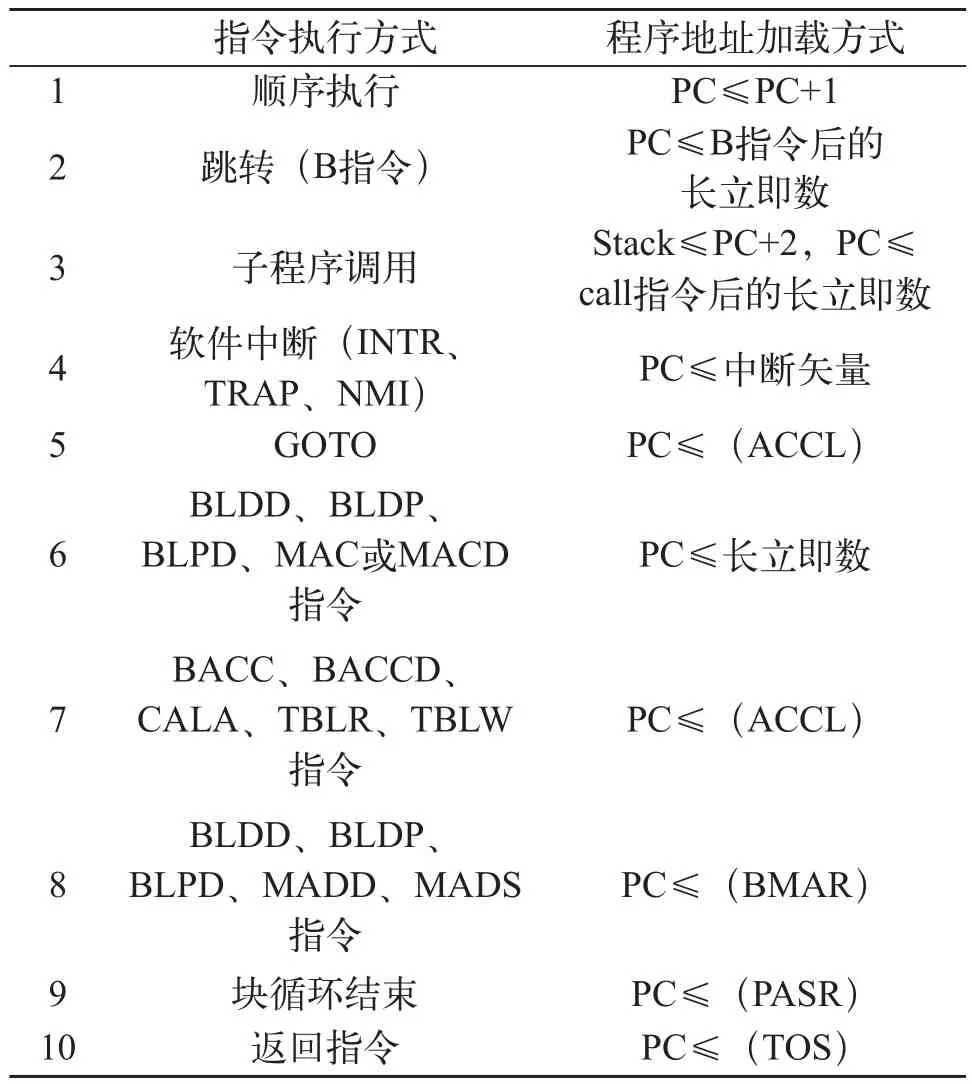

2.4 程序地址的加載方式

根據不同的指令執行方式,程序地址PC的載入方式也不同,PC加載方式如表1。通過程序地址總線PAB來尋址程序存儲器,被尋址的指令裝入指令寄存器IR中。

根據表1,程序地址的輸入有多種來源,包括立即數、中斷矢量、寄存器ACCL、BMAR、PASR和堆棧頂TOS等,這就決定了地址加載硬件的結構是多選擇器結合總線的方式。

程序地址生成與加載邏輯如圖5所示,為避免多地址沖突,3個帶選擇的觸發器輸出經三態門與程序地址總線PAB相連。在PAB總線的左側,第一個地址加載源是堆棧頂TOS、數據總線DB、存儲器的輸出MD6和IR<4:0>,這些輸入對應返回指令RET、RETC、程序塊移指令BLDD、BLDP、BLPD、乘加指令MAC或MACD、子程序調用等指令執行操作;第二個地址加載源是PASR,其值通過ADDR_B1D或數據總線DB加載,對應塊循環結束操作;第三個地址加載源是BMAR,其值通過DB總線加載,對應BLDD、BLDP、BLPD、MADD、MADS指令操作。上述3種輸出通過三態門連接到PAB總線上,作為PAB的來源。

表1 程序地址加載方式

在PAB總線的右側,當執行GOTO和BACC、BACCD、CALA、TBLR、TBLW指令時,ACC<15:0>通過稱之為程序總線鎖存器PB賦給地址總線ADDR_B1。ADDR_B1的值也可以來自總線PAB、PC和存儲器輸出MD6,而ADDR_B1反饋給程序計數器作為PC輸入。ADDR_B1經觸發器鎖存后的地址ADDR_B1D反饋回PASR寄存器,作為PASR的輸入,當執行RPTB指令時ADDR_B1D載入PASR。這樣根據不同的指令,通過PAB總線選擇不同的地址寄存器給程序總線ADDR_B1,ADDR_B1經程序計數器PC運算后把下一個操作的地址值反饋給指定的寄存器單元。這樣,程序地址生成加載邏輯實現了所有程序控制所需的地址產生和載入方式。

3 程序控制中遞增遞減運算分析

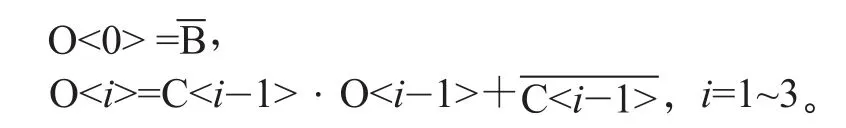

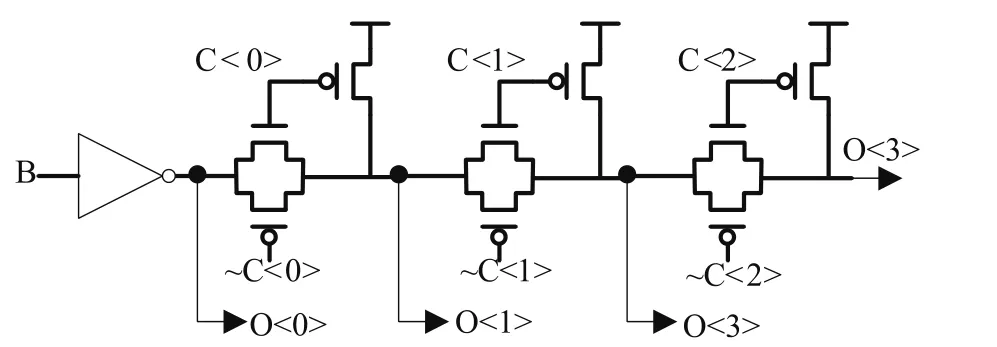

程序控制中的兩個關鍵運算部件——程序計數器和重復計數器——其遞增(加一)、遞減(減一)運算邏輯結構相同,遞增遞減運算邏輯把16位的輸入分成4組,每組4位,每組的運算單元結構相同,我們稱之為Arithmetic Slice(AS)。每一組AS由傳輸置位邏輯、同或運算邏輯及控制傳輸邏輯構成,現以AS的低4位為例說明。傳輸置位邏輯如圖6所示,遞增保持控制信號B通過內部控制信號C<2:0>控制的傳輸門傳到輸出O<1>、O<2>和O<3>。當C<2:0>各位都為1時各級傳輸門打開,O<i>=O<i-1>;當C<2:0>各位都為0時傳輸門關閉,上拉P管打開使O<3>、O<2>、O<1>置位為1,O<0>恒為。O<3:0>的邏輯表達式如下:

圖5 程序地址加載邏輯圖

圖6 傳輸置位邏輯

當C<3:0>同時為1時Z=B,當C<3:0>有一位為0時Z=0。

4 遞增運算仿真結果

用Hspice對遞增運算進行仿真,仿真結果如圖7所示,圖中ADDR_B1為遞增輸入,PC_IN為遞增輸出。以低4位運算為例,從圖中可以看出:輸入從0開始遞增,當輸入為00002時對應輸出為00012、輸入00012時對應輸出00102、輸入00102對應輸出00112,以此類推,當輸入為11112時輸出為00002,控制傳輸位為1。輸入到輸出間延時為0.5ns。根據公式,當ADDR_B1<1:0>為11即輸入為3時O<2>為0,其他輸入時O<2>都為1;同樣只有當ADDR_B1<2:0>為111即輸入為7時O<3>為0,其他輸入時O<3>都為1。當ADDR_B1<0>為0時輸出PC_IN<0>為1;當ADDR_B1<0>為1時輸出PC_IN<1>為1、 PC_IN<0>為0;當ADDR_B1<1>和ADDR_B1<0>都為1時輸出PC_IN<2>為1;當ADDR_B1<2>、ADDR_B1<1>和ADDR_B1<0>都為1時輸出PC_IN<3>為1。這樣輸入ADDR_B1每計數到1時,輸出PC_IN<1>翻轉一下;輸入ADDR_B1每計數到3時,輸出PC_IN<2>翻轉一下;輸入ADDR_B1每計數到7時,輸出PC_IN<3>翻轉一下,實現每次輸出隨輸入的變化而自動加一遞增。

圖7 遞增仿真結果圖

5 結論

通過對DSP的程序計數器、堆棧、程序重復邏輯和程序地址加載邏輯等的分析,弄清了程序順序執行與重復執行的流程,對不同指令執行方式、程序加載方式作了詳細闡述。分析了程序控制中遞增遞減運算部件的邏輯實現,明確了DSP的程序控制結構及其實現方式。本文通過分析DSP程序控制流程及其實現方式,從而揭示了指令執行中程序地址加載的各種關系,對弄清DSP程序控制結構、研究DSP架構具有參考意義。

[1]TMS320C5X DIGITAL SIGNAL PROCESSORS USER’S GUIDE TI. 1998. 80-115.

[2]TI著,徐科軍,等譯.TMS320LF/LC24系列DSP的CPU與外設[M]. 北京:清華大學出版社,2004. 32-41.

[3]江思敏,等編著. TMS320LF240X DSP硬件開發教程[M].北京:機械工業出版社.2003. 12-49.

[4]TMS320C54X DSP Reference Set Volume1:CPU and Peripherals. TI. 2001.145-167.