采用CPCI總線的通用高速數傳接收機

劉進軍

(中國西南電子技術研究所,成都 610036)

1 引 言

近年來,隨著高速數傳技術應用領域的不斷拓展,高速數傳技術不僅廣泛應用于偵察衛星、軍事衛星、資源探測衛星、高分辨率對地觀測衛星等航天器中,而且航空飛行器如預警機、高空偵察機、無人機等,以及臨近空間飛行器也紛紛增加了數據獲取功能,需支持高速數據傳輸或海量存儲能力。在高速數傳系統中,高速解調設備是核心。目前,國內主流的高速解調設備處理能力均低于300 Mbit/s數據傳輸速率,已不能滿足日益增長的數據傳輸速率需求。隨著系統支持數據傳輸速率的提高,對接收機的電路設計、解調性能等提出了挑戰,高性能的高速解調接收機市場需求迫切。

本文采用軟件無線電設計思想,對高數數傳接收機軟硬件技術進行了深入研究,通過硬件模塊化設計和軟件動態加載與升級技術,提高了接收機設計靈活性和通用性。

2 接收機實現原理

通常,高速數傳接收機可采用模擬、模數混合以及全數字3種實現方式。模擬實現方式存在設備復雜、實現難度大以及通道一致性較差等缺陷,影響高速數據解調性能;而模數混合和全數字實現方式具有通道一致性好、設計靈活等優點,是一種較好的設計方案。

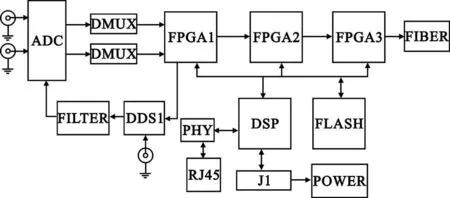

接收機具備高速數據處理能力,其電路器件選擇和電路設計需滿足高速數傳要求,接收機主要由超高速模數變換器(ADC)、直接數字合成器(DDS)和大規模可編程器(如FPGA、DSP等)組成,實現原理框圖如圖1所示。

圖1 高速數傳接收機原理框圖Fig.1 The block diagram of high-rate data transmission receiver architecture

模擬基帶信號或中頻信號經信號調理后,由ADC進行采樣變換,完成信號離散處理,由FPGA1控制DDS的頻率控制寄存器,產生相位連續的正弦波信號作為采樣時鐘。采樣后的離散差分數據通過DMUX降速后,送入FPGA1中進行載波恢復、位同步信息提取、匹配濾波、信道均衡等信號處理[1]后,將數據送到FPGA2中完成譯碼,包括維特比譯碼、幀同步、RS譯碼、Turbo譯碼、LDPC譯碼等。譯碼后的數據通過FPGA3進行數據打包及協議處理,由高速光纖或10/100/1 000Mbit/s以太網接口輸出到數據記錄模塊或遠控中心。接收機各模塊之間的通信、控制命令、上報狀態和數據均采用PCI接口電路,提高了系統設計一致性。

3 主要功能設計

3.1 模擬前端設置

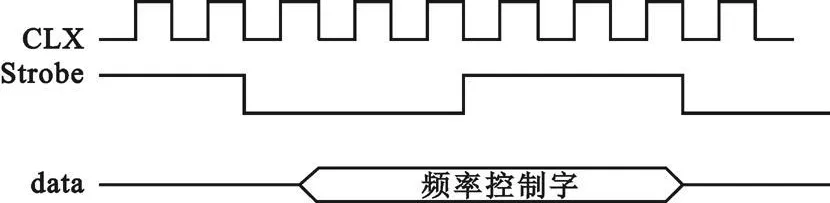

高速數傳接收機模擬前端可配置為模數混合和全數字兩種接收機結構。接收機工作在模擬接收模式,ADC采用雙通道工作,同步采樣I/Q兩路模擬信號;接收機工作在全數字接收模式,ADC采用單通道工作,對輸入的中頻信號進行采樣。為適應兩種工作模式,高速數傳接收機需兼容提供不同采樣時鐘,采樣時鐘由DSP控制FPGA1,通過FPGA1構建DDS產生,DDS控制時序如圖2所示。

圖2 DDS控制時序圖Fig.2 DDS control logic diagram

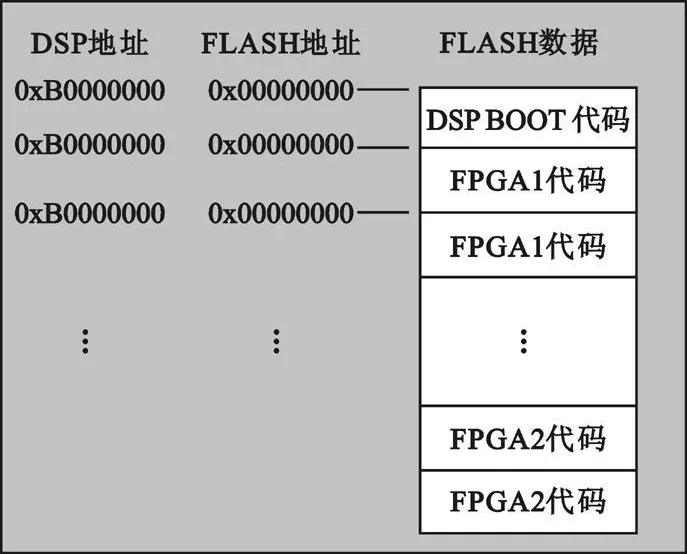

3.2 軟件動態加載

為滿足接收機通用性設計需求,FPGA1主要功能設計為解調,實現載波恢復、位同步信息提取、匹配濾波、信道均衡等功能。FPGA2主要功能設計為譯碼,包括維特比譯碼、幀同步、RS譯碼、Turbo譯碼、LDPC譯碼等。在不同應用環境下,解調和譯碼程序需要刷新,因此,設計FPGA具有動態加載或遠程更新功能。對FPGA1和FPGA2程序進行預先規劃,存放于超大容量FLASH地址單元中,通過系統命令選擇對應的功能模式。針對新增加功能,可通過遠程更新,利用網絡將程序傳至系統模塊中,再由系統將程序寫入到未用的FLASH空間,寫完后啟動代碼即實現新功能。DSP外部尋址空間是4 Mbyte,FLASH容量為256Mbyte,尋址空間與容量地址不匹配,因此,通過FPGA3控制FLASH高位地址,DSP的BOOT和程序代碼放置于FLASH最低段,按照12Mbyte空間分配FPGA1和 FPGA2的程序代碼。FLASH存儲空間分配如圖3所示。

圖3 DSP和FPGA1、FPGA2程序代碼分配圖Fig.3 Distribution of DSP,FPGA1 and FPGA2 programs

為縮短FPGA1和FPGA2程序加載時間,可預先將數據寫入FLASH中,主要有兩種寫入法:一種是主機通過PCI總線將代碼寫入DSP,再由DSP寫入FLASH中;另一種是由DSP直接讀FPGA程序文件,將代碼寫入FLASH中。FPGA進行動態加載時,直接通過主機選擇對應功能版本,由DSP將FLASH中代碼直接寫入FPGA中。

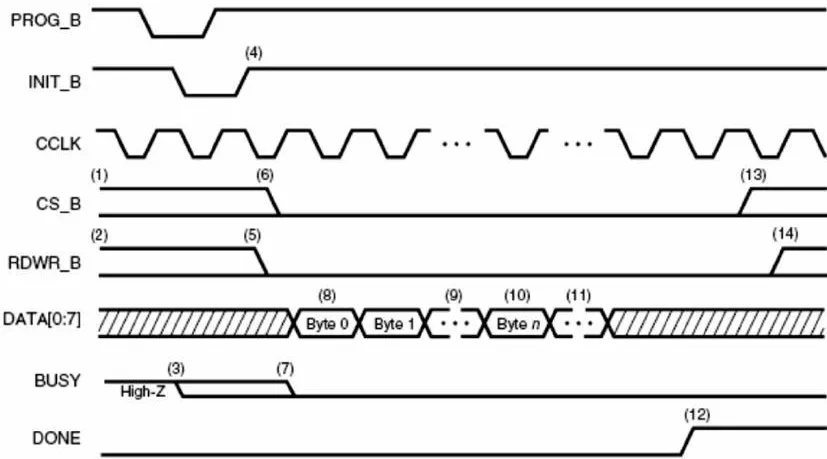

FPGA1和FPGA2動態加載時序如圖4所示。

圖4 FPGA1和FPGA2動態加載時序圖Fig.4 Dynamic loading timing diagram of FPGA1 and FPGA2

DSP異步訪問接口和 FPGA3相連,FPGA1和FPGA2加載端口連在FPGA3上,由FPGA3將DSP命令時序轉換成圖4所示時序。操作步驟如下:

(1)DSP送入FPGA3動態加載命令,FPGA3將PROG-B置一段低脈沖;

(2)DSP從FPGA3讀INIT-B狀態,由低到高依次讀FLASH數據,將數據寫入FPGA3;

(3)FPGA3收到寫數據命令,產生寫時鐘,將數據寫入FPGA1或FPGA2;

(4)數據寫入成功后,DONE信號電平跳變,表示加載成功,并上報狀態。

3.3 CPCI總線設計

常用CPCI接口采用PCI橋芯片設計,一端提供PCI總線,一端為本地端口。本接收機系統中,直接使用DSP的PCI外設接口,用C語言代替硬件描述語言做控制邏輯,增加了通用性和靈活性。該PCI接口符合PCI2.3規范,工作頻率為33 MHz/66 MHz,本接收機選擇工作頻率為33 MHz,采用32位數據線,其傳輸峰值速度可達132 Mbyte/s。

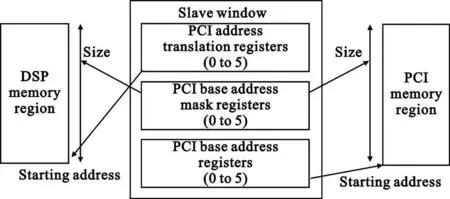

DSP的PCI接口程序主要包括配置寄存器、存儲器映射寄存器。對C6455芯片而言,供應商ID、設備ID分別是0x104C、0xB000,對多個板卡共用一個機箱情況下,只需更改ID號就可識別不同設備。DSP地址空間和PCI空間的映射關系如圖5所示。

圖5 DSP地址空間到PCI地址空間的映射圖Fig.5 The address of DSP and PCI mapping diagram

C6455提供了6個基地址寄存器BAR0~BAR5,通過設置基地址寄存器,可實現DSP和主機端的地址映射。DSP作為高速數傳接收機的控制功能單元,接收主機下發的各種參數和命令,產生相應的控制流程,同時讀取FPGA中各種狀態信息,并上報參數。

4 性能測試

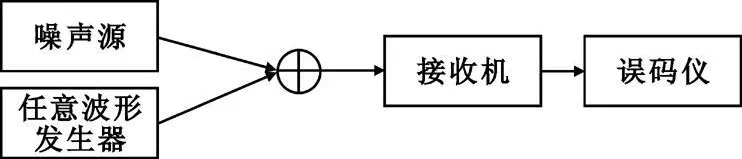

接收機解調誤碼性能(BER)是衡量接收機性能的重要指標。通過任意波形發生器產生不同的調制數據輸入到噪聲源,與噪聲源產生不同噪聲功率譜密度的高斯白噪聲相加后,送入接收機解調,解調后數據送誤碼儀測試解調誤碼率,就可完成高速數傳接收機的解調誤碼性能指標測試。測試連接如圖6所示。

圖6 高速數傳接收機誤碼性能測試框圖Fig.6 High-rate data transmission receiver BER performance test diagram

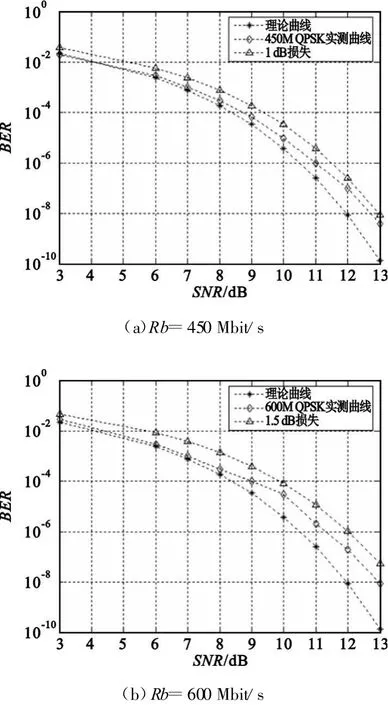

針對QPSK調制信號,數據傳輸速率分別為450Mbit/s和600 Mbit/s情況下,接收機誤碼率測試結果如圖 7所示。測試結果表明,當碼速率為450Mbit/s情況下,接收機的解調損失在1 dB以內,碼速率為600 Mbit/s情況下,接收機的解調損失在1.5 dB以內。本文所設計的接收機實現方案從解調損失上要優于文獻[2]中設計的接收機,在傳輸數據速率600 Mbit/s的情況下,本文的方法取得了大約1.5 dB的性能增益,這在實際的應用中是非常有意義的。

圖7 接收機誤碼率測試曲線Fig.7 The BER curves of high-rate data transmission receiver

5 結束語

本文設計的CPCI總線高速數傳接收機,采用硬件模塊化、功能化以及軟件動態加載與升級技術,解決了不同高速數傳系統應用中使用同一硬件平臺的難題,目前已成功應用在450 Mbit/s和600 Mbit/s兩種不同的高速數傳系統工程項目中。另外,通過設計了模數混合和全數字接收機兩種硬件接口以及ADC采樣率實時設置功能,該高速數傳接收機具有更強的通用性和靈活性,可應用在其他中低速數傳系統中。

[1] 曹志剛,錢亞生.現代通信原理[M].北京:清華大學出版社,2006.CAO Zhi-gang,QIAN Ya-sheng.Modem Communication Principle[M].Beijing:Tsinghua University Press,2006.(in Chinese)

[2] 董長海,鄭雪峰,鄭戈,等.600Mb/s高速數傳接收的設計與實現[J].遙控遙測,2007(增刊):31-34.TONG Chang-hai,ZHENG Xue-feng,ZHENG Ge,et al.Design and Realization of 600Mb/s High Data-rate Receiver[J].Journal of Telemetry,Tracking and Command,2007(Suppl.):31-34.(in Chinese)