基于FPGA乘法器的FIR濾波器系統設計

張婧霞,沈三民,翟成瑞

(中北大學儀器科學與動態測試教育部重點實驗室,山西 太原 030051)

在通信系統、航空航天系統、雷達系統、遙感遙測系統等工程技術領域,無論是在信號的獲取、傳輸,還是信號的處理和轉換都離不開濾波技術。由于FIR濾波器具有嚴格的線性相位和在系統中具有穩定性,因此FIR濾波技術具有廣泛的應用[1-4]。

隨著微電子技術的發展,采用現場可編程門陣列FPGA進行數字信號處理得到了飛速發展。由于FPGA具有現場可編程的特點,具有高速傳輸和處理數字信號的能力,實現濾波算法速度高于傳統的DSP的數字處理信號的能力,因此受到硬件電路設計工程師們的青睞[5]。傳統的采用FPGA實現的FIR濾波器由于采用寄存器直接相乘模式占用了大量的乘法資源,因此在進行乘法運算時影響FPGA運行速度,并且由于資源上的限制導致FPGA其他功能受到限制。但基于FPGA乘法器的FIR濾波器具有節省FPGA 資源、提高運算速度、減少電路體積等優點[6-7]。

1 FIR低通濾波器整體設計

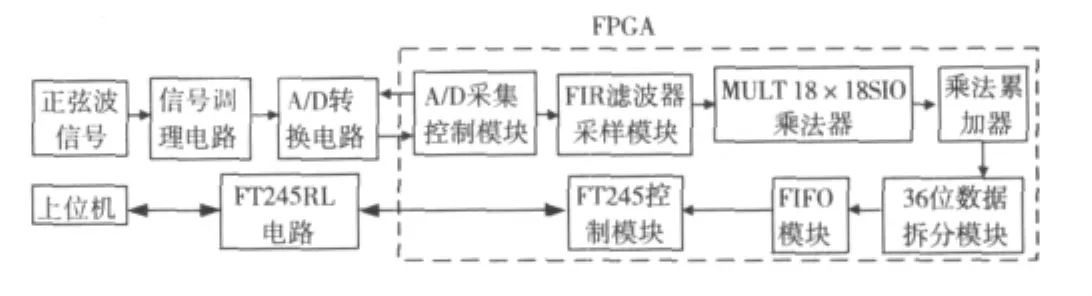

本文主要介紹的是FIR低通濾波器,該FIR低通濾波器主要由硬件電路和FPGA程序組成。FIR濾波器硬件電路主要由信號調理電路、AD轉換電路、FPGA控制電路、FT245RL電路和上位機組成,其中FPGA內部程序模塊包括AD采集控制模塊、FIR濾波器采樣模塊、MULT 18×18SIO乘法器模塊、累加模塊、36位數據拆分模塊、FIFO模塊和FT245控制模塊。該濾波器主要功能是利用信號發生器產生特定頻率的正弦波,通過信號調理電路進行調理后經過12位的AD轉換器進行轉換輸出數字信號,FIR濾波器采樣模塊工作在60 MHz的時鐘內,并且以10 kHz的采樣率對AD輸出的數字信號進行采樣,采樣到的數字信號值連同FIR濾波系數輸出到18位乘法器模塊,經過乘法運算后進行累加,累加出來的是36位數據,最終通過FT245組成的USB接口傳給上位機進行曲線顯示,所得結果即為濾波后的數據,系統組成原理如圖1所示。

圖1 FIR低通濾波器整體設計框圖

2 硬件電路設計

2.1 AD轉換器電路

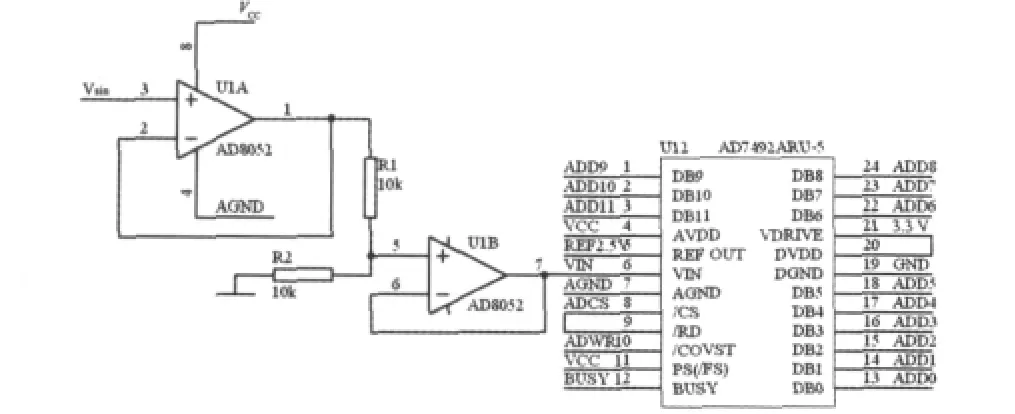

本系統中對于輸入電壓的采樣率為10 kHz,因此采用了AD公司的高性能逐次逼近型A/D轉換芯片AD7492BRU-5,最大轉換速率為1.25×10次/s,具有12位的并行數據輸出接口,并且具有三態功能,能夠滿足系統采樣要求。

由于AD7492BRU-5的基準電壓為2.5 V,而輸入的模擬信號范圍為0~5 V,因此在模擬信號進入AD轉換器之前還需要對信號進行適當的調理,調理電路如圖2所示。采用兩個10 kΩ電阻對輸出的模擬信號進行分壓,使其范圍滿足A/D轉換器的輸入要求,并通過電壓跟隨器進行輸出,信號不會失真。

圖2 AD轉換器連接電路

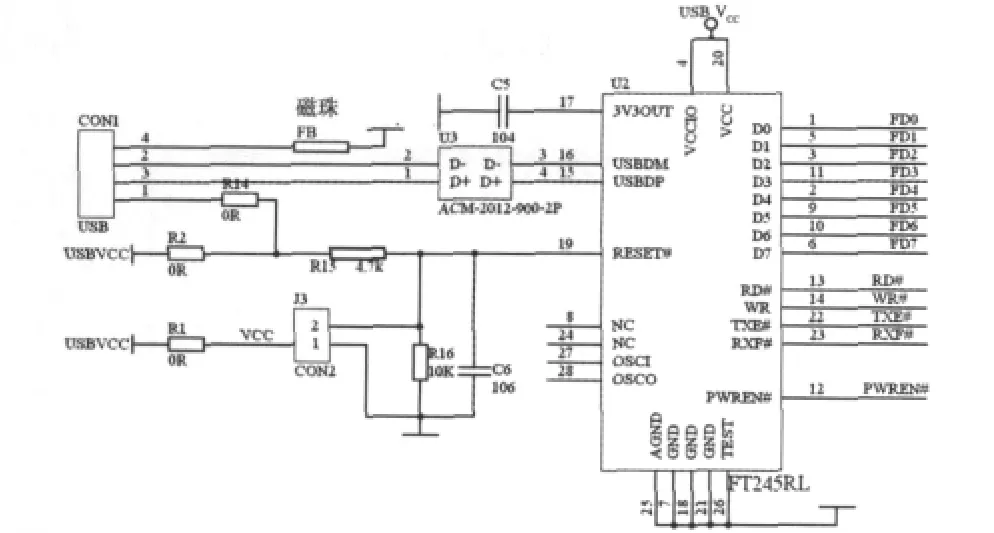

2.2 FT245接口電路

本系統中FPGA發送的濾波數據通過USB接口回傳給上位機,上位機讀取USB的數據,并對數據進行存盤。USB接口電路采用FTDI公司的FT245RL作為USB接口芯片實現上位機與FPGA的數據通信。FT245RL無需編寫固件程序,可以使用FTDI公司提供的驅動程序,并且兼容USB1.1及USB2.0協議。USB連接電路如圖3所示,該電路中數據傳輸線接一個共模電感ACM-2012-900,當傳輸差分信號USBDM和USBDP上有共模干擾時,由于共模信號產生磁場疊加,在共模電感上形成高阻抗,從而達到濾除共模干擾的目的。USB口接地端接一個磁珠,這樣連接可以更好地防止電源不穩對數據傳輸的干擾。USB接口從FPGA讀取數據,FPGA內部只要判斷到FIFO中產生半滿信號,就將數據傳輸到USB接口,最終利用上位機進行讀取。

圖3 FT245連接電路

3 FIR濾波器程序設計

本設計采用Xilinx公司XC3S400的FPGA進行程序驗證,XC3S400是高密度的可編程邏輯器件。它的主要特點包括具有最小5 ns的引腳到引腳的邏輯時延,全局時鐘最高引腳最高輸入頻率為66 MHz,內核用1.2 V供電,I/O口可設置在3.3 V工作。該器件具有豐富邏輯的資源,包括16個MULT18×18SIO,可以進行大量的乘法運算[8]。

FIR濾波器程序主要由采樣模塊、乘法器模塊、累加和模塊組成,采樣模塊功能是采集60個采樣值、并把濾波系數輸出到乘法器與采樣值進行相乘。乘法器模塊主要功能是對60個采樣值和60個濾波系數進行相乘,所得的相乘結果輸入累加器。累加器就是將輸入的60個結果進行累加,得到36 位的濾波結果[9-10]。

3.1 采樣模塊

采樣模塊主要是對AD轉換后輸出的值進行采樣,本設計中采樣率為10 kHz,也就是AD的采樣率為10 kHz,而濾波器對AD轉換后輸出的值的采樣率也是10 kHz,它們的實現在程序上是同步的。在AD輸出模塊當中,每當數據轉換完成輸出時,會產生一個rdy上升沿信號,采樣模塊接收并辨別rdy上升沿信號后接收第一個數據,并把第一個濾波系數輸出到MULT18×18SIO乘法器,同時給乘法器CLK端產生一個上升沿信號,啟動乘法器進行相乘,相乘結果時間極短,所以可以實現高速相乘運算。

采樣模塊利用VHDL語言進行編寫,利用狀態機實現,在模塊中采用4個狀態來實現采樣和濾波,第1個狀態為采樣,只要判斷rdy上升沿信號就利用寄存器進行采樣,并給寄存器賦值;第2個狀態取出對應的濾波系數;第3個狀態為產生乘法器時鐘clk,且計數器counter加1;第4個狀態判斷計數器是否加到60,如果是則跳出采集,輸出濾波結果,其采集和控制流程圖如圖4所示。

圖4 采樣模塊工作流程圖

采樣模塊當中還包括60個濾波系數,濾波器系數由Matlab產生,Matlab中FDATool(Filter Design& Analysis Tool)是Matlab信號處理工具箱專用的濾波器設計分析工具,操作簡單、靈活,可以采用多種方法設計FIR濾波器。本文設計的FIR濾波器為60階,采樣率為10 kHz,截止頻率為200 Hz的FIR低通濾波器,通帶內紋波抖動為1 dB,阻帶下降60 dB,并將其系數量化成16 bit后保存到COE文件中。本設計當中濾波系數擴大32767 倍,具體的量化過程如下:

設濾波系數浮點數h(n)為xn,最大系數為xmax,量化結果為zn,則

量化后的數據為10進制數,需轉化為二進制數,并將十進制的負數轉化為二進制補碼形式才可以用于乘法器進行相乘。在采樣模塊當中,定義了一個可以存60個系數數組的寄存器,FIR濾波器系數就存在于60個數組當中,在運算中可以靈活取出濾波系數進行相乘。

3.2 乘法器

Xilinx FPGA開發環境軟件自帶的18位乘法器模塊MULT18×18SIO如圖5所示,該乘法累加器A(17:0)為AD轉換后的數據輸入端口,B(17:0)為濾波系數輸入端口,C端口為乘法器時鐘clk輸入端,上升沿有效,CE為使能端高電平有效,R端為復位端低電平有效,P(35:0)為濾波器數據輸出端。因為MULT18×18SIO乘法器為FPGA內部自帶的硬核資源,可以直接調用,因此幾乎不占用任何FPGA資源,并且可以提高乘法速度,只要在clk端給予一個上升沿就可以對其操作,使用起來方便、快捷。

圖5 MULT18×18SIO乘法器

3.3 累加和模塊

累加和模塊主要對乘法結果進行累加,在累加模塊中定義一個36位的寄存器,在累加上升沿脈沖到來時對乘法器輸出的結果進行累加,一共進行59次累加,累加后的結果送入36位數據拆分模塊,拆分成5 byte的數據壓入FIFO進行發送,上位機通過FT245讀取到濾波數據。

4 試驗驗證

針對FIR濾波器電路系統,設計了一個專門與配套USB接口FT245通信的軟件,該軟件能讀取USB數據,并把USB數據保存在以DAT為后綴名的文件中。用該軟件對該數據進行還原轉化,即可得到其電壓值,并能通過軟件把結果顯示出來。

用信號發生器同時給濾波器系統發送頻率為100 Hz(小于200 Hz)和250 Hz,幅值為0~+5 V正弦波輸入信號,正弦波信號經過信號調理及AD轉換后由FPGA進行FIR低通濾波,最終通過USB接口將數據傳輸到計算機的上位機當中。讀取到的濾波數據如圖6所示,圖中陰影部分為一個濾波數據值007F00A59F,轉化為電壓值過程如下:007F00A59F轉化為十進制數,得到 N=2130 748831 ,由量化過程得到傳遞值f=524062 (32767 除以最大系數得到),則AD輸出值x=N/f=4065 ,那么電壓值V=(4065 /4095 ×2.5)V=2.48 V,則輸入電壓值Vin=(2.48×2)V=4.96 V。

圖6 DAT文件的FIR濾波原始數據(截圖)

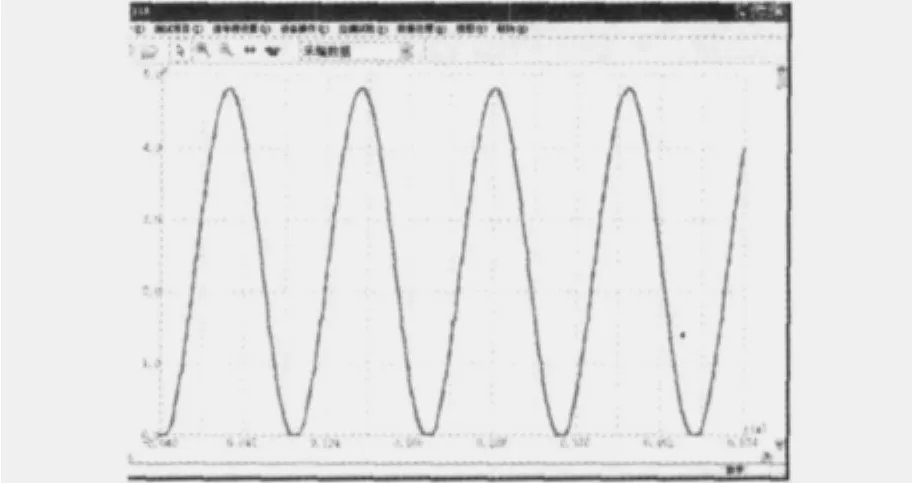

根據以上轉換關系,利用上位機軟件對讀取到的數據進行曲線繪制,所得到的曲線為0~+5 V正弦波,如圖7所示。由試驗數據可知,頻率大于200 Hz的信號幅值經過濾波器后受到衰減,不能通過FIR低通濾波器,低于200 Hz的信號卻能順利通過濾波器,可見所設計的濾波器滿足要求。

圖7 上位機軟件顯示的濾波后的波形(截圖)

5 小結

試驗結果表明,基于FPGA乘法器的FIR濾波器在采樣控制、數字信號處理等方向,相比傳統FPGA的FIR濾波器設計具有簡單、快捷且有更高的執行效率和速度的特點。在該設計當中,FPGA的資源占用率只有10%,留有足夠的資源以設計其他邏輯電路功能。基于FPGA乘法器的FIR濾波器高速、高靈活性的優點,使其可廣泛應用于高速數字信號處理領域。

[1]李受明.FIR數字濾波器在雷達信號處理中的應用[D].西安:西安電子科技大學,2007.

[2]朱義勝,董輝.信號處理濾波器設計[M].北京:電子工業出版社,2004.

[3]王金明,張雄偉.FIR濾波器的優化設計與硬件實現[J].電視技術,2003,27(3):19-21.

[4]陸宇鵬,邱宏安,田多華,等.基于FPGA的數字濾波器的設計與實現[J]. 電聲技術,2008,32(5):23-25.

[5]虞露,李儆,馮興光.大規模可編程邏輯器件(FPGA)開發系統電源設計研究[M].西安:西安電子科技大學出版社,2007.

[6]從玉良,王宏志,趙曉明.數字信號處理原理[M].2版.北京:電子工業出版社,2009.

[7]蔣壘,王昌林,許沖.基于FPGA的FIR數字濾波器算法實現[J].船舶電子工程,2006,26(1):151-156.

[8]李云松,宋銳,雷杰,等.Xilinx FPGA設計基礎[M].西安:西安電子科技大學出版社,2008.

[9]徐以濤,王呈貴,王金龍.基于DA算法的FIR濾波器硬件實現[J].解放軍理工大學學報:自然科學版,2003,4(3):22-25.

[10]胡廣書.數字信號處理:理論、算法與實現[M].2版.北京:清華大學出版社,2003.