基于單片機的數字信號傳輸性能分析儀的設計*

李天山

(廈門海洋職業技術學院,福建 廈門 361012)

伴隨著計算機的飛速發展和網絡時代的到來,數字通信應用的領域越來越多,在通信的過程中各種干擾因素也隨之而來,這些干擾的存在嚴重影響了數字信號的傳輸性能,因此設計一種能夠及時快捷的檢測數字傳輸通道的傳輸性能的分析儀有很長深遠的應用意義。

1 系統整體設計

1.1 數字信號發生模塊

m序列數字信號可通過移位寄存器的邏輯組合實現,其產生序列的速度非常快,我們可以采用TI公司的MSP430F169單片機為DDS定義時鐘周期信號,達到輸出信號數據率的步進可調。MSP430F169單片機在具有8MHz高速晶振的同時,還具有方便的切換超低功耗模式,從而大大降低系統的功耗,性價比高等特點。DDS在數字頻率合成方面的優勢具體體現在相對帶寬寬、頻率轉換時間短、頻率分辨率高、輸出相位連續、可產生寬帶正交信號及其他多種調制信號、可編程和全數字化、控制靈活方便等方面,并具有極高的性價比。

1.2 偽隨機信號發生模塊

利用有源晶振為移位寄存器提供時鐘信號,電路易于實現,同時具有很強的抗干擾能力,有源晶振不需要單獨搭建振蕩電路,信號質量好,比較穩定,而且連接方式相對簡單。本研究使用10M有源晶振。

1.3 數字信號分析電路

用FPGA對曼徹斯特碼進行數據分析,并提取出信號的時鐘周期,運用FPGA的優勢是它的處理速度非常快,可以通過內部鎖相環把外部時鐘倍頻,核心頻率可以到幾百兆。便于提取時鐘信號。

2 理論分析與計算

2.1 m序列數字信號的參數與理論計算

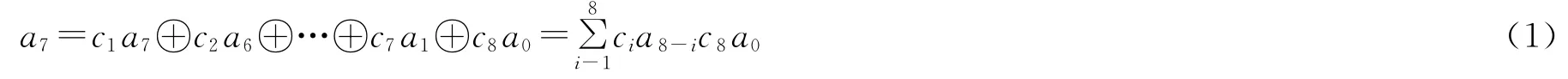

信號產生電路主要由MSP430單片機、DDS電路、線性反饋移位寄存器等部分組成。在數字信號發生器中運用的是八級線性反饋移位寄存器,電路圖如圖1所示。

八位移位寄存器的初始狀態為a-1a-2…a-8,經過一次一位之后,狀態變為a0a-1a-2…a-6,經過n次移位之后,狀態變為a7a6…a1a0。再次移位一次,移位寄存器左端新得到的輸入a8,可以寫為

ci的取值決定了移位寄存器的反饋連接和序列的結構,故ci是一個很重要的參量。用特征方程表示為:

圖1 八級移位寄存器電路圖

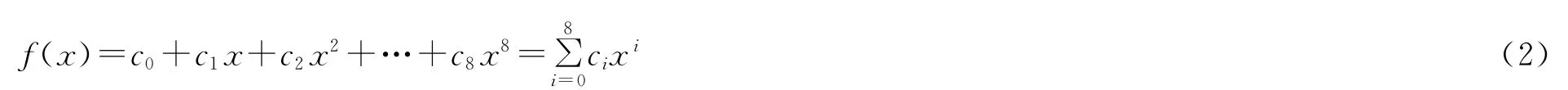

2.2 低通濾波器的參數計算

此模塊采用三個截止頻率分別為100K、200K、500K的二階無限增益多路低通有源濾波器。對于截止頻率為100K的濾波器,電路圖如圖2所示

2.3 同步信號的提取原理

本系統可以選擇使用曼徹斯特碼模式工作。曼徹斯特碼在時鐘前半周期和原碼相同,后半周期和原碼相反。因此要用數據選擇器,在時鐘信號為高電平時,選擇原碼作為曼徹斯特編碼的信號,而時鐘信號為低電平時,選擇原碼的反碼作為曼徹斯特編碼信號。

在數字信號分析電路中,需要對曼徹斯特碼進行同步時鐘信號的提取,具體的提取電路可以分為整形電路、微分電路、全波整流電路、窄帶濾波電路和鎖相環電路。利用這些電路來提取出同步信號,并經過FPGA對時鐘信號和數字信號進行分析最終在示波器上顯示出眼圖。

圖2 低通濾波器仿真電路

2.4 眼圖的顯示分析

數字信號在示波器上累積而顯示出眼圖,從眼圖的形狀可以看出碼間串擾和噪聲的影響,分析出傳輸信號的整體特征。一個完整的眼圖應包含從“000”到“111”的所有狀態,八種狀態在短時間間隔內相疊加,即可形成眼圖。可以根據計算得出眼圖的消光比、Q因子等參數、眼交叉比和信號上升時間和下降時間。根據這些參數來判斷信號的受干擾程度。

Q因子用于測量眼圖信噪比的參數,它的定義是接收機在最佳判決門限下信號功率和噪聲功率的比值,可適用于各種信號格式和速率的數字信號,其計算公式如下:

其中,“1”電平的平均值Ptop與“0”電平的平均值pbase的差為眼幅度,“1”信號噪聲有效值σ1與“0”信號噪聲有效值σ0之和為信號噪聲有效值。

Q因子綜合反映眼圖的質量問題。Q因子越高,眼圖的質量就越好,信噪比就越高。Q因子一般受噪聲、光功率、電信號是否從始端到終端阻抗匹配等因素影響。一般來說,眼圖中1電平的這條線越細、越平滑,Q因子越高。在不加光衰減的情況下,發送側光眼圖的Q因子不應該小于12,接收測的Q因子不應該小于6。

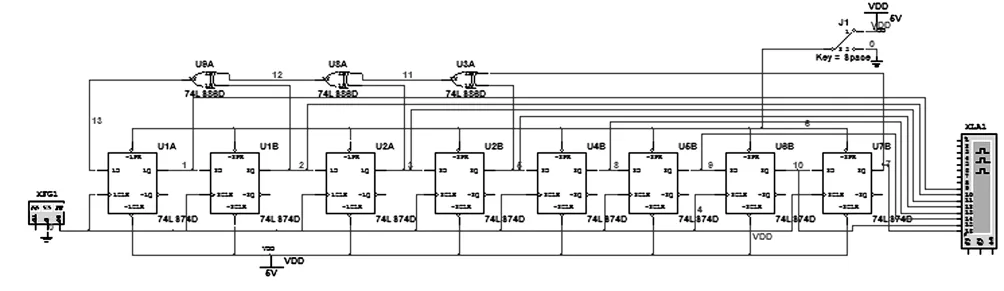

3 系統電路與程序設計

3.1 系統整體框圖設計

圖3 系統總體框圖

如圖3所示,本設計由MSP430單片機控制DDS電路為八位線性移位寄存器提供時鐘周期,使移位寄存器產生f(x)=1+x2+x3+x4+x8的m序列數字信號。用10M有源晶振為十二位線性移位寄存器提供時鐘周期,產生f(x)=1+x+x4+x5+x12的m序列偽隨機信號。數字信號在經過三個低通濾波器后與偽隨機信號在同向求和運算電路中合成為信號V2a。該信號經過電壓比較器電路的整形后傳輸給FPGA進行同步時鐘信號的提取,并利用時鐘信號觸發傳輸信號,在示波器上顯示出眼圖。從而判斷系統數字信號的傳輸性能。

3.2 數字信號發生器的設計和原理圖

本模塊使用MSP430單片機作為信號發生的主控芯片,它定義DDS發出方波信號作為m序列數字信號發生器的時鐘信號,使八位移位寄存器發出不同頻率的數字信號,并實現了數據率在10—100kbps之間的步進可調。在此基礎上,運用液晶12864正確顯示出信號發生器的的步進率。

相位累加器由N位加法器與N位累加寄存器級聯構成。每來一個時鐘脈沖fs,加法器將控制字k與累加寄存器輸出的累加相位數據相加,把相加后的結果送到累加寄存器的數據輸入端,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字相加。這樣,相位累加器在時鐘作用下,不斷對頻率控制字進行線性相位累加。由此可以看出,相位累加器在每一個中輸入時,把頻率控制字累加一次,相位累加器輸出的數據就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號周期頻率。

為了避免在開始工作時移位寄存器進入全0狀態,將組成的8級移位寄存器電路的D觸發器中1~7級的復位端和第8級D觸發器的置數端連接一個單脈沖發生器。當接通電源開始工作時,單脈沖發生器會產生一個開機復位脈沖,就使移位寄存器開始工作時不會進入全0狀態。理論上在接通電源以后,這個由8級D觸發器所組成的移位寄存器電路就會產生P=63的m序列。

4 系統測試和數據分析

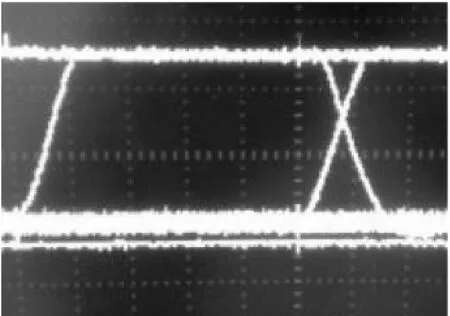

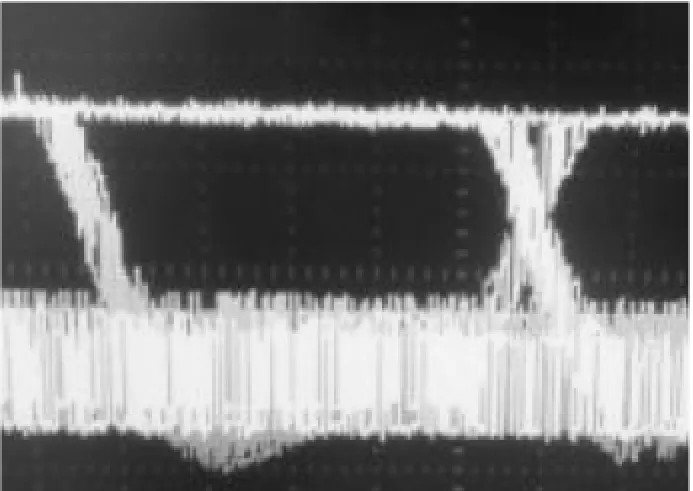

通過示波器觀察在有干擾信號和無干擾信號兩種狀態下的眼圖波形如圖4和圖5所示。

圖4 實測無噪聲眼圖

圖5 實測加入噪聲眼圖

通過示波器可以觀察到當加入的偽隨機信號的幅值不同時得到的眼圖的幅度、消光比、眼交叉比會發生相應的變化,從而可以分析出該數字信號傳輸的性能。

經測試,本次設計已完成m序列隨機數字信號發生器、偽隨機碼發生器、并通過曼徹斯特編碼進行傳輸、三個低通濾波模擬實際數字信號傳輸、曼徹斯特編碼同步信號提取模塊等各項功能,并均達到實際應用的各項指標。

5 結束語

在數字時代的浪潮中,數字信號傳輸性能分析儀的應用前景越來越廣闊,基于該技術的應用產品會有很大的發展空間,本系統采用MSP43F149作為主控處理器,完成了由信號發生器、偽隨機信號生成器、濾波電路、控制顯示部分組成,能夠很好的實現對數字信號傳輸性能的測試功能,通過對該系統的整體性能測試,本設計能過滿足實際應用的技術指標要求。

[1]童詩白,華成英.模擬電子技術基礎[M].4版.北京:高等教育出版社,2001.

[2]曹磊.MSP430單片機C程序設計與實踐[M].北京:北京航空航天大學出版社,2007.

[4]王前虹,債殿堂,成謝鋒.電工電子一體化實驗教程[M].北京:中國石油大學出版社,2008.

[5]王兆安,黃俊.電力電子技術[M].北京:機械工業出版社,2000.

[6]王毓銀.數字電路邏輯設計[M].北京:高等教育出版社,2005.

[7]李朝青.單片機原理及接口技術[M].北京:北京航空航天大學出版社,2005.