新型低功耗CMOS片上溫度傳感器設計*

林 榮,蔡 敏,黃偉朝,李正平

(1.華南理工大學電子與信息學院,廣州 510640;2.廣州潤芯信息技術有限公司,廣州 510663)

隨著集成電路技術的發展,集成度迅速提高,芯片的熱效應得到越來越多的關注和研究。各種系統芯片需要體積小、功耗低、性能可靠的片上溫度傳感器實時檢測芯片表面溫度變化。目前報道的使用CMOS 工藝的測溫方案有很多種[1-3],參考文獻[4]利用CMOS工藝的兩個襯底三極管(PNP)的基—射電壓差 ΔVBE的溫度特性,一個帶隙基準電壓和∑-ΔADC得到數字輸出,該文獻報道在-55℃ ~125℃溫度測量精度可達±0.1℃(3σ),但是該設計使用動態元件匹配、斬波放大器和∑-ΔDAC減小誤差,而且利用二階∑-ΔADC作為模數轉換器,電路結構復雜,占用芯片面積大,對于片上溫度傳感器來說,這不是一種經濟的方案。參考文獻[5-6]中采用了反相器鏈的延遲時間隨溫度變化的特性來測量溫度,最后通過一個TDC得到被測溫度的數字值,電路過于復雜,功耗也較高,不符合低功耗要求。參考文獻[7-9]中利用MOS晶體管的閾值電壓的溫度特性得到負溫度特性電壓,然后驅動一個VCO,得出頻率與溫度成比例的振蕩信號。但是晶體管的閾值電壓的工藝偏差非常大,校準成本較高。

綜合考慮閾值電壓、遷移率和襯底三極管的感溫原理,本文采取襯底PNP管的作為感溫元件,這是工業界最成熟的、性能最可靠的感溫器件。模數轉換器由結構簡單、性能穩定環形振蕩器和數字測頻電路組成。整個系統電路具有面積小、功耗低、結構簡單的優點,滿足測量精度(±3.5℃)和低功耗要求。

1 溫度傳感器的系統描述

本溫度傳感器由三個模塊組成:PTAT電流偏置電路;環形振蕩器;數字測頻和校準模塊。如圖1所示,PTAT電路產生與溫度成正比的電流IPTAT,該電流鏡像到環型振蕩器的調諧電路中,控制振蕩器的振蕩頻率,構成電流饑餓型VCO,由此得到振蕩頻率與溫度成正比的信號。數字測頻和校準模塊測量振蕩信號的頻率輸出8位數字,在此添加了校準電路,減小工藝角對測量精度的影響。數字信號通過SPI輸出到基帶電路。

圖1 溫度傳感器系統示意圖

2 溫度傳感器子模塊的設計

2.1 PTAT電流偏置電路的設計

為了得到與溫度成正比的偏置電流,采取了工業界常用的兩個襯底三極管Q1、Q2的基-射電壓之差:

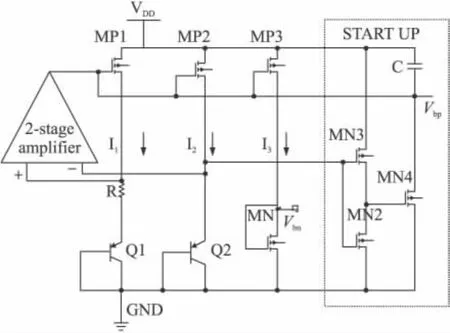

其中N是Q1、Q2晶體管發射極面積之比,K為波爾茲曼系數,T為絕對溫度。由式(1)可知,ΔVBE與絕對溫度T成正比[5]。具體的電路結構圖2所示,Q1的發射極面積是Q2發射極面積的8倍,兩個管子的發射極電流I1=I2,MP1、MP2、MP3三個管子組成比例為1∶1∶1的電流鏡,所以I3=I1。其中I3鏡像到環型振蕩器的控制電流,控制環型振蕩器的振蕩頻率。

圖2 PTAT電流偏置電路圖

電路中的兩級差分運放利用其反饋機制,保持運放輸入端電壓相同,為了減小運放的輸入失調電壓和減小電源電壓對輸出電流的影響,運放的直流增益要足夠大,同時保證環路穩定[10]。版圖上運放要考慮匹配,理想情況下運放輸入兩端電壓相等。流過電阻R的電流大小為:

由式(2)可知,忽略電阻R的溫度效應,輸出電流I3與溫度成正比,影響電流I3的非理想因素主要有運放的失調電壓VOS、電阻的工藝偏差ΔR、電流鏡的失配ΔI。可以通過精心設計運算放大器以及在版圖布局考慮匹配可以減小失調電壓;也可以增加管子溝道長度和增大面積來減小電流鏡的失配;最主要的誤差來源與電阻的工藝偏差,在測頻電路中增加了校準電路,可以減小電阻偏差帶來的非理想效應。

該電路必須增加一個啟動電路才能正常工作,如圖2所示,啟動電路由反相器和一個下拉管子組成,如果反相器設計恰當,假如初始狀態電路不啟動,I2=0,則VBE2=0,反相器的輸出就為高電平,管子MN4導通,電流鏡MP1、MP2、MP3柵極電壓被拉為低,電流開始啟動,當電路正常工作,反相器的輸出電平低于MN4的閾值電壓,則MN4關斷,流過啟動電路的電流為0,不影響偏置電路的工作狀態。

電路中的濾波電容C是為了避免后續電路引入干擾,抑制運放輸出節點電壓的波動,保證偏置電路的正常工作,該電容可能影響運放的穩定性,在設計運放時考慮該電容的負載效應。

2.2 環型振蕩器的設計

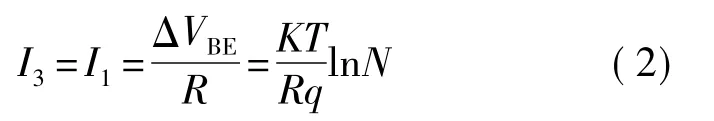

環型振蕩器把前面得到的與溫度成正比的電流轉化為振蕩頻率與溫度成正比的信號。環型振蕩器有多種結構,都是由多個相同的延遲單元組成一個環路,延遲單元可分為單端反相器、差分反相器。環型振蕩器的工作原理是使得環路傳輸函數僅在一個頻率點上滿足Barkhausen判據:

Barkhausen判據僅是實現振蕩器的必要條件,而不是充分條件,要形成環型振蕩器,環路必須提供180°的直流相移和180°的交流相移,180°的交流相移所對應的頻率即是振蕩頻率。因此如果延遲單元采取單端反相放大器結構,那么環型振蕩器應由奇數個延遲單元組成,且級數至少為3;如果延遲單元采取差分放大器結構,并且所有的延遲單元接成反相,則延遲單元應為不小于3的奇數;如果差分延遲中有一個單元接成同相形式,而其他單元接成反相形式,則延遲單元的數目為不小于4的偶數。

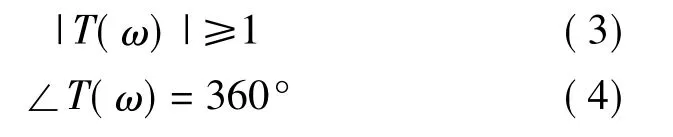

單端延遲單元的延遲時間容易受到電源電壓噪聲和襯底耦合噪聲的干擾,而差分延遲單元則可以在一定程度上抑制這類共模噪聲。考慮到本設計是片上溫度傳感器,在同一襯底上還有很多其他高頻和數字模塊,很容易引起共模噪聲,所以采用差分延遲單元來抑制這類噪聲。差分形式的環型振蕩器的相位噪聲和功耗隨著級數的增加而增加,則環型振蕩器采用圖3的結構,由三級反相器延遲單元組成,其中Vbp、Vbn是從PTAT電流偏置電路鏡像過來的柵極控制電壓。

圖3 電流控制環型振蕩器結構圖

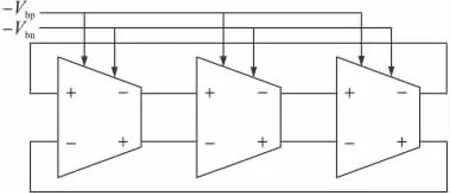

環型振蕩器中的延遲單元采取圖4所示的新電路結構[11],這是一種互補輸入、互補輸出、差分調諧的結構,由四個反相器組成,MP2、MN2和MP5、MN5組成的兩個反相器為常見的延遲單元結構,在信號路徑上引入一定的延遲。MP3、MN3和MP4、MN4組成的兩個反相器構成一個鎖存器,在狀態發生轉換時,在輸出節點和之間形成正反饋,加快轉換速率,提高振蕩器的相位噪聲性能.這兩個反相器的驅動強度設計為略高于主通道的反相器,因此轉換的速率取決于這兩個反相器,而與振蕩頻率關系不大。圖4中差分控制電壓Vbp、Vbn控制流過MP1、MN1的電流,進而對對主通道上的反相器進行控制,位于鎖存器環路之外,僅調諧延遲單元的延遲時間進而改變振蕩器的振蕩頻率。不改變狀態轉換速率。

圖4 環型振蕩器中的延遲單元電路圖

根據參考文獻[12],每級延遲單元的延遲時間為:

則環型振蕩器的振蕩頻率可由下面式子表示:

上面兩個式子中tdelay為每級延遲單元的延遲時間,M為振蕩器延遲單元的數目,Ibias=I3為從PTAT電流偏置電路鏡像到MP1、MN1的電流,Cload為每級反相器的等效負載等容,VH-VL為輸出電壓擺幅。

把式(2)代入式(6),得到振蕩信號頻率和溫度的近似關系:

這部分電路的非理想效應主要是振蕩器的相位噪聲和電源電壓對振蕩信號擺幅的影響。需要減小相位噪聲,可以通過提高振蕩信號幅度和加快信號在上升沿與下降沿的轉換速率,圖4的電路中的鎖存器起到了這樣的作用,在兩個輸出之間形成正反饋,加快轉換速率,能夠提供從電源到地的全擺幅信號,還可以提供全差分信號輸出。另外,利用片上的LDO電源,得到穩定的電源電壓,減小電源電壓對信號擺幅的影響。提高信號頻率的穩定性。

2.3 數字測頻與校準電路設計

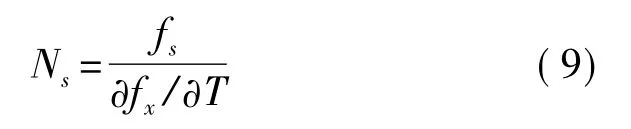

測量頻率方法采用同步測頻法,如圖5所示,利用兩個計數器,在被測信號上升沿到來的時候分別對40 MHz的基準時鐘(片上系統提供)和被測信號的周期在規定的閘門時間進行計數,由下面公式:

其中fx為被測信號的頻率值,fs是基準時鐘的頻率值。Nx是被測信號在閘門時間Ns/fs里的周期數目,Ns是在該閘門時間基準時鐘的周期數目,Ns的值由信號振蕩頻率與溫度的關系決定,Ns的計算公式:

其中,各參數與上文定義相同。確定了Ns、fs和-60℃時的Nx的值后,Nx-N-60的值就代表了溫度值。

圖5 數字測頻電路示意圖

為了消除工藝誤差,提高測量精度,在環型振蕩器的每一級延遲單元增加了校準電路,如圖4所示。利用四位數字控制字A4A3A2A1控制延遲單元的等效負載電容的大小,其中的校準電容具有二進制權值C4=2C3=4C2=8C1,校準電容值由上述四位控制字調整大小,變化范圍為0至15C1,步進為C1。由式(7)可知,PTAT電路中的電阻大小受工藝的影響,導致測量誤差。這樣調整環型振蕩器延遲單元的等效負載電容,可以消除這種工藝誤差。

3 仿真結果與分析

本電路利用 TSMC 0.13 μm CMOS工藝,在 Cadence仿真環境的virtuoso進行原理圖和版圖設計,版圖布局如圖6所示,面積僅為0.02 mm2,利用Spectre進行仿真,后版圖仿真結果如圖7、8、9所示。

圖6 溫度傳感器版圖

圖7是PTAT電流偏置電路的輸出電流隨溫度的變化關系,非線性為僅為1.6%。得到的輸出電流與溫度關系式:

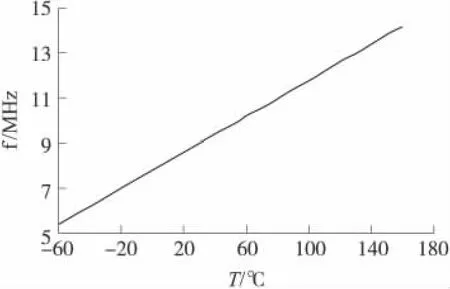

圖8是環型振蕩器輸出信號振蕩頻率隨溫度的變化關系,振蕩頻率與溫度的關系為:

其中T是絕對溫度,偏置電流與溫度成正比例關系,振蕩頻率與溫度也保持良好的線性關系。

圖7 偏置電路輸出電流隨溫度的變化關系圖

圖8 振蕩器輸出信號頻率隨溫度變化關系圖

圖9 數字輸出值隨溫度變化關系圖

圖9為最后輸出的八位無符號數代表的十進制值隨溫度變化的關系,線性度也很好。數值與溫度的關系為:

其中D是輸出數值,T為攝氏溫度,上述結果是在典型工藝角下的仿真圖。其他工藝角通過校準可得到表1的結果。其中的誤差來源于環型振蕩器的相位噪聲、校準電容的步進誤差和傳感器的自熱效應,有待改進。

表1 溫度傳感器的性能參數

4 結論

本文利用襯底三極管的基-射電壓差的溫度特性設計了基于環形振蕩器的數字溫度傳感器,并提出了可行的校準方案。利用TSMC 0.13μm CMOS 1.2V工藝設計,后仿真結果表明,本文提出的設計方案在在-60℃到160℃溫度范圍內測量精度在±3.5℃以內,具有精度高、功耗低、工作電壓低、芯片面積小、測溫范圍廣的特點。本電路很容易集成到SOC芯片上,為集成電路的溫度測量和控制提供方便。

[1]林賽華,楊華中.新型全CMOS片上溫度傳感器設計[J].半導體學報,2006,3:551-555.

[2]張詢,王鵬,靳東明.一種新型的CMOS溫度傳感器[J].半導體學報,2005,11:2202-2207.

[3]張艷紅,劉兵武,劉理天,等.一種新型硅基厚膜壓力/溫度傳感器的設計和制作[J].傳感技術學報,2006,19(6):2376-2379.

[4]Pertijs M,Makinwa K,Huijsing H.A CMOSSmart Temperature Sensor With a 3σInaccuracy of 0.1 ℃ From 55 ℃ to 125 ℃[J].IEEE,J.Solid-State Circuit,2005,40(12):2805-2815.

[5]Chen P,Chen C C,Tsa C C,et al.A Time-to-Digital-Converter-Based CM-OS Smart Temperature Sensor[J].IEEE Journal of Solid-State Circuits,2005,40(8):1642-1648.

[6]Woo K,Meninger S,Xanthopoulos T,et al.Dual-DLL-Based CMOS All-Digital Temperature Sensor for Microprocessor Thermal Monitorin-g[J].IEEE,ISSCC,Microprocessor Technologies,2009:68-70.

[7]Wang Nailong,Zhang Sheng,Zhou Runde.A Novel Built-in CMOS Temperatrure Sensor for VLST Circuits[J].Chinese Jounnal of Semiconductors,2004,25(3):252-255.

[8]曹新亮,余寧梅,衛秦嘯.集成CMOS溫度傳感器設計、實現和測試[J].傳感技術學報,2010,23(1):38-42.

[9]李蕾,謝生,黃曉綜.應用于無源標簽的CMOS溫度傳感器[J].傳感技術學報,2010,23(8):1098-1101.

[10]Razavi B.Design of Analog CMOS Integrted Circuits[M].Los Angeles,University of California,2002.309-324.

[11]池保勇,余志平,石秉學.CMOS射頻集成電路分析與設計[M].北京:清華大學出版社2006.367-453.

[12]Sundaresan K,Allen P andAyazi F.Proces and Temperature Compensation in a 7-MHz CMOS Clock Oscillator[J].IEEE Journal of-Solid State Circuits,2006,41(2):433-442.