基于FPGA的脈沖發(fā)生器波形模塊設(shè)計(jì)

張孝飛, 趙孔新, 張賽男

(長春工業(yè)大學(xué)計(jì)算機(jī)科學(xué)與工程學(xué)院,吉林長春 130012)

0 引 言

高速脈沖發(fā)生器作為現(xiàn)在測(cè)試領(lǐng)域中一種重要的測(cè)試工具,能夠產(chǎn)生脈沖寬度、脈沖幅度、信號(hào)延遲等脈沖參數(shù)充分可控的脈沖信號(hào),以滿足特定的測(cè)試要求。脈沖頻率、信號(hào)延遲調(diào)整的精度及分辨率、參數(shù)可編程能力和信號(hào)功率、脈沖寬度調(diào)整的精度和分辨率等方面的因素決定了高速脈沖發(fā)生技術(shù)的先進(jìn)性。為了使之具有高速靈活、高精度及高分辨率的特點(diǎn),文中用Altera公司可編程FPGA芯片以及安森美公司可編程延時(shí)芯片和高性能D觸發(fā)器來設(shè)計(jì)。

1 總體設(shè)計(jì)思路

脈沖發(fā)生器的波形模塊設(shè)計(jì)是由FPGA內(nèi)部的脈沖/群脈沖產(chǎn)生電路產(chǎn)生脈寬、占空比、脈沖周期、脈沖個(gè)數(shù)可調(diào)的脈沖[1]。考慮到如果只用FPGA內(nèi)的時(shí)序做脈寬調(diào)整,而FPGA內(nèi)部的脈寬調(diào)整是通過計(jì)數(shù)器計(jì)數(shù)來調(diào)整的,調(diào)整的頻率是根據(jù)當(dāng)前的周期調(diào)整的,這樣就不能滿足高精度的要求,所以考慮用內(nèi)部計(jì)數(shù)粗調(diào)加外部芯片細(xì)調(diào)的方法來達(dá)到高精度。

通過FPGA內(nèi)產(chǎn)生上升沿觸發(fā)信號(hào)和經(jīng)過粗調(diào)加微調(diào)產(chǎn)生的下降沿觸發(fā)信號(hào)送入高性能D觸發(fā)器[2]來產(chǎn)生所需要的信號(hào)。此方案可以滿足100 MHz脈沖的產(chǎn)生。

2 脈沖/群脈沖產(chǎn)生電路

2.1 設(shè)計(jì)方法

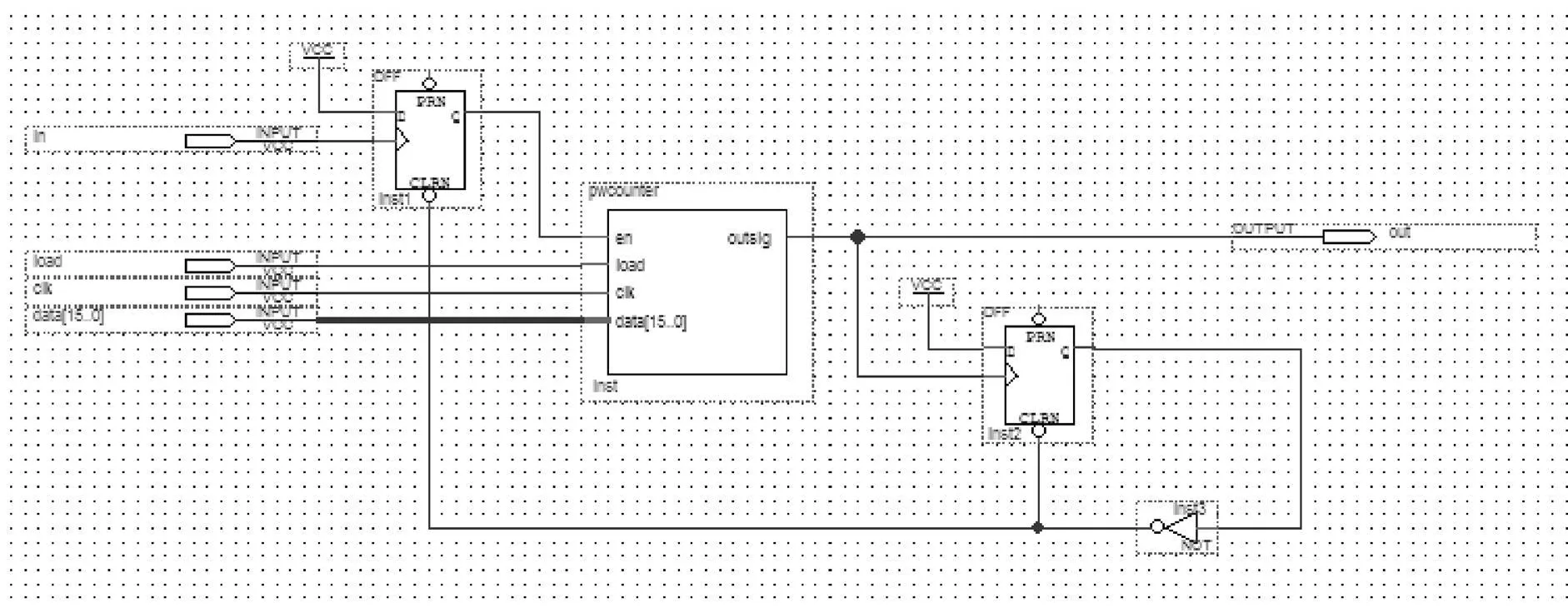

為了產(chǎn)生所需要的脈沖,可以利用Verilog HDL語言在FPGA內(nèi)部編寫單脈沖/群脈沖計(jì)數(shù)器。在其后面加上一個(gè)門控時(shí)鐘電路和窄脈沖產(chǎn)生電路,門控時(shí)鐘電路能夠抑制毛刺的產(chǎn)生,窄脈沖產(chǎn)生電路能夠是上升沿觸發(fā)信號(hào)和下降沿觸發(fā)信號(hào)是窄脈沖,滿足設(shè)計(jì)的最小脈寬要求。原理框圖如圖1所示。

圖1 單/群脈沖產(chǎn)生電路

2.2 工作原理

圖1中,period[15..0]端是輸入的群脈沖周期;num[15..0]是輸入的群脈沖個(gè)數(shù);clk是當(dāng)前的時(shí)鐘輸入端;load是復(fù)位端,高電平有效;gate信號(hào)是經(jīng)過模式選擇的使能信號(hào);out是脈沖/群脈沖輸出端[3-5]。

單脈沖的產(chǎn)生是群脈沖產(chǎn)生的一種特殊情況,將群脈沖周期值period[15..0]和脈沖個(gè)數(shù)num[15:0]值設(shè)置成同樣的值時(shí)就可以實(shí)現(xiàn)。

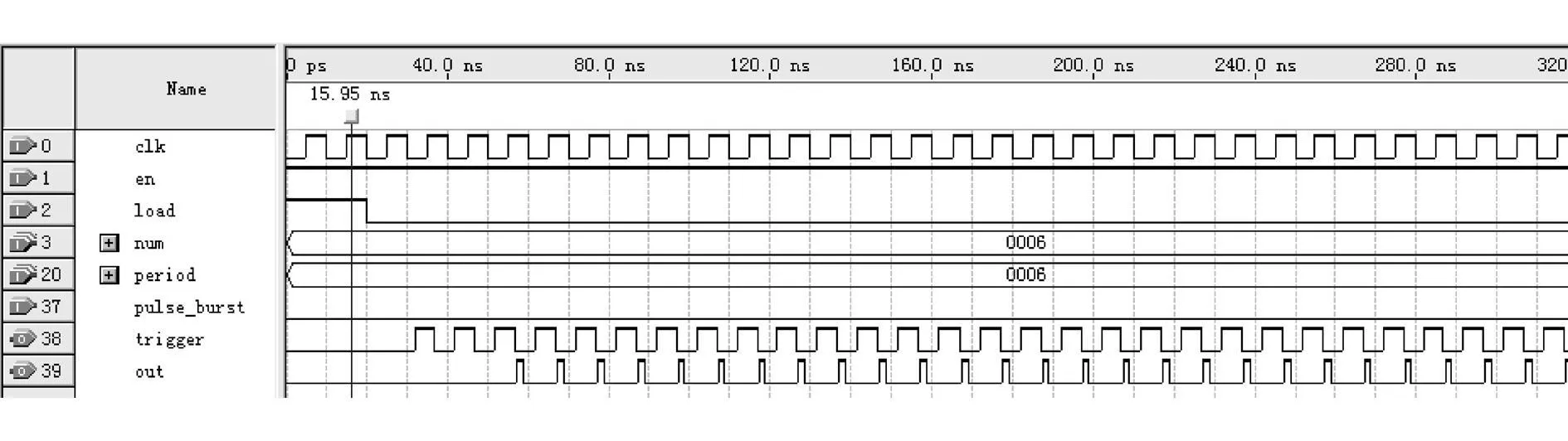

下面以群脈沖為例介紹單脈沖/群脈沖計(jì)數(shù)器模塊的工作原理:設(shè)置num[15..0]和period[15..0]分別為6和10,gate(en)為1,在pulse模塊的out將會(huì)連續(xù)輸出6個(gè)時(shí)鐘周期(clk)的高電平,然后連續(xù)輸出4個(gè)時(shí)鐘周期(clk)的低電平,這樣計(jì)數(shù)器就計(jì)數(shù)完一個(gè)群脈沖輸出周期,輸出的高低電平通過后面的門控和窄脈沖電路產(chǎn)生窄脈沖信號(hào)。仿真結(jié)果[6]如圖2所示。

圖2 群脈沖時(shí)序仿真圖

圖中,pulse_burst和trigger是設(shè)計(jì)中觸發(fā)模塊的數(shù)據(jù)輸入,pulse_bursr控制是單脈沖還是群脈沖輸出,trigger是標(biāo)志脈沖何時(shí)開始的。如果把num和period設(shè)置相同的數(shù)值,則是單脈沖輸出,仿真結(jié)果如圖3所示。

圖3 單脈沖時(shí)序仿真圖

3 脈寬參數(shù)的調(diào)整方法及電路設(shè)計(jì)

3.1 設(shè)計(jì)方法

如果只利用FPGA內(nèi)的時(shí)序邏輯做脈寬調(diào)整,而FPGA內(nèi)部脈寬調(diào)整是通過計(jì)數(shù)器計(jì)數(shù)的方式實(shí)現(xiàn)的,因此,其調(diào)整的分辨率就是當(dāng)前時(shí)鐘的周期,例如時(shí)鐘頻率為100 MHz[7],此時(shí)鐘周期也就是當(dāng)前時(shí)鐘頻率下的分辨率為10 ns,這不能滿足高精度的要求。為了滿足要求,選取安森美公司的可編程延時(shí)芯片MC100EP196,MC100EP196的分辨率是10 ps,單片延時(shí)最大10 ns,這可以滿足大多數(shù)要求。如果僅僅使用可編程延時(shí)芯片的話,設(shè)計(jì)的脈沖是100 MHz,要求脈寬是5 ns~995 μ s[8],這個(gè)范圍要求用大量的可編程延時(shí)芯片,因此,提出用FPGA+可編程延時(shí)芯片來設(shè)計(jì)脈寬的調(diào)整。整體方案如圖4所示。

圖4 脈寬參數(shù)調(diào)整及電路設(shè)計(jì)

3.2 設(shè)計(jì)原理

在設(shè)計(jì)100 MHz脈沖發(fā)生器時(shí),當(dāng)脈沖高于50 MHz時(shí),脈寬的范圍是10~20 ns。而選用的芯片范圍是10 ns,所以,可以不用FPGA內(nèi)部編程粗調(diào),直接用兩個(gè)延時(shí)芯片串聯(lián)來調(diào)節(jié)脈寬的范圍。而當(dāng)?shù)陀?0 MHz時(shí),可以用FPGA+可編程延時(shí)芯片。粗調(diào)部分的編程模塊電路和微調(diào)部分電路分別如圖5和圖6所示。

圖5 粗調(diào)部分電路圖

圖6 微調(diào)部分電路圖

4 數(shù)字脈沖合成電路

4.1 設(shè)計(jì)方法

數(shù)字脈沖合成電路是通過一個(gè)D觸發(fā)器實(shí)現(xiàn)的,是前面脈沖產(chǎn)生電路產(chǎn)生的經(jīng)過脈寬粗調(diào)、微調(diào)產(chǎn)生的上升沿觸發(fā)信號(hào)和下降沿觸發(fā)信號(hào)送入到數(shù)字合成電路合成最終的數(shù)字脈沖信號(hào)。數(shù)字脈沖合成電路如圖7所示。

圖7 數(shù)字脈沖合成電路

4.2 設(shè)計(jì)原理

數(shù)字脈沖合成電路的核心原器件是MC100EP51,具體設(shè)計(jì)是將MC100EP51的數(shù)據(jù)端D接LVPECL邏輯高電平,而MC100EP51的差分時(shí)鐘輸入端接由前端脈沖產(chǎn)生電路產(chǎn)生的上升沿觸發(fā)信號(hào)LE+和LE-,其清零端RESET是接由經(jīng)過脈寬粗調(diào)和脈寬微調(diào)后的下降沿觸發(fā)信號(hào)TE+,這樣D觸發(fā)器就會(huì)在上升沿觸發(fā)信號(hào)到來時(shí)形成數(shù)字脈沖的高電平,而在下降沿觸發(fā)信號(hào)到達(dá)清零端時(shí),觸發(fā)信號(hào)會(huì)重新清零形成數(shù)字脈沖輸出的低電平,即實(shí)現(xiàn)了最終數(shù)字脈沖的產(chǎn)成。

5 結(jié) 語

目前,脈沖發(fā)生器在測(cè)試領(lǐng)域占據(jù)著主要地位,然而,我國的這項(xiàng)技術(shù)比起國外來落后太多,多年來占據(jù)這個(gè)領(lǐng)域的產(chǎn)品都是國外的產(chǎn)品。所以對(duì)此技術(shù)的研究具有重大的意義。

[1] 何緒芃,曾發(fā)祚.脈沖與數(shù)字電路[M].成都:電子科技大學(xué)出版社,1995.

[2] 劉勇.數(shù)字電路[M].2版.北京:電子工業(yè)出版社,2008.

[3] 巴斯克.Verilog HDL入門[M].3版.夏宇聞,譯.北京:北京航空航天大學(xué)出版社,2008.

[4] 楊恒.零起點(diǎn)學(xué)習(xí)單片機(jī)與CPLD/FPGA[M].北京:北京航空航天大學(xué)出版社,2007.

[5] 陳滿.基于FPGA的高速可變周期脈沖發(fā)生器的設(shè)計(jì)與實(shí)現(xiàn)[J].國外電子元器件,2007(3):35-37.

[6] EDA先鋒工作室,吳繼華,王誠,等.Altera FPGA/CPLD設(shè)計(jì)[J].北京:人民郵電出版社,2005.

[7] 奚俊.脈沖發(fā)生器高速時(shí)鐘模塊設(shè)計(jì)[D]:[碩士學(xué)位論文].成都:電子科技大學(xué),2008.

[8] 鄭義.高速脈沖發(fā)生器信號(hào)合成與控制電路設(shè)計(jì)[D]:[碩士學(xué)位論文].成都:電子科技大學(xué),2008.