雙運算核提升小波變換的FPGA硬件實現

周新文,鐘明光

(1.西安電子科技大學電子工程學院,陜西西安 710071;2.西安電子科技大學機電工程學院,陜西西安 710071)

雙正交小波[1]具有對稱性,因此具有線性相位,有較高的正則性和消失距,能夠平滑地近似表示信號,使得小波變換后大系數盡可能地集中在圖像邊緣處及低頻子帶,適合于圖像壓縮。提升小波變換[2-5]是不依賴于傅里葉變換的新一代小波變換,運算量是傳統小波變換的50%。提升小波變換可以實現同址計算,這樣在運算中可以節省內存的消耗,易于硬件實現。同時提升方法的正反變換結構一致,只有正負號的區別。基于這樣的原因,應用提升運算實現傳統的雙正交小波變換,在圖像壓縮系統中具有一定意義[6-8]。

1 將雙正交小波變換分解為提升步驟

雙正交小波具有很多優良的數學性質,適合在圖像壓縮系統中使用。理論證明,可以將傳統的小波濾波器分解成提升步驟。將傳統小波變換轉換成提升運算,常見較簡單的分解方法是基于因式分解的方法,這里應用Euclidean算法實現。

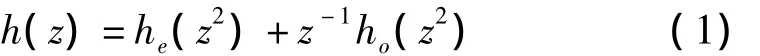

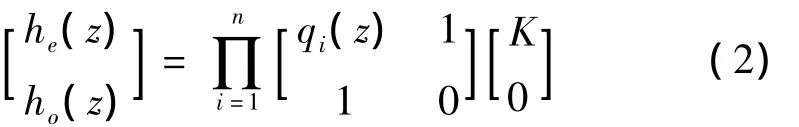

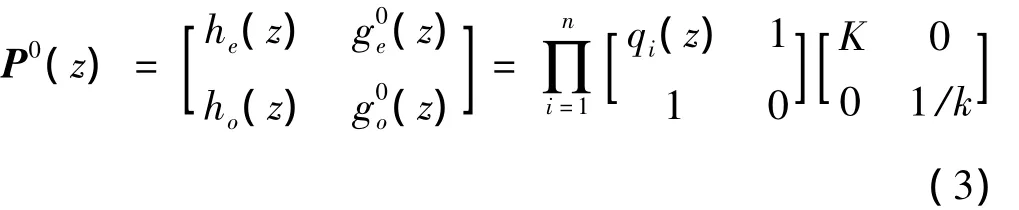

小波濾波器組,應用Euclidean進行分解。將表示為奇數系數與偶數系數的和

由于ho(z)和he(z)互素,式(1)可進一步表示為

對于給定濾波器,通過下式可以得到一個濾波器g0,令

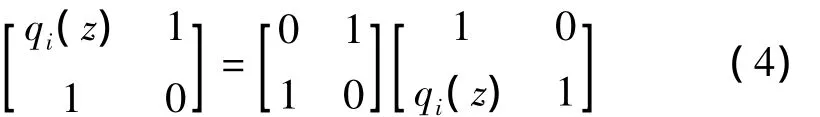

當i為偶數

當i為奇數

由式(4)和式(5)得

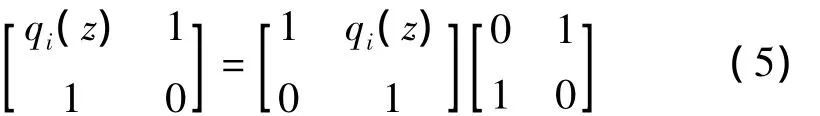

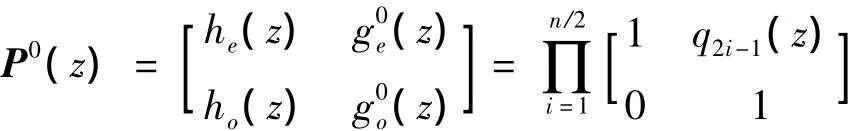

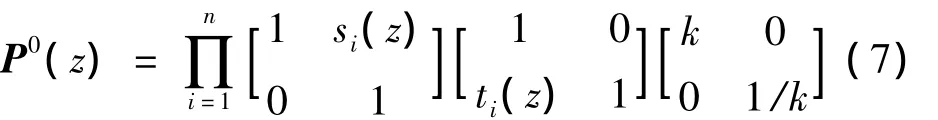

令 si(z)=q2i-1(z),t(z)=q2i(z)得到

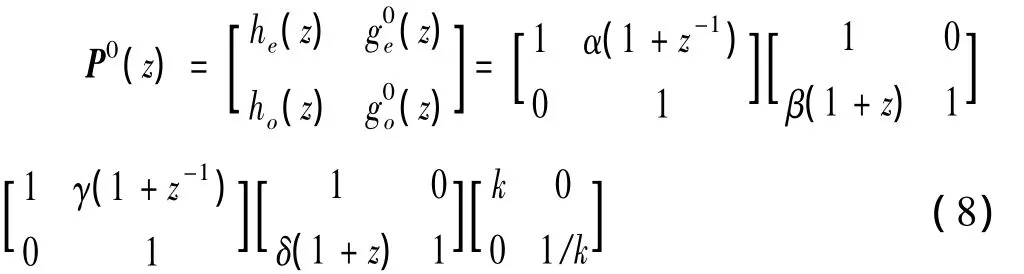

對于9/7小波濾波器分解為

結合小波濾波器的多相分解he(z),ho(z),ge(z)和go(z),聯立方程組解得 α=-1.586 134,β=-0.052 98,γ =0.882 911,δ=0.443 506,k=1.149 604,得到9/7小波變換運算式如式(9)所示。

2 提升小波變換整體設計

采用3級小波變換,共6步一維小波變換操作,即第1層行變換,第2層列變換,第2層行變換,第2層列變換,第3層行變換,第3層列變換。模塊要求1個時鐘周期計算1個小波系數,進行實時處理。在FPGA中采用流水操作。假設1幀圖像的大小為N×N像素,進行小波變換。分析系統可以知道,第1層行列變換需要2×N×N個時鐘周期,第2層行列變換需要1/2×N×N個時鐘周期,第3層行列變換需要1/8×N×N個時鐘周期。

第1層行變換需要直接接收原始數據,因此時鐘頻率應當與數據同步時鐘一致,并且單獨設計。其余5步變換共需1.625×N×N個時鐘周期。要滿足1個時鐘周期產生1個小波系數,則后續5步變換模塊的時鐘頻率至少應當是第1層行變換時鐘頻率的1.625倍,這樣設計就會引入雙時鐘。

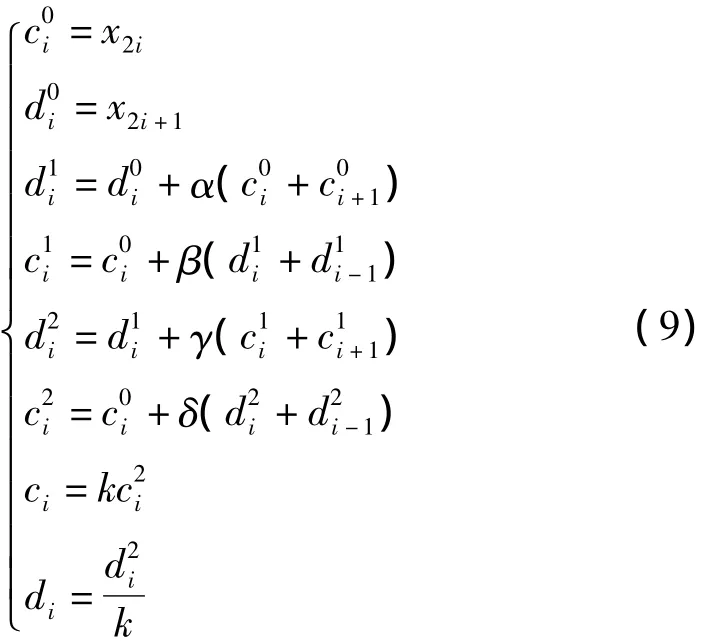

FPGA硬件設計中的多時鐘往往是造成系統工作不穩定的主要因素。設計時需要考慮的因素增多,因此設計難度增加。更高頻率,對于器件的要求會提高,需要更高性能的芯片。同時更高的頻率就意味著更高的功耗。基于以上考慮,本文在后續5步變換的設計中采用了雙變換核的模式。當前幀圖像的第1層行變換與上一幀圖像的后續5步變換并行進行。后序變換過程中,采用雙運算核設計,同時進行兩行(列)數據的運算,這樣就能夠能保證在使用單一時鐘的情況下,每個時鐘周期處理1個數據,達到實時處理的要求,這是本文設計的關鍵。這里引入一個新問題,就是上一步變換的結果需要進行數據組織,為下一步兩行(列)并行運算做好準備。小波變換模塊整體設計如圖1所示。

圖1 小波變換模塊框圖

3 小波變換模塊詳細設計

下面分運算模塊,控制模塊和數據組織模塊對硬件設計做一介紹。運算模塊負責主要的數據運算,控制模塊負責流程控制,數據組織模塊負責對上一步變換的結果進行組織,以滿足下一步兩行(列)變換的需要。

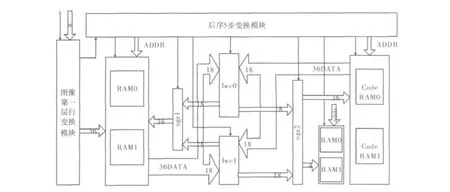

(1)運算核設計。小波變換運算核設計如圖2所示。運算核共涉及8個加法器和5個乘法器。由于前面輸入或者前中間運算結果數據在后序運算中需要用到。因此依據時序為相應的信號設置一定數量的寄存器組。采用流水設計,每步運算到相應寄存器中去取數,這樣保證數據時序對齊。同時運算中還需要處理的問題是邊界擴展。圖 2中的原始數據 x(n),p(m),q(y)和r(z)都需要作邊界擴展,每行(列)各擴展一個數據。其中x(n)和q(y)需要在右邊界作擴展,分別用第一個數據x(N)和q(Mi),p(m)和r(z)需要在左邊界作擴展,分別為最后第一個數據p(0)和r(0),Mi為第i層一維變換需要處理的數據個數的1/2。邊界擴展的時序同步由控制模塊負責。

圖2 小波變換運算硬件設計框圖

(2)控制模塊。控制模塊主要負責各步變換運算的啟動,停止,邊界擴展同步控制,變換模塊數據讀寫的使能,讀寫數據存儲地址的產生等工作。在設計中將第一層行變換進行單獨設計,后序5步變換進行集中設計。這里首先說明第一步行變換的流程控制,后序5步變換相似。

第1層行變換模塊主要作以下工作:1)接收外部數據,將運算結果送數據組織模塊。2)數據運算。3)產生寫數據地址信號以及寫使能信號。4)控制邊界擴展。5)產生外部存儲器RAM片選信號;f產生第一層行變換結束標志。數據按幀處理,幀內部按行處理。隨原始數據有幀同步和行同步信號。控制模塊依據同步信號來控制相應的計數器計數,以控制邊界擴展,產生寫使能,寫數據地址,RAM片選信號,第一層行變換結束標志等信號的產生。

第1層行變換結束,隨即啟動該幀數據的后序5步變換依次進行。后序5步變換進行獨立設計。同時后序5步變換依次控制兩個運算核進行運算,實現兩行(列)的并行處理,這是本設計的關鍵。

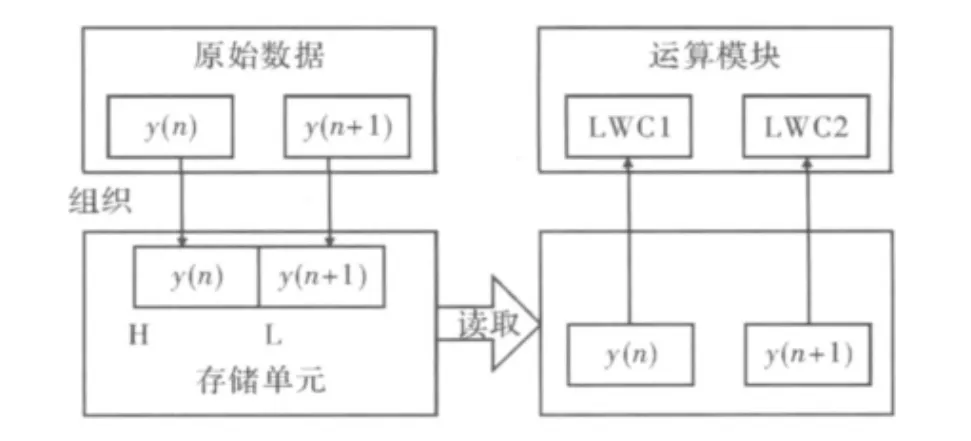

(3)數據組織模塊。數據組織模塊服務于運算模塊。分為兩個子模塊,org1和org2,分別負責行變換數據組織和列變換數據組織。行變換結束之后的數據都要參與列變換運算,在數據組織過程中將同行相鄰兩列兩個數據組織起來,存在一個存儲單元內,這樣在列變換時,讀取一次就能讀出來兩個分別屬于兩列的數據,再分別送給兩個運算核進行處理。數據組織及數據讀取如圖3所示。

圖3 行變換數據組織及列變換數據讀取示意圖

列變換數據組織模塊org2負責列變換結果數據組織。列變換結果只有第1層列變換后的LL1區域和第2層列變換后的LL2區域的數據參與下一層行變換,因此也只有這些數據需要進行組織,其他數據作為最終的變換結果。這些數據的組織是結合后序操作進行的,文中不予說明。列變換結果組織的目標是在行變換過程中讀取一次數據,可以讀取同一列相鄰兩行的兩個數據。數據組織形式與圖3所示類似。

4 試驗仿真

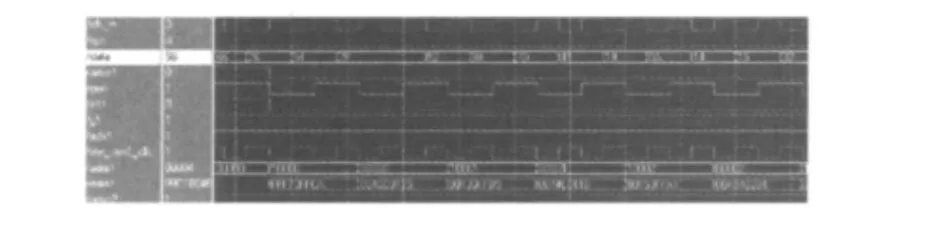

文中的設計在外部時鐘為50 MHz下通過仿真驗證。系統工作穩定可靠。仿真中主要參照C語言版本的數據。格外關注幀數據首尾、行列首尾的同步信號、控制信號、計數器和運算數據等。同時在行列中進行了大量的數據核對工作。在硬件設計中使用了數字時鐘管理模塊(DCM),同時對時鐘和端口做了約束。仿真結果如圖4所示。

圖4 小波變換模塊仿真截圖

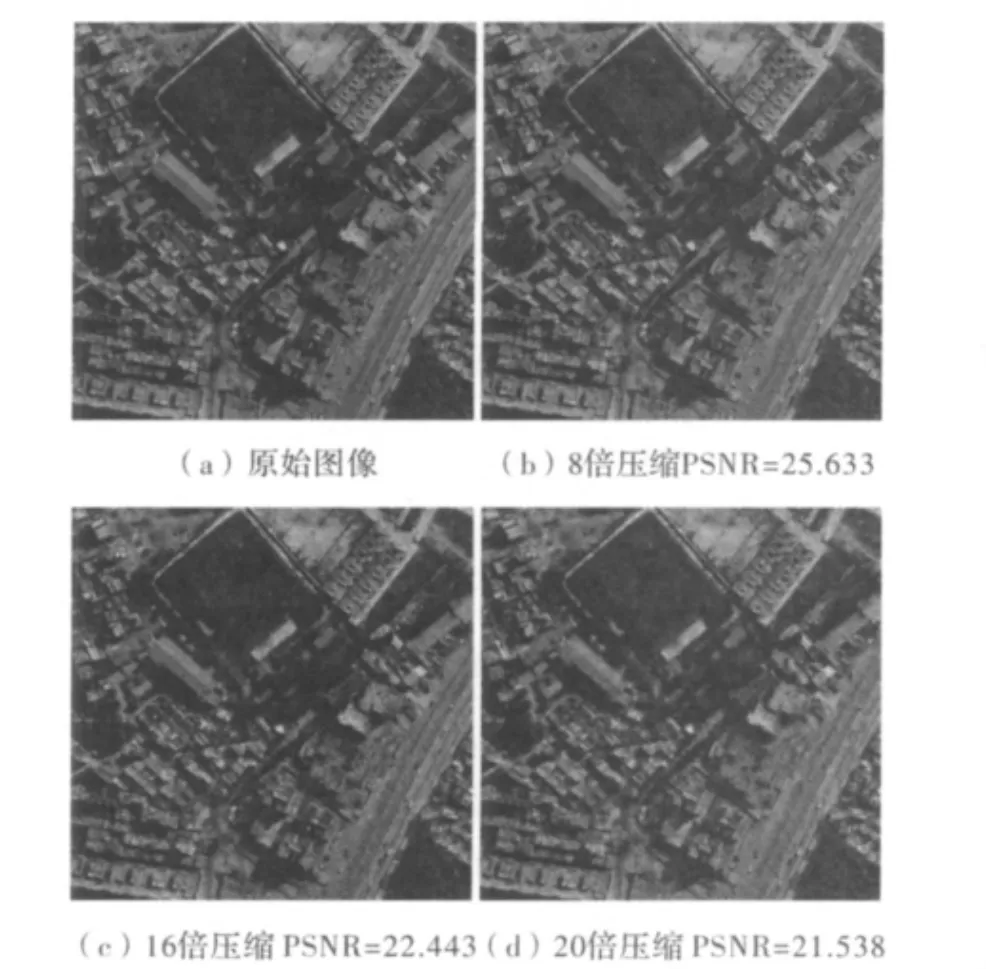

雙正交小波變換采用提升步驟進行計算,大大降低了計算量,同時由于雙運算核設計,系統能夠達到實時處理的要求。雙正交小波變換在圖像壓縮中性能優良。將小波變換作為圖像壓縮系統的一部分,進行了測試。測試過程中,將最終的小波系數按照編碼掃描的要求進行組織。結果顯示,該模塊能夠滿足圖像壓縮系統的要求,數據正確,壓縮性能優良,系統工作穩定。圖5給出了小波變換模塊應用于圖像壓縮編解碼系統的測試結果。圖5(a)為原始圖像,圖5(b),圖5(c)和圖5(d)分別為8倍,16倍和20倍壓縮重構圖像。在20倍壓縮時,重構圖像依然比較清晰。

圖5 小波變換圖像壓縮測試結果

5 結束語

小波變換是圖像壓縮系統中的關鍵模塊。其端口定義明確,易于進行獨立設計。本文應用提升算法在FPGA硬件平臺上實現了小波變換。使用了雙運算核的設計,使得系統在不增加設計復雜性,不提高功耗的情況下,實現了數據的實時處理。系統通過了仿真驗證,工作穩定可靠,達到實用要求。

[1] 崔錦泰.小波分析導論[M].西安:西安交通大學出版社,1995.

[2] DAUBECHIES I,SWELDEN W.Factoring wavelet transforms into lifting steps[J].Journal of Fourier Analysis and Applications,1998,4(3):247 -269.

[3] LIN T,HAO Pengwei,XU Shufang.Factoring m - band wavelet transforms into reversible integer mappings and lifting steps[C].IEEE International Conference on Acoustics,Speech,and Signal Processing,2005(4):629 -632.

[4] CHENG L,LIANG D L,ZHANG Z H.Popular biorthogonal wavelet filters via a liftings cheme and Its application in image compression [J].IEE Proc. - Vis.Image Signal Process.,August,2003,150(4):227 -232.

[5] SWELDEN W.The lifting scheme a custom -design construction of biorthogonal wavelets[J].Applied and Computational Harmonic Analysis,1996,3(2):186 -200.

[6] 王文君,陳思錦,秦其明,等.基于雙正交小波的多分辨率遙感圖像數據融臺[J].現代電子技術,2004(5):33-36.

[7] 都伊林,戴文琪.雙正交小波提升系數的遞推算法與實現[J].現代電子技術,2006(8):77-80.

[8] 胡濤,黃鋁文,張鵬.基于雙正交小波變換在灰度圖像壓縮中的應用[J].現代電子技術,2004(21):84-86.