基于VMM方法的SOC集成驗證

李 磊,羅勝欽

(同濟大學電子科學與技術系,上海 201804)

1 引言

隨著集成電路設計向超大規模發展,芯片驗證工作的難度在不斷增大,驗證的工作量已經占到整個SOC研發的70%左右,芯片驗證直接影響到芯片上市的時間,因此提高芯片驗證的效率已變得至關重要[1]。

VMM是synopsys公司推出的基于system verilog的一套驗證方法學,繼承于RVM。利用VMM的層次化、隨機約束等特點,能有效提升現有的驗證方法,快速搭建具有目標模塊的驗證環境[2]。

2 SOC集成驗證

SOC驗證可以分為集成驗證IV(Integrated Verification)和系統驗證SV(System Verification)。本文主要介紹SOC集成驗證,采用VMM驗證方法學和DesignWare VIP,Master例化為VIP Interface模型,通過約束VIP Transaction參數產生各種定向激勵;通過約束Scenario Class產生各種隨機激勵。

2.1 集成驗證的功能

集成驗證需要完成的任務包括:

(1)驗證各功能模塊是否正常連接;

(2)驗證各模塊對片外IO是否連接正常;

(3)驗證各模塊間的互聯是否正常,例如DMA請求信號和VIC請求信號;

(4)驗證各層總線的地址映射是否正常;

(5)Memory地址遍歷和隨機測試;

(6)多Master沖突檢測等。

集成驗證是基于時鐘周期的測試,能夠基于時序非常方便地發送各種不同的操作,可以彌補系統驗證的不足;同時由于不需要啟動系統,集成驗證具有運行速度快的特點。集成驗證在芯片驗證中極其重要。

2.2 集成驗證平臺

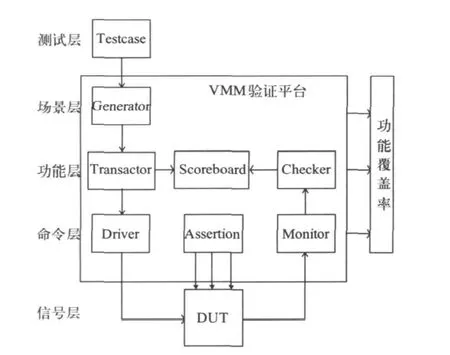

在SOC集成驗證中需要將每個Master替換為VIP Interface模型,通過例化的模型訪問所有的IP寄存器和Memory地址空間,驗證架構互連的正確性。項目的集成驗證平臺采用VMM方法。圖1顯示了VMM層次化驗證平臺的結構[3]。

圖1 VMM層次化驗證平臺結構圖

VMM驗證平臺有多個層組成,主要包括圖1中的測試層、場景層、功能層、命令層和信號層,反映了設計所處理數據的抽象層次。驗證平臺能滿足不同測試用例的各種要求,測試用例的編寫位于該驗證平臺的頂層,每個層次都能給上層提供一系列的服務,并通過抽象將低層次的細節隱藏起來[4]。

3 集成驗證環境

3.1 可歸一化的集成驗證環境

集成驗證是否高效,跟集成驗證環境的優劣密切相關。其中,集成驗證環境的歸一化對集成驗證工作具有重要意義。

集成驗證環境的搭建是需要花費很多人力時間才能完成的。在追求芯片快速上市的今天,一個項目搭建一個全新的驗證環境已經無法讓人接受[5]。集成驗證環境的歸一化主要體現在一些公有目錄和文件的存放具有統一性,可被其他項目重用,從而避免一個項目一個驗證環境的情況,對于新的項目只需修改一小部分文件即可。

本項目采用可歸一化的驗證環境,在驗證環境搭建中減少了很多工作量。

可歸一化SOC驗證環境文件的存放如下:

|—Verification // 驗證的總目錄

|—common // 系統驗證和集成驗證公共目錄

|—bin // 公共腳本

|—testbench //存放公共的測試文件

|—vfilelists //存放所有的RTL代碼

|—pmap //存放IP的pmap文件

|—mem-model //存放存儲器模型

……

|—iv // 集成驗證目錄

|—env //驗證環境文件的存放

|—sim //仿真開始目錄

|—log //仿真log文件夾|—wave //仿真波形文件夾

|—output //編譯仿真過程文件

……

|—tc //驗證用例目錄

|—reg //寄存器測試用例目錄

|—mem //Memory測試用例目錄

……

|—script //腳本文件目錄

|—vmt_bfm //Vmtmaster的bfm目錄

……

其中,env文件下存放著VMM驗證代碼模板。Ahb_env.sv主要用于把各個Master、slave和他們各自的數據通道連接起來,起到貫穿所有組件的作用。Ahb_gen.sv用于產生各種激勵,通過約束Vip transaction參數來定義上層激勵函數。Ahb_defines.sv包含系統使用的宏定義。

對于架構、功能等不同的片上系統,SOC驗證環境的修改不可避免,但是有了可歸一化的SOC驗證環境,其繼承性就大大加強。根據歸一化驗證平臺,就可快速搭建一個新項目的SOC驗證環境。

3.2 基于VMM和DW VIP的集成驗證環境

AMBA總線是ARM公司推出的SOC總線,應用廣泛。本項目也是基于AMBA總線架構,采用ARM9處理器,SOC的集成驗證環境是基于VMM和DesignWare VIP。

V M M提供了用于實現驗證環境的基本類vmm_env,任何驗證環境都從該類繼承,該類控制著整個仿真的進程,用于控制其他類的實例化,進程啟動和結束[6]。

Vmm_env提供的基本函數和方法使得環境的搭建到仿真的完成只需9步操作。這9步操作均在ahb_env.sv中定義和配置,分別是:env.gen_cfg,env.build,env.reset_dut,env.cfg_dut,env.start,env.wait_for_end,env.stop,env.cleanup,env.report。

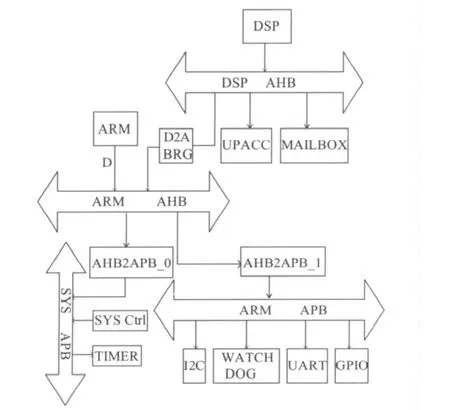

在這9步操作中,我們可以根據具體驗證的要求和任務,在 env.build、env.start、env.wait_for_end、env.stop這幾個步驟中進行設定。圖2是SOC系統芯片結構簡圖。

圖2 SOC系統芯片結構簡圖

在SOC集成驗證中我們將每個Master替換為AHB VIP Interface模型,通過例化的模型訪問所有的IP寄存器和Memory地址空間[7]。

測試層testcase主要是驗證用例的編寫。而VMM_SCENARIO_GEN類由宏生成,根據指定的VMM_DATA類來生成場景發生器。

本文的測試用例構造最常用的方式是:`ARMD.write_32(`asicSYSCTRL,32’h00000010)。此語句是Master ARMD訪問系統控制器SYS CTRL的一個寄存器。其中,`ARMD是一個宏定義,為場景層的generator發生器的一個通道。在write_32函數中,運用了VMM_channel類out_chan.put(item),主要作用是generator將數據包放入通向transactor的channel中。

AHB VIP模型在VMM驗證中起著重要的作用,在VMM中實現的是功能層和命令層的功能。這里采用的是DW_Vip_ahb_master_rvm類,此類具有事務處理器(transacor)的功能。構造函數為:

Function new(

string Instname,

AhbmasterPort portconnect,

dw_vip_ahb_master_configration cfg,

dw_vip_ahb_transaction_channel in_chan,

dw_vip_ahb_transaction_channel out_chan,

)

從in_chan輸入的transaction,經過transactor解析后,轉換成AHB Masterport的信號。通過AHB Masterport interface和DUT交互,從而完成了從測試層到DUT接口的激勵傳輸。

從測試層到達信號層的過程很好地體現了VMM驗證方法的核心。

VMM驗證與傳統的功能驗證區別在于:傳統的功能驗證是在DUT的接口上直接輸入激勵,通過DUT檢查響應。這種方法抽象級別低,在復雜的SOC中不容易定位錯誤,驗證耗時也長;VMM驗證如上述的過程,是抽象級別高的驗證方法,testcase采用面向對象的system verilog語言,有豐富的類庫支持,能有效提高驗證的功能覆蓋率和驗證的效率[8]。

4 結論

在越來越高的抽象層次上進行驗證是驗證方法學不斷發展的趨勢。本文以AMBA總線架構系統芯片的集成驗證為例,采用VMM和DW VIP的集成驗證方法。驗證環境歸一性強,進行簡單修改即可被新項目繼承,同時驗證環境采用大量的腳本文件,自動化程度高,節省了人力資源和時間,可顯著地提高驗證的工作效率,從而縮短整個復雜SOC的研發時間。

[1]Chris Spear. SystemVerilog for Verification[M].Springer,2006,1-18.

[2]Verification Methodology Mannual[P].Synopsys,Inc,&ARM,Inc.

[3]Janick Bergeron,Eduard Cemy,Alan Hunter等著,夏宇聞等譯. System Verilog驗證方法學[M].北京:北京航空航天大學出版社,2007.

[4]Jinbin Hu,Xiaoguang Li.System verification based on VMM and SOPC[C].Computer Science and Information Technology (ICCSIT), 2010 3rd IEEE International Conference.2010:41-43.

[5]孫海平,丁健. 系統芯片驗證方法與技術[M].北京:電子工業出版社,2005.

[6]Keaveney Martin ,McMahon Anthony,O’Keeffe Niall,et al..The development of advanced verification environments using System Verilog[C]. Signals and Systems Conference,208. (ISSC 2008). IET Irish.2008:325-330.

[7]Lu Kong,Wu-Chen Wu,Yong He,et al.. Design of SoC verification platform based on VMM methodology[C]. ASIC,2009. ASICON ’09. IEEE 8th International Conference.2009:1272-1275.

[8]Janick Bergeron.Writing Testbenches using SystemVerilog[M].Springer,2006.