應用于開關電源控制芯片的欠壓鎖存電路的設計

江厚禮,莊華龍,孫偉鋒

1.東南大學集成電路學院, 南京 210096;

2.東南大學國家ASIC工程中心, 南京 210096

隨著各種便攜式電子設備的快速發展,對單片開關電源控制芯片的需求越來越大,相應地,對于芯片的性能要求也越來越高,為了避免在芯片正常工作時電源電壓的波動對芯片內部電路產生不利的影響,通常需要欠壓鎖存電路對電源電壓進行監控,一旦檢測到低于所設置的欠壓閾值, 芯片停止工作[1]。

傳統的欠壓鎖存電路要求簡單實用,但忽略了功耗的問題,當芯片在正常工作時,欠壓鎖存電路仍然具有一定的功耗,這樣就降低整個芯片的轉換效率,基于這樣的考量,本文設計了一種低功耗的欠壓鎖存電路,并在CSMC 0.5 μm CMOS工藝庫下使用Cadence Spectre進行了仿真驗證,結果表明基本滿足設計要求。

1 電路設計

1.1 傳統的欠壓鎖存電路及原理

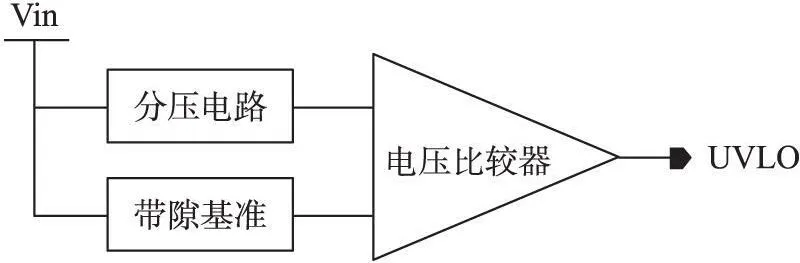

圖1 傳統的欠壓鎖存電路示意圖

傳統的欠壓鎖存電路如圖1所示,供電電源Vin提供偏置使帶隙基準電壓源工作,分壓電路采樣Vin的變化,通過電壓比較器與基準電壓進行比較,產生一個UVLO信號[2]。當采樣值高于基準值時,輸出一個高電平,啟動芯片工作;當供電電源Vin發生波動,致使采樣值低于基準值時,輸出低電平信號,禁止芯片其他部分電路工作,直到解除欠壓狀況。這種電路需要帶隙基準源和比較器,電路結構比較復雜,而且電路的功耗比較大,響應速度較慢[3]。基于這種情況,本文設計了一種新型欠壓鎖存電路,以降低欠壓鎖存電路自身功耗,提高響應速度。

1.2 新型欠壓鎖存電路

新型欠壓鎖存電路由采樣模塊、先導控制模塊、加速響應電路、遲滯反饋電路、緩沖電路等組成,如圖2所示。 R1, R2, R3, R4電阻分壓網絡實現對Vdd電壓的采樣, M1, R5與Inv1(M12, M13組成)構成先導控制電路,控制比較器的灌電流;M2, M3, R6構成比較器, 實現 采 樣 電 壓 與 Vth的 比 較;M5, R8, 與 門AND1構成另外一路充電回路,只在Vdd電壓下降過程中有效;M0實現遲滯反饋的功能;C0為儲能電容,實現充 放電的功能;M6, M7, M8, M9, M10, M11構成施密特觸發器,與Inv3(M14, M15組成)一起實現整形濾波的功能[4]。本電路通過先導控制電路控制電流較大的比較器的灌電流,使比較器只有在狀態發生翻轉時有微弱的電流流過M3,在其余時間內,無論比較器輸出高電平還是低電平,都沒有電流流過M3,也就是說電路無論是處在正常工作狀態還是欠壓狀態,比較器總是關斷,這樣就可以把電路的功耗降到最低,滿足了低功耗設計的要求。

圖2 一種新型欠壓鎖存電路

具體的工作過程敘述如下:

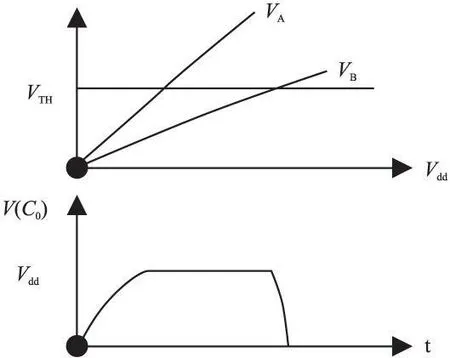

在Vdd電壓上升的過程中,當電壓較低時,由于M1截止, C點處于高電位,可以通過先導控制電路使M2導通,同時M4也導通,給電容C0充電,使E點充電至Vdd,輸出端為高電平,電路處于欠壓鎖存狀態;隨著Vdd電壓升高,由于A點電壓高于B點電壓,使得M1比M3先行導通,先導控制電路使M2截止,此時比較器的灌電流消失,由于電容C0還沒有放電回路, E點仍然保持高電位,電路還是處于欠壓鎖存狀態;當Vdd進一步上升使得B點的電壓高于閾值Vth時, M3導通, C0通過該支路迅速放電, E點電壓降至0,電路解除欠壓狀態,進入正常工作狀態,并且使得M0導通, R1被短路。整個過程如圖3所示。

圖3 工作原理示意圖

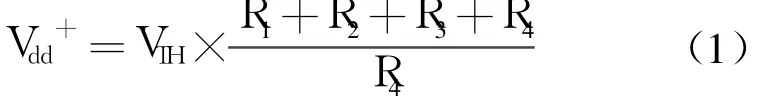

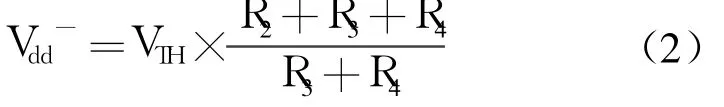

因此在Vdd上升過程中,其閾值為:

隨著Vdd電壓下降,電路從正常工作狀態轉為欠壓狀態的過程中, M3先截止,此時B, E點都為低電平,導致F點為低電平, M6導通,給C0充電,但不會充到Vdd電壓, 隨著Vdd的持 續下降, M1截止,使得M2導通,繼而通過M4, R7給C0繼續充電,此時會充至Vdd電壓,輸出高電平,即電路處于欠壓鎖存狀態,由于M3一直處于截止狀態,沒有灌電流流過,所以基本上沒有功耗[5]。

因此在Vdd下降過程中,其閾值為:

由上述兩式可得出Vdd的遲滯量為:

另外,為了實現先導控制電路的低功耗, R5和M1需要仔細設計, R5不宜太小, M1尺寸適當減小,使流過M1的電流變小[6]。

2 電路仿真與分析

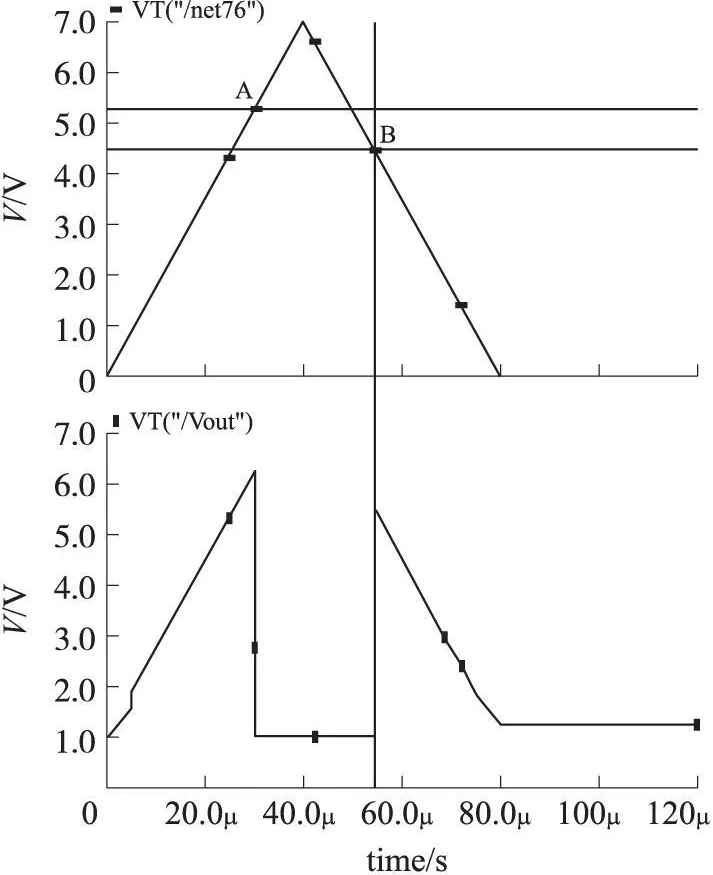

在CSMC 0.5 μm CMOS工藝模型下,利用Cadence Spectre仿真工具對欠壓鎖存電路進行仿真。由于開關電源啟動時為控制芯片提供的電源電壓是逐漸上升的,并且為了觀察電路是否實現滯回功能,所以將Vdd電壓設置成隨時間變化的三角波形,進行瞬態仿真,仿真波形如圖4所示。

仿真結果表明,在Vdd上升的過程中,當Vdd電壓超過5.29 V時,電路退出欠壓狀態;隨著Vdd從7 V開始減小,并低于4.47 V(欠壓閾值典型值),電路又重新進入欠壓狀態,輸出高電平禁止芯片其他部分電路工作;欠壓閾值的滯回電壓范圍為0.80 V,滯回特性使得電路避免干擾信號的影響,提高抗干擾能力[7]。此外,比較器的翻轉速度很快,滿足了對電路的響應速度的要求。

圖4 輸出信號波形

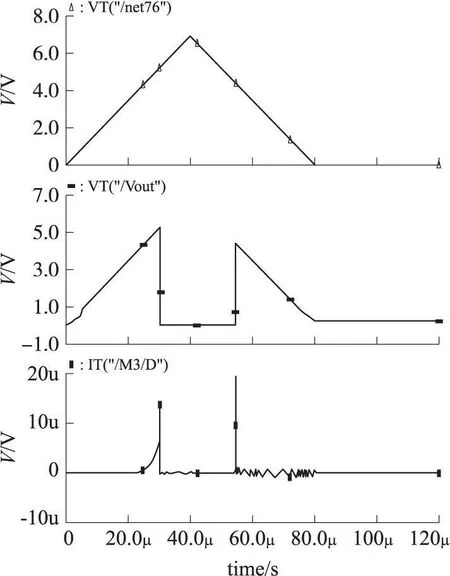

同時,對流過比較器的電流進行瞬態仿真,仿真波形如圖5所示。由圖5可知,只有在比較器狀態發生翻轉的瞬間才有微弱的電流流過M3,在其余時間內,無論比較器輸出高電平還是低電平,都沒有電流流過M3,也就是說電路無論是處在正常工作狀態還是欠壓狀態,比較器都不消耗功率,這樣就可以把電路的功耗降到最低,實現了低功耗的設計。

圖5 流過比較器的電流波形

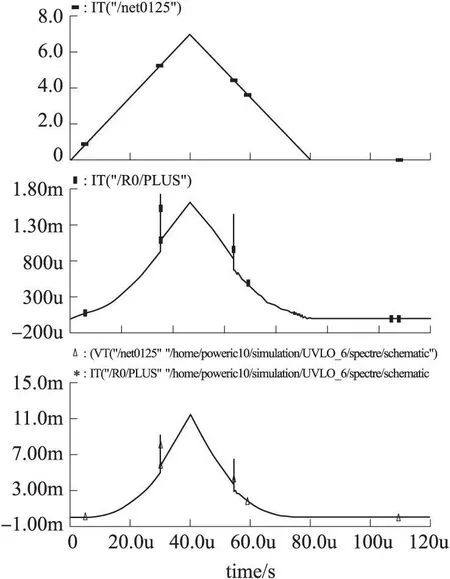

最后,對整個電路的工作電流進行瞬態仿真,仿真波形如圖6所示。仿真結果表明,芯片正常工作時,即從芯片退出欠壓到Vdd下降后重新進入欠壓狀態,欠壓鎖存電路的平均功耗為 7.6 mW, 低于10 mW,實現了低功耗設計的要求。

圖6 整個電路的工作電流波形

3 結論

隨著各種便攜式電子設備的快速發展,對單片開關電源控制芯片的需求越來越大,相應地,對于芯片的性能要求也越來越高,所以欠壓鎖存電路就成了開關電源控制芯片的基本需要, 它可以保證芯片在電源電壓波動的情況下工作的穩定性。本文基于CMOS工藝設計了一種新型欠壓鎖存電路,仿真結果表明,該電路具有功耗低,響應速度快等優點,并且電路結構簡單,可以做成IP核[8],易于移植到其他的開關電源控制芯片中去。

[ 1] 趙春波,許偉,吳玉廣.一種CMOS欠壓保護電路的設計[ J].ICEngineering,集成電路與元器件卷, 2004(10):59-60.

[ 2] 王銳,唐婷婷.一種BiCMOS欠壓保護電路的設計[ J] .電子科技, 2006(10):76-78.

[ 3] 王瑾,田澤,李攀,等.一種改進的BiCMOS工藝欠壓鎖存電路的設計[ J] .現代電子技術, 2007(24):182-184.

[ 4] 鄧云飛,吳玉廣.PWM控制器欠壓鎖定電路的實現[ J].電子技術, 2003(11):51-53.

[ 5] 石躍,周澤坤.一種高性能欠壓封鎖電路[ J] .中國集成電路,2007(4):26-28.

[ 6] Robert John Schuelke, Gregory J Rausch.Current-Mode Undervoltage Lockout Circuit:US Patent, US20090231770[ P] .2009-09-17.

[ 7] Brohlin P L, Allen.Supply Independent Low Quiescent Current Undervoltage Lockout Circuit:USPatent, 6842321B2[ P] .2005-11-01.

[ 8] Allen PE, Holberg D R.CMOS模擬集成電路設計[ M].第2版.馮軍,李智群,譯.北京:電子工業出版社, 2005.