鎖相環中克服非理想因素的鑒相器和電荷泵設計*

程知群,朱雪芳,周云芳,高俊君,徐勝軍

(杭州電子科技大學射頻電路與系統教育部重點實驗室, 杭州310018)

鎖相環在射頻收發電路中的作用是被用來產生一個本振信號,實現收發器的下變頻和上變頻等功能。本振信號的頻譜純凈度將決定接收信號的信噪比,其衡量指標除了相位噪聲外,還有參考雜散特性。參考雜散的影響在鄰近信號干擾嚴重,鑒相器的鑒相死區和電荷泵電路的非理想特性是引起鎖相環參考雜散特性的主要原因[1]。

1 電路設計與分析

傳統的三態鑒相器存在一個非理想效應——鑒相死區,它會顯著地影響鎖相環的鎖定時間和參考雜散等特性。當參考信號和反饋信號存在很小的相位誤差時,在理想情況下鑒相器會根據相位差輸出一個數字脈沖去驅動后面的電荷泵電路。

但是在實際情況中當鑒相器兩個輸入信號的相位誤差太小時, PFD輸出脈沖的寬度太窄以至于不能驅動后面電荷泵電路, 這一段鑒相器不能鑒別的相位誤差區間就稱之為鑒相器的鑒相死區[2]。

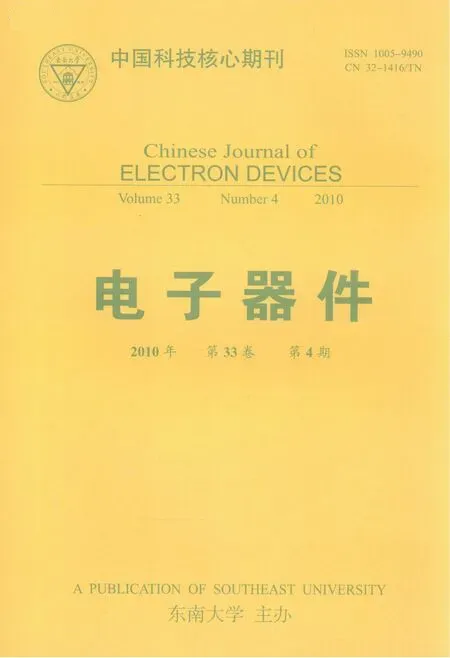

它可以用圖1來解釋,假設PFD內部觸發器輸出信號的上升延時為t。為了開啟電荷泵電路中的開關, PFD的輸出信號必須達到邏輯高電平。假設與門的邏輯翻轉閾值電壓為Vcc/2,也就是說與門會在反饋信號的上升沿到來之后的t/2的時間里重置觸發器。圖1(a)表示PFD的兩個輸入信號存在較大的相位差的情況, UP信號有足夠的時間來到達邏輯高電平。相反的情況如圖1(b)所示, PFD的兩個輸入信號的相位差較小, UP和DN信號幾乎相繼上升,當DN信號到達AND門的翻轉電平時,觸發器被置位。此時UP信號只是超過了Vcc/2, 但是還沒有達到數字邏輯高電平,所以不能開啟后面電荷泵電路的開關。這樣,鑒相器就有了所謂的鑒相死區。

圖1 輸入相位誤差

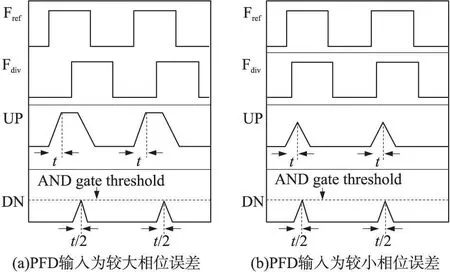

圖2所示為存在鑒相死區的PFD電路的傳輸特性,從圖中可以看出該鑒相器在(-tπ/T~tπ/T)區間內不工作,其中T為參考時鐘的頻率。所以,鎖相環在該工作區間內容易受到外界干擾信號的影響,惡化它的噪聲和雜散特性。

圖2 PFD的傳輸曲線

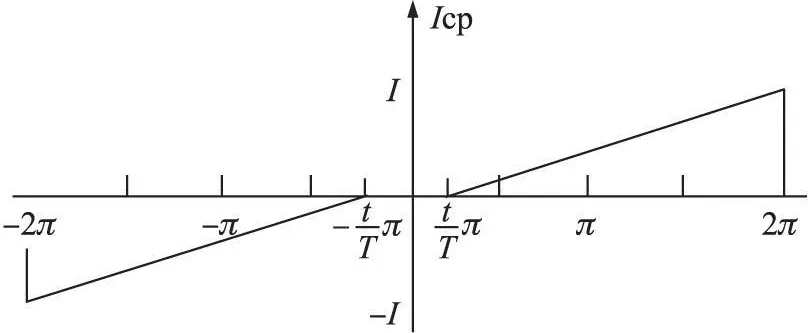

為了克服鑒相器的鑒相死區,通常可以采用提高參考時鐘的頻率和在重置路徑中加入延時單元等方法。但是參考時鐘的頻率通常是由信道間隔決定的,所以現在鎖相環中的PFD電路通常采用增加延遲單元的方法。這里用圖3所示,通過在與門重置路徑上加入延遲單元后使得UP和DN信號有充分的時間能夠達到邏輯高電平來開啟電荷泵電路中的開關,從而消除了PFD的鑒相死區[3-4]。

圖3 克服鑒相死區的方法

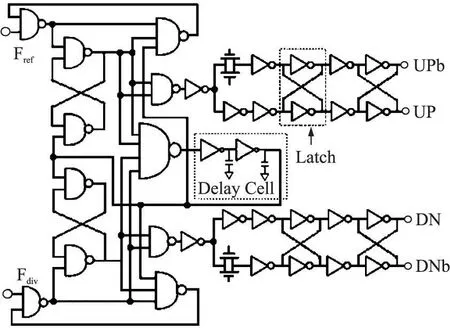

圖4 為本文所設計的PFD電路,它是由標準數字邏輯單元實現,采用的是時鐘下降沿觸發的形式。在四輸入與門后面加上反相延時單元來克服鑒相死區。為了配合后面電荷泵電路的設計,需要四路反相對稱的輸出時鐘信號:UP, UPb, DN, DNb。為此在兩個觸發器輸出端分別加入由反相器和傳輸門組成的輸出電路。其中由反相器構成的Latch的作用是利用正反饋加快信號的邏輯轉換速度,同時也使UP, Upb, DN, DNb的時鐘沿滿足要求[5]。

圖4 本次設計采用的PFD

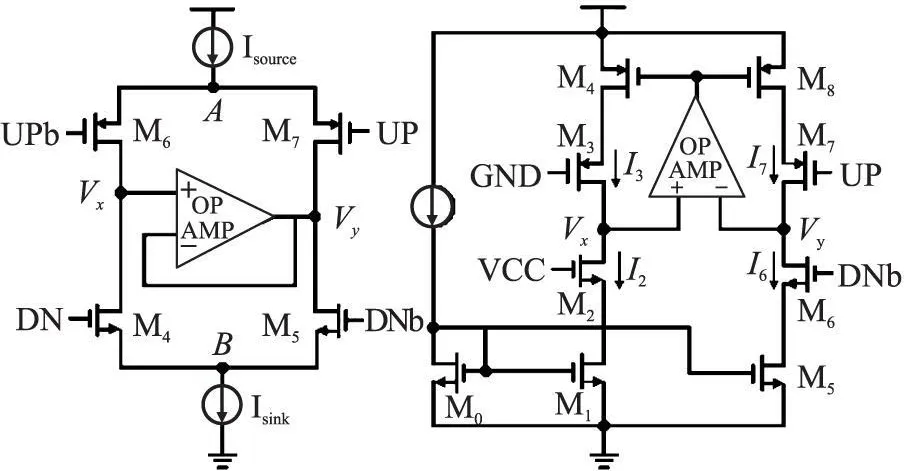

電荷泵電路上下兩個電流源Isink和Isource的匹配程度是電荷泵電路設計的關鍵。傳統的高性能電荷泵設計通常采用長溝道晶體管和Cascode技術來提高輸出電阻。但是,鎖相環在鎖定過程中, VCO控制電壓的變化范圍通常會接近于滿擺幅變化,這樣即便是長溝道晶體管和Cascode技術也不能完全克服溝道調制效應。圖5所示為傳統高性能電荷泵的設計方法。圖5(a)在四個開關管之間加入一個電壓跟隨器,利用運放高增益的特性使得Vx和Vy相等,從而來避免MOS開關管的溝道電荷分享效應[6]。在沒有運放的情況下,開關M4~M7的導通和關閉,A點和B點的電壓會發生跳變,這樣MOS管內的溝道電荷流入流出會使VCO的控制電壓會發生擾動,從而引起雜散。在M6導通, M7關閉的情況下, A點的電壓與Vx近似相等,電壓跟隨器使得Vy也近似相等于VA。這樣,開關管在導通和關閉的情況下,源漏電壓保持相等,從而減小了開關管的電荷分享問題。但是這種結構并不能保證上下尾電流源的匹配,圖5(b)所示的結構可以確保上下電流源的匹配性。其中, M1~M4是M5~M8的復制電路。只要高運算放大器的增益足夠高就可以保證Vx=Vy,這樣I2=I6, I3=I7。因為I6=I7,所以I6=I7=I3=I2,從而上下電流源的匹配性大大增強[7-9]。

圖5 傳統的電荷泵電路

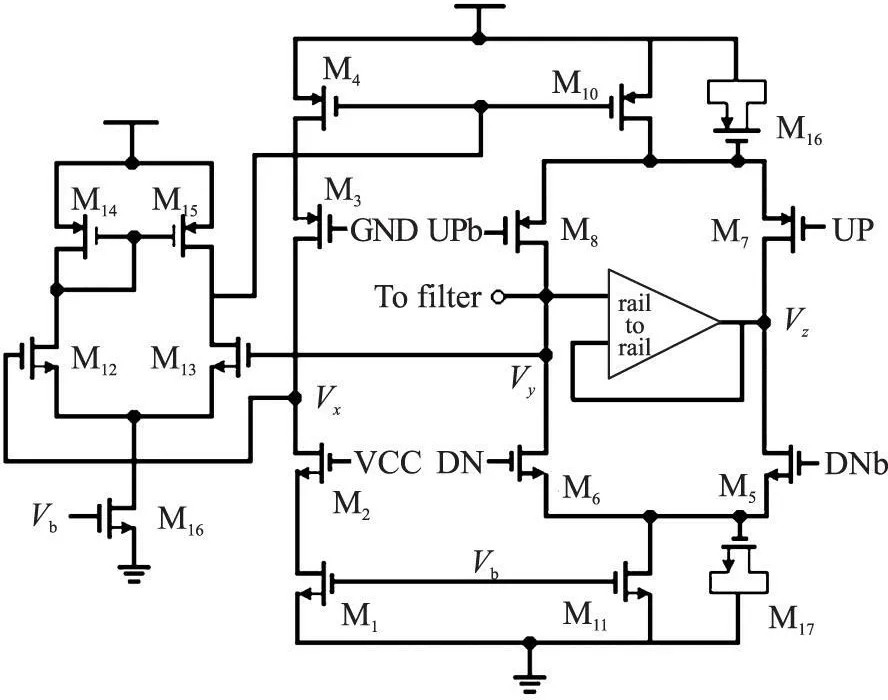

通過比較圖5兩種電路的優缺點,本文提出了一種新型的電荷泵電路,他把兩種電路結合起來,如圖6所示。在開關部分,同樣引入了如圖5(a)所示的dummy switches M7和M5來構成互補開關對。在互補開關的中間加入了一個高增益的軌對軌運放來減小電荷泵的電荷分享效應。M1~M4同樣是復制電路(Replica Bias),在設計時要確保M1=M11, M2=M6=M5, M3=M8=M7, M4=M10。 M12~M16構成運算放大器確保 Mx=My。在設計時需要注的是M13漏極的輸出直接連到M4和M10的柵極,這樣M12~M16和M10其實構成了一個兩級運算放大器,所以本文只采用了M12~M16構成一個最簡單的一級運算放大器。為了確保M10的柵極不振蕩需要對這個兩級運放進行頻率補償,常用的方法是在M10的柵極和漏極加上電阻和電容進行頻率補償(圖中未標出)。

圖6 本次設計采用的電荷泵電路

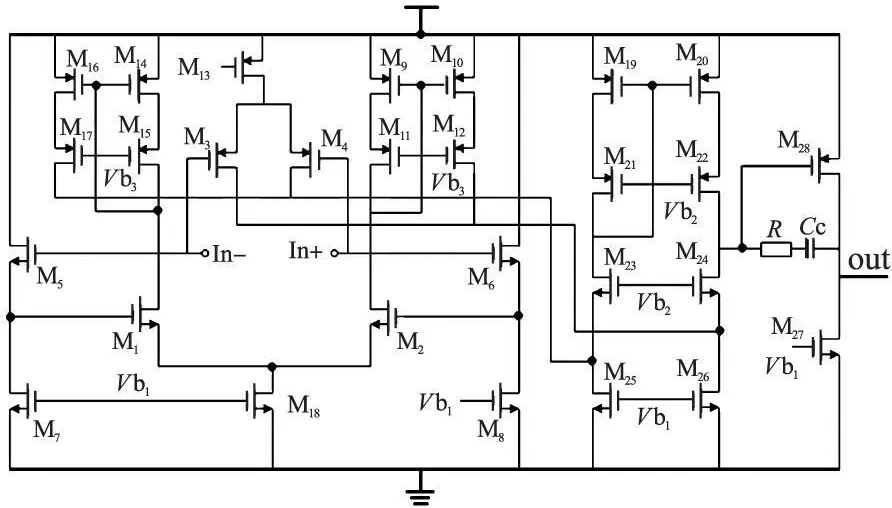

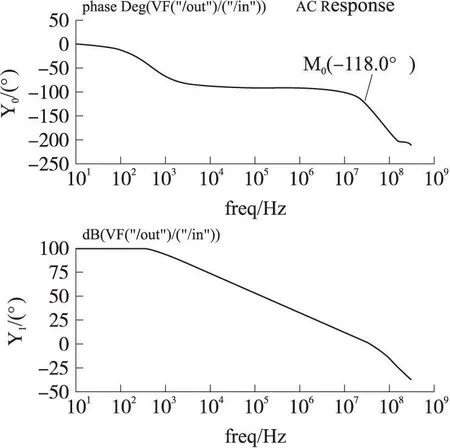

互補開關對中間的運放是個設計難點,因為它的輸出直接連到了VCO的控制端,所以它的輸入輸出擺幅必須要大,為此本文設計了一個如圖7 所示的輸入軌對軌的兩級運算放大器[10]。 M3和M4構成了PMOS的差分對管, M1和M2構成了NMOS的差分對管, M5~M8構成了Level Shift電路。通過合理選擇M5~M8的尺寸的大小可以滿足軌對軌的輸入擺幅。M19~M26形成共源共柵的折疊式運放,來獲得較高的增益。第二級采用了簡單的共源放大器的形式來增加輸出端的擺幅。在第一級和第二級之間加入R和Cc來達到頻率補償的目的。該運放的相頻響應和幅頻響應如圖8所示。

圖7 軌對軌運放

圖8 軌對軌運放仿真的波特圖

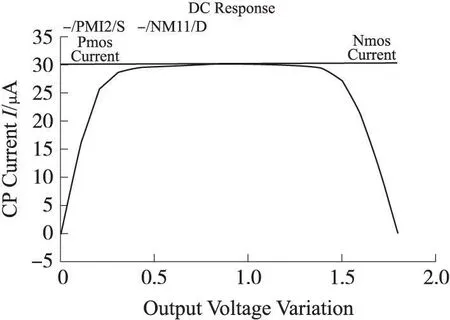

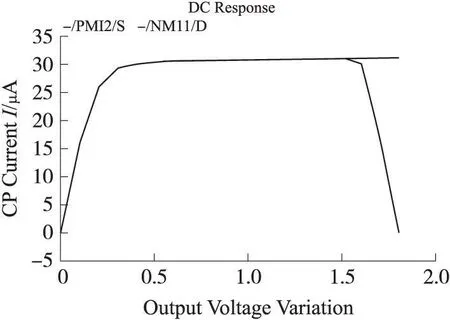

圖9 和圖10 分別是傳統電荷泵電路和本文所提出的新型電荷泵電路上下電流匹配程度的仿真結果。其中橫坐標表示電荷泵的輸出電壓,縱坐標表示電荷泵的輸出電流。從圖9中可以看出傳統的電荷泵電路只是在0.75 V~1.25 V之間時上下電流源的匹配程度好,在此區間之外,上下電流源有著明顯的失配,這是造成鎖相環雜散特性的主要原因。而圖10所示在0.3 V~1.5 V的范圍內,上下電流源均能保持良好的匹配性,擴大了VCO輸入信號的變化范圍。此外需要注意的是,本文提出的新型電荷泵電路比傳統的電荷泵電路要復雜,所以電荷泵本身會引入較多的噪聲,這就需要在環路帶寬的選擇上給予一定的考慮。

圖9 傳統電荷泵電路上下電流匹配度

圖10 本文電荷泵電路上下電流匹配度

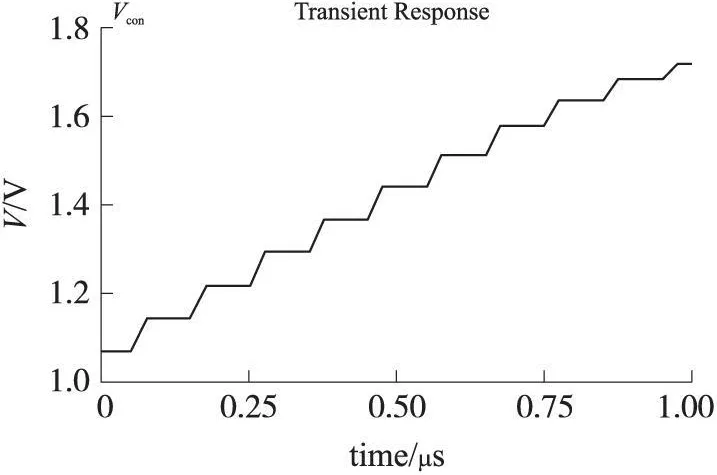

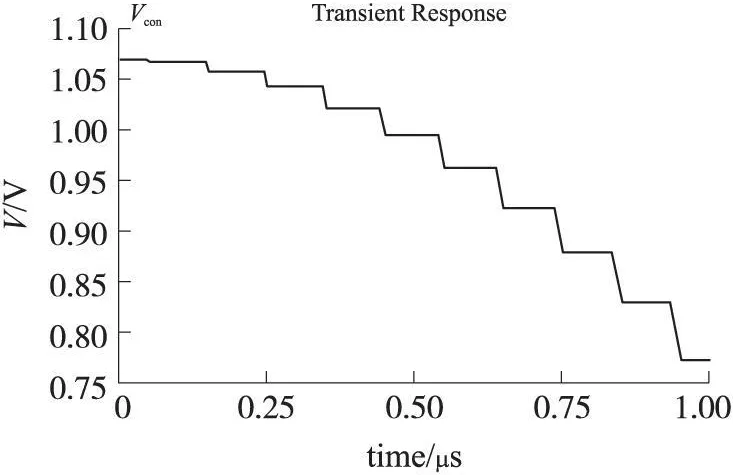

圖11 和圖12分別是本次設計電荷泵電路的充電和放電的仿真波形。從圖中可以看出該電荷泵電路工作正常,每次充電開始和結束的時刻,輸出電壓基本沒有毛刺。只有當充電接近電源電壓或是放電接近地的時候,輸出電壓出現小幅度的毛刺。這是因為此時電荷泵左邊的鉗制運放會有管子進入線性區,導致增益的下降。考慮本次設計的LC VCO采用的是開關電容陣列粗調和小尺寸MOS變容管細調相結合的結構,所以每次頻率合成器鎖定時VCO的控制電壓盡量設計在Vcc/2處。這樣不僅可以提高變容管的線性度,使環路穩定,而且可以確保電荷泵的性能。

圖11 本文電荷泵電路充電效果

圖12 本文電荷泵電路放電效果

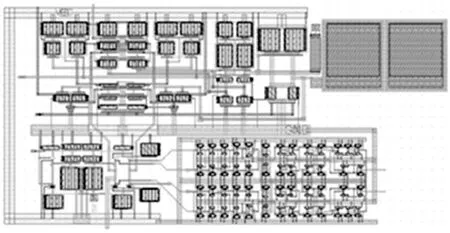

2 版圖設計

圖13所示為電荷泵電路和PFD的版圖.鑒相器和電荷泵電路都需要保持對稱性,在電荷泵版圖設計時要特別注意它開關管的設計。為克服開關管的非理想效應,在開關的旁邊通常加入了Dummy管。軌對軌運放的輸入對畫成了四方交叉結構,以輸入對降低不匹配和失調電壓對運放增益的影響。此外, PFD電路四路輸出信號UP、UPb、DN、和DNb信號到電荷泵開關上的離線長短要盡量保持相等,不然會引起額外的充放電動作,導致雜散效應變差。

圖13 鑒相器和電荷泵的版圖

3 總結

本文討論了鎖相環中鑒相器和電荷泵電路常見的非理想因素,并提出了克服辦法。在綜合傳統電路的基礎上,提出一種新型的電荷泵電路,仿真結果表明該電荷泵具有較高的電流匹配度。

[ 1] Gardner F.Charge-Pump Phase-Lock Loops.IEEE Trans.Commun, 1980, 28(11):1849-1858.

[ 2] Charles C T, JD Allstot.A Calibrated Phase Frequency Detector for Reference Spur Reduction in Charge-Pump Plls[ J] .IEEE Transcations on Circuits and Systems II:Express Briefs, 2006,53:822-826.

[ 3] Maneatis J.Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques[ J].IEEE J.Solid-State Circuits,1996, 31:1723-1732.

[ 4] Hung CM, Kenneth K O.A Fully Integrated 1.5-V 5.5-GHz CMOS Phase-Locked Loop[ J] .IEEE J.Solid-State Circuits,2002, 37:521-527.

[ 5] Lam C, Razavi B.A 2.6-GHz/5.2-GHz Frequency Synthesizer in 0.4um CMOSTechnology[ J] .IEEE J.Solid-State Circuits,1996, 31:1723-1732.

[ 6]Yang Zhenyu, Tang Zhangwen, Hao Min.A Fully Differential Charge Pump with Accurate Current Matching and Rail-to-Rail Common-Mode Feedback Circuit[M].IEEE Int.Symp.Circuits Syst, 2008, 448-415.

[ 7]Rhee W.Design of High-Performance CMOS Charge Pumps in Phase-Locked Loops[ M] .In Proc.IEEE Int.Symp.Circuits Syst.May, 1999, 2:363-366.

[ 8] Lee J, Kell M, Kim S, et al.Charge Pump with Perfect Current Matching Characteristics in Phase Lock Loops[ J] .IEEE Electronic Letters, 2000, 36(11):1907-1908.

[ 9] Cheng Shanfeng, Tong Haitao.Design and Analysis of an Ultrahigh-Speed Glitch-Free Fully Differential Charge Pump with Minimum Output Current Variation and Accurate Matching[ J] .IEEE Transcations on Circuits and Systems II:Express Briefs, 2006,53:843-847.

[ 10] Wang Minsheng.Constant-Gm Rail-to-Rail CMOSOp-Amp Input Stage with Overlapped Transition Regions[ J] .IEEE J.Solid-State Circuits, 1999, 34:148-156.