數字脈沖應答機的時延補償方法

(中國西南電子技術研究所,成都 610036)

1 引 言

單脈沖相參應答機的基本功能是相參轉發單脈沖地面雷達上行信號,與地面雷達協同工作,完成飛行器軌道測量。地面雷達通過測量飛行器應答機轉發信號的時延完成飛行器距離的測量[1]。因此,要求應答機轉發時延穩定。

在傳統模擬體制脈沖應答機設計中,脈沖延遲選用聲表面波延遲線,這種延遲線插損大,延遲時間隨溫度變化較大,帶來調試難、生產性差、時延不穩定等缺點,嚴重影響到地面雷達的測距精度。為了克服模擬體制脈沖應答機的缺點,脈沖相參應答機采用了數字化設計,運用數字存儲轉發和數字時延補償技術,可大大提高脈沖應答機轉發時延的穩定性。該數字化脈沖相參應答機具有延遲時間易修改、控制精度高、可靠性高、生產性好、小型化和使用靈活等優點。

本文主要介紹了單脈沖應答機數字終端設計,對轉發精度進行了分析,提出了數字化時延補償技術,并針對實際應用工程,給出了試驗測試結果。

2 數字化終端設計

單脈沖相參應答機與地面雷達站合作實現高精度測距,關鍵是控制應答機的轉發延時精確。采用基于FPGA的數字存儲轉發技術,可容易實現高精度的時延補償,能大大提高應答機的轉發精度。

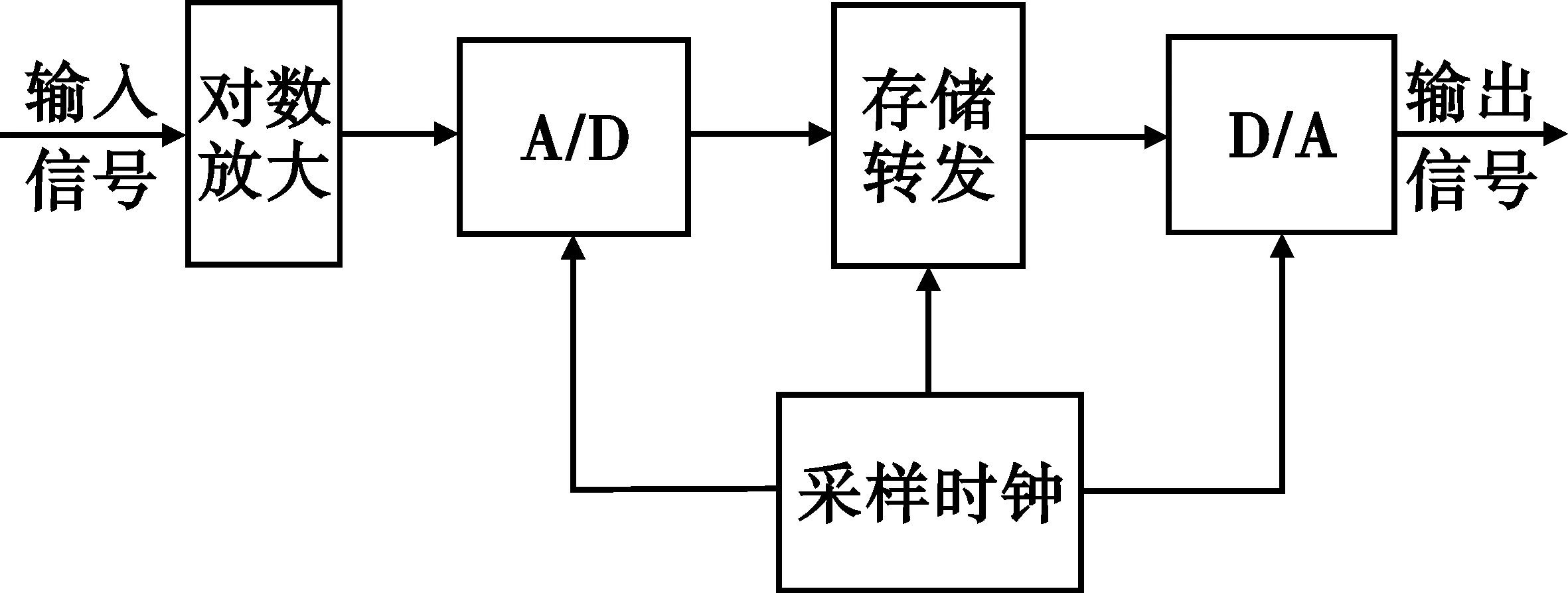

數字化終端的實現原理框圖如圖1所示。其信號流程為:接收高放模塊送來的中頻信號,經對數放大,壓縮接收信號的動態范圍和中頻檢波,再經過A/D采樣后,直接送到FPGA進行數字化設計,采用數字存儲方式精確控制轉發延時時間,經D/A變換器輸出中頻轉發信號。

圖1 數字存儲轉發原理框圖Fig.1 The functional diagram of digital store and forward technique

如何實現存儲轉發功能,是數字化終端設計的關鍵。終端的存儲轉發器采用FPGA實現,利用數據同步時鐘作為寫信號,將送入FPGA的數字數據寫入RAM或FIFO芯片中,再用本級采樣時鐘將數據讀出,從而實現數字接口同步以及輸入、輸出延時可變的靈活設計。通常,雙口RAM的端口控制比FIFO更靈活,由地址線就可完成讀取或存儲數據要求,故本數字終端選用雙口RAM實現數據同步和延時轉發存儲功能。針對實際工程應用中雙口RAM的參數設計,應根據A/D和D/A的位數、中頻調制脈沖信號的脈寬τ以及A/D采樣時鐘fs的關系綜合計算出需要的存儲器位寬和深度。

該數字終端的存儲轉發器各參數可通過程序靈活設置,實現了應答機時延可控,以便滿足不同任務需求;同時,轉發延時時間可控制在1個時鐘周期內,大大提高了應答機脈沖轉發的延時精度。

3 延時轉發精度分析

根據脈沖信號測距原理,地面雷達通過測量脈沖信號傳播時間計算目標距離[2]:

(1)

式中,c為電波傳播速度,τ是傳播時間。

實際得到的信號傳播時間包括信號空間傳播時間、應答機轉發信號延時時間和信號在地面雷達系統信道中的傳播時間,而應答機轉發延時時間穩定性是確保地面雷達測距精度的關鍵。

應答機轉發延時時間誤差主要包括熱噪聲引入的轉發脈沖前沿抖動、系統時鐘漂移以及信號電平變化產生的轉發脈沖前沿漂移等。

(1)噪聲帶來的延時誤差Δτ1

脈沖應答機接收到脈沖信號后,接收信道和接收機中存在熱噪聲,含有噪聲的信號進入視頻放大器和門限電路時,脈沖信號前沿就會疊加噪聲電壓,使脈沖觸發不穩定,從而造成了延時誤差,這種延時具有隨機分布的特點,如圖2所示。

圖2 噪聲引入的延時誤差Fig.2 Time delay error vs received noise

(2)時鐘漂移的時延誤差Δτ2

系統時鐘漂移會引起A/D采樣數據抖動,從而導致各種控制脈沖的計數誤差,時鐘漂移引起的時延最大誤差不超過1個時鐘周期,若系統采樣時鐘為fs,則時延誤差為Δτs=1/fs。

(3)電平變化引起的時延誤差Δτ3

為了適應飛行器測距需要,脈沖應答機接收信號需滿足一定的動態范圍要求,即應答機接收信號的電平是距離的函數,應答機離地面雷達站越遠,其接收信號電平越低,反之亦然。接收信號電平的變化會導致檢波器輸出信號包絡電平隨之發生變化,而脈沖信號檢波包絡判決門限設置固定,弱信號和強信號對應的觸發判決電平時間會不同,造成時間延時誤差。當信號增強時,檢波包絡判決觸發點時間向前移動,具體變化規律如圖3所示。

圖3 接收電平變化帶來的延時Fig.3 Time delay vs the received signal level

導致這種現象的原因是中頻脈沖調制信號經過濾波器后,因濾波器的帶寬限制,濾除了脈沖信號中的高頻分量部分,使脈沖信號的沿發生畸變。畸變后的脈沖經過固定判決電平判讀后,脈沖前沿產生漂移。

脈沖應答機轉發時延誤差主要有兩種類型,一種是恒定的和慢漂移誤差,另一種是具有隨機特性和起伏特性誤差。后者是無法校正的,會引起隨機的測距誤差,噪聲帶來的延時誤差Δτ1就屬于此種情況。而前者針對恒定的或有規律的慢漂移誤差,可以在測距系統中利用系統校正措施進行補償或消除,時鐘漂移誤差Δτ2和信號電平變化帶來的延時誤差Δτ3屬于此種情況。針對Δτ2,可以利用提高系統時鐘頻率和頻率穩定度指標措施,減少該項誤差;針對Δτ3,主要采用數字化時延補償技術進行補償。

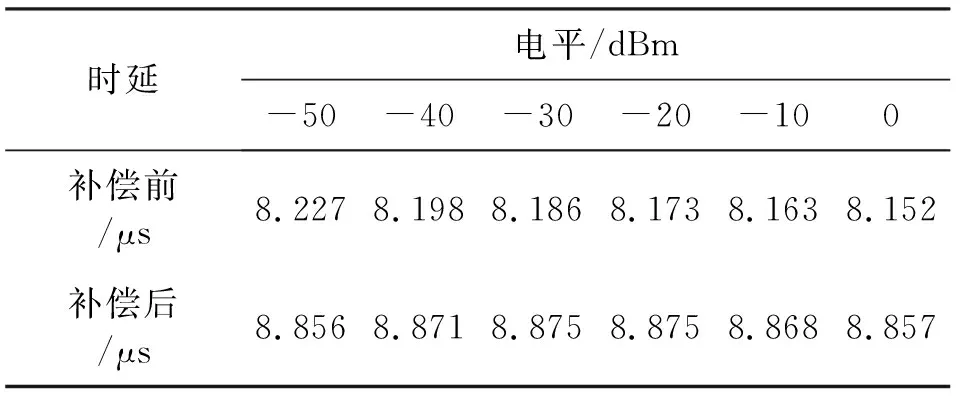

表1是某項工程中針對電平變化引起應答機時延變化情況的測試數據結果。測試條件為:未采用時延補償技術,動態范圍為50 dB,采用時間間隔儀測試應答機的轉發時延。

表1 電平變化引起的時延變化表Table 1 Value of time delay vs the received signal level

從試驗測試數據可知,在整個接收信號的動態范圍內,電平變化引起的時延誤差Δτ3=75 ns,這個指標遠遠不能滿足系統使用要求,需改善設計。

4 時延補償方法

針對數字化脈沖應答機終端信號電平變化引起的時延較大,需采用相應的技術補償措施,提高脈沖應答機的時延轉發精度。針對該脈沖應答機,主要采用的技術補償措施有如下幾種。

(1)增加濾波器帶寬

檢波前濾波器的帶寬會影響接收脈沖前沿的抖動。根據工程研制經驗可知,若濾波器帶寬增加一倍,其脈沖前沿的延時變化可減小一半[3];但濾波器帶寬變寬,會增加濾波器帶內噪聲,惡化后端信號信噪比,因此,在選擇濾波器帶寬方面需要進行折衷考慮。

(2)數字化時延補償方法

針對脈沖應答機的時延變化,還可采用數字化補償措施。該補償方法主要是利用對數放大器檢波脈沖的能量,根據實測能量結果實時完成時延誤差的補償。在實現上采用低速A/D采樣+查找表的設計方案,即根據檢波脈沖能量,查找相應的時延補償量進行補償。

第一種方法在設備研制前就需完成,根據設計的信號信噪比和時延變化誤差量,選擇合理的濾波器帶寬。由于器件性能的不一致性會導致不同設備接收信號的信噪比、時延變化出現差異,因此,采用該方法缺乏靈活性。第二種方法能根據不同系統的精度要求、設備個體差異有針對性地設計延時查找表,靈活調整應答機的高、中、低轉發精度。因此,針對實際研制的數字化脈沖應答機,優先選擇數字化時延補償方法。

數字化時延補償方法的具體實現過程為:將檢波脈沖進行A/D采樣,在FPGA內部設計一個查找表,根據A/D采樣的數字幅度,查詢延時的變化量,查找表深度根據轉發精度的要求設定[4]。根據工程經驗,選擇A/D采樣速率大于10倍脈寬即可滿足系統精度要求,有效位數根據系統的動態范圍進行選擇,其實現框圖如圖4所示。

圖4 時延補償的實現框圖Fig.4 The implementation block diagram of time delay compensation

通過以上分析知,信號處理補償技術設計更靈活,控制精度更高,因此在具體實現上選擇數字化時延補償方式。

5 測試結果

表2是采用數字化時延補償方法前后測試結果對照表。從表中可知,脈沖應答機接收信號的動態范圍為50 dB,在采用補償技術前,脈沖應答機接收整個動態范圍內的脈沖信號最大延時誤差達到75 ns;采用數字化補償技術后,可將脈沖延時誤差減小到19 ns,大大提高了脈沖應答機的延時轉發精度。

表2 數字化時延補償方法前后的時延誤差比對表Table 2 Comparison of time delay errors before and after digital time delay compensation

6 結束語

脈沖應答機在配合地面雷達完成目標測距任務過程中,要求應答機具有高的信號延時轉發精度。數字化脈沖相參應答機采用基于FPGA的數字存儲轉發技術,并結合查找表的高精度時延補償方法,可大大提高應答機的測距精度,對實際工程應用具有借鑒價值。

參考文獻:

[1] 趙樹強,許愛華,胡紹林. 脈沖雷達高仰角測量數據分析及處理對策[J].飛行器測控學報,2003,22(4):67-70.

ZHAO Shu-qiang,XU Ai-hua,HU Shao-lin. Measurement Data Analysis and Processing Counterplan of the High Elevation Angle of Pulse-Radar[J].Journal of spacecraft TT&C Technology, 2003,22(4):67-70.(in Chinese)

[2] 丁鷺飛,耿富錄.雷達原理[M]. 西安:西安電子科技大學出版社,2002.

DING Lu-fei,GENG Fu-lu.Radar Princple[M].Xi′an:Xidian University Press,2002. (in Chinese)

[3] 廖承恩.微波技術基礎[M]. 西安:西安電子科技大學,1995.

LIAO Cheng-en.Microwave Technology [M]. Xi′an:Xidian University Press,1995. (in Chinese)

[4] 張海燕,李欣,田書峰. 基于BP神經網絡的仿真線設計及其FPGA實現[J].電子與信息學報,2007,29(5):1267-1270.

ZHANG Hai-yan,LI Xin,TIAN Shu-feng. Simulation Line Design and Its FPGA Realization Based on BP Neural Network[J]. Journal of Electronics & Information Technology,2007,29(5):1267-1270.(in Chinese)