CMOS集成電路閂鎖效應抑制技術

董麗鳳,李艷麗,王吉源

(江西理工大學信息工程學院,江西 贛州 341000)

CMOS集成電路閂鎖效應抑制技術

董麗鳳,李艷麗,王吉源

(江西理工大學信息工程學院,江西 贛州 341000)

閂鎖效應是CMOS集成電路在實際應用中失效的主要原因之一,而且隨著器件特征尺寸越來越小,使得CMOS電路結構中的閂鎖效應日益突出。文章以P阱CMOS反相器為例,從CMOS集成電路的工藝結構出發,采用可控硅等效電路模型,較為詳細地分析了閂鎖效應的形成機理,給出了閂鎖效應產生的三個基本條件,并從版圖設計和工藝設計兩方面總結了幾種抑制閂鎖效應的關鍵技術。

CMOS集成電路;閂鎖效應;可控硅;抑制

1 引言

CMOS(Complementary Metal-Oxide-Semiconductor)集成電路是目前大規模(LSI)和超大規模(VLSI)集成電路中廣泛應用的一種電路結構,相對于傳統的雙極型、NMOS和PMOS集成電路而言,其在功率消耗、噪聲抑制等方面具有明顯的優勢,雖然CMOS電路具有以上眾多優點,但也有一些由于自身結構引發的寄生效應限制了其優越性的充分發揮,隱含于體硅CMOS(指在硅襯底上制作的CMOS)結構中的閂鎖效應就是一個最典型的例子,并且隨著器件尺寸的不斷縮小,閂鎖效應對電路性能的影響將愈發明顯。

2 閂鎖效應及其形成機理

閂鎖效應(latch up)是指在體硅CMOS結構中,從電源到地存在的PNPN寄生可控硅結構,在滿足可控硅觸發條件下,引起電源到地的極大電流,破壞電路正常工作乃至燒毀整個電路的現象,也稱自鎖效應。閂鎖效應往往發生在芯片中某一局部區域,有兩種情況:一種是閂鎖只發生在外圍與輸入輸出有關的地方,另一種是閂鎖可能發生在芯片的任何地方,在使用中前一種情況遇到較多。

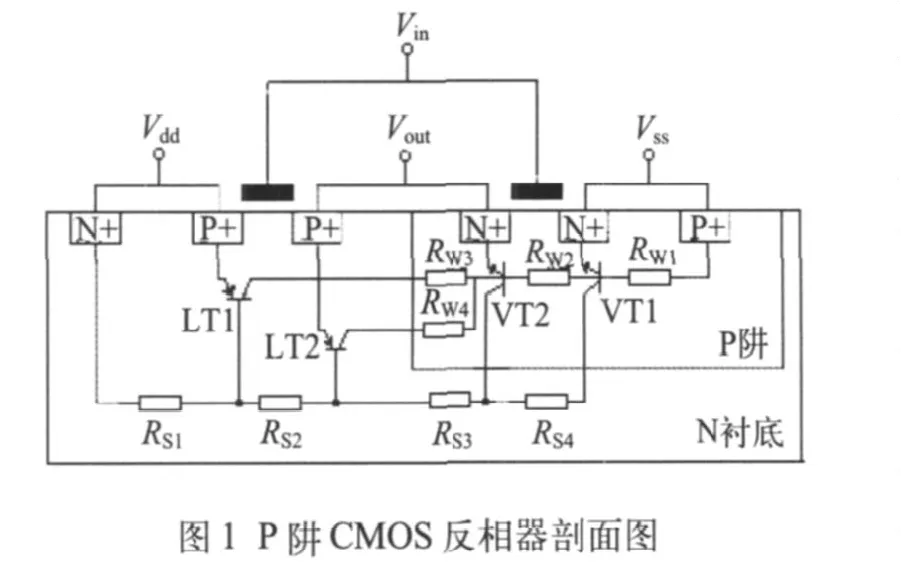

下面以一個P阱CMOS反相器為例,來說明閂鎖效應的形成機理[1-2]。圖1是CMOS反相器的剖面圖。從圖1中我們可以看出,在形成CMOS反相器結構的同時,也不可避免地產生了由寄生雙極晶體管構成的PNPN器件,即可控硅(SCR),該可控硅器件由兩個橫向的PNP雙極型晶體管和兩個縱向的NPN雙極型晶體管組成,即P溝道MOSFET的源(漏)極、N型襯底以及P阱分別為橫向PNP雙極晶體管LT1(LT2)的發射極、基極和集電極;N溝道MOSFET的漏(源)極、P阱及N型襯底分別為縱向NPN雙極晶體管VT1(VT2)的發射極、基極及集電極,這種寄生的縱向NPN晶體管和橫向的PNP晶體管通過P阱和共同的襯底耦合。

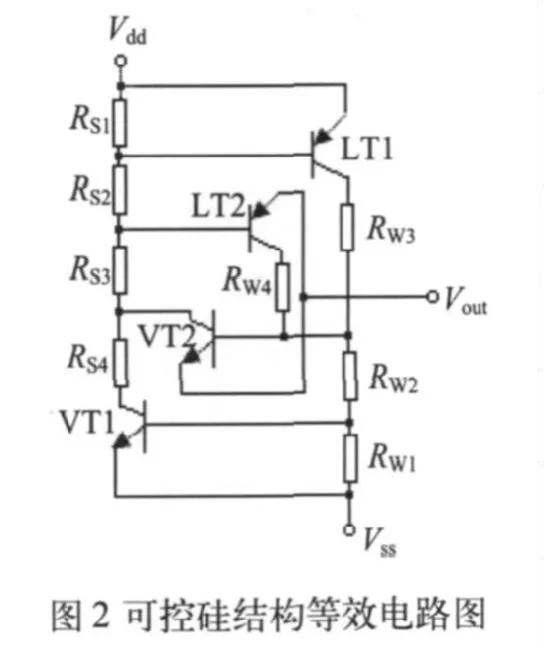

因此我們可以得到寄生可控硅結構的等效電路圖,如圖2所示。

從圖2中可以看出,雙極晶體管VT2、LT2可以不予考慮,因此可以將該電路進行簡化,得到簡化的可控硅結構等效電路圖,如圖3。由寄生部分的等效電路圖分析閂鎖效應發生的條件。由圖3可見寄生電路在LT1和VT1之間形成了一個正反饋回路,在正常情況下,由于Vdd與Vss之間有一個反偏的阱與襯底PN結隔離,只有很小的二極管漏電流在其間流過,不會對反相器正常工作產生影響。但當CMOS集成電路接通電源后,如果在A點有電流注入,會使節點電壓VA上升,即NPN管VT1的VBE增大,當VBE增大到一定程度時(>0.7V),縱向NPN晶體管VT1會導通而進入放大區,導致IC2增大,故使得VB下降,VB下降則LT1的VBE也增大,導致|IC1|增大,最終導致VA進一步上升,一旦LT1和VT1之間形成的正反饋回路增益大于或等于1,上述過程將持續下去,直至兩個晶體管完全導通,在Vdd與Vss之間產生很大的電流。此時,即使A點的注入電流消失,Vdd與Vss之間的電流仍然存在,這就是閂鎖效應的形成過程。

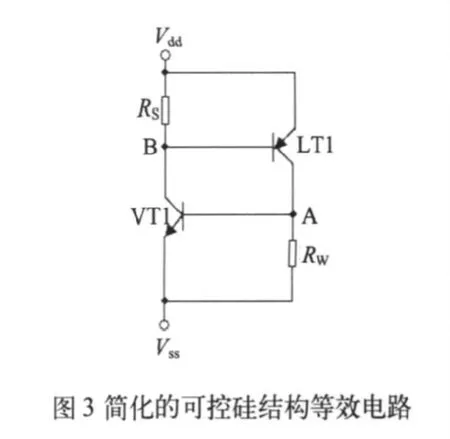

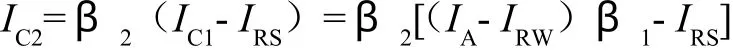

下面導出產生閂鎖效應的條件,假設NPN管的共射電流增益為β1,PNP管的共射電流增益為β2,A點的注入電流為IA。根據射、集、基極的電流關系有:IA=IRW+IB1,IC1=β1IB1,IC1=IRS+IB2,IC2=β2IB2,所以:

式中IRW、IRS較小,因此有:IC2≈β1β2IA。

若β1β2>1,則IA的反饋量IC2>IA。這樣兩個寄生管同時工作,形成正反饋回路,加深了可控硅導通,在電源和地之間形成極大的導通電流,并使電源和地之間鎖定在一個很低的電壓,即該電路被閂鎖。

由上述分析可總結出產生閂鎖效應的三個基本條件,即:

(1)環路增益必須大于1,即βNPN×βPNP≥1;

(2)橫向PNP管和縱向PNP管的發射結都被加正偏電壓;

(3)電源所提供的最大電流大于寄生可控硅導通所需要的維持電流。

3 閂鎖效應的抑制技術

由以上分析可知,閂鎖效應起因于寄生的可控硅結構,且其發生需具備一定的條件,因此只要破壞產生閂鎖效應的三個基本條件或其中之一,就能有效地避免閂鎖的發生。在實際應用中,通常可從版圖和工藝等方面采取措施,消除閂鎖效應的發生。

3.1 版圖設計考慮

3.1.1 保護環技術

由產生閂鎖效應的基本條件可知,減小電阻RS和RW,降低寄生三極管的電流放大倍數βNPN,βPNP,可有效提高抗閂鎖的能力。因此,可以通過在版圖設計中引用保護環技術[3]來實現減小襯底電阻RS和阱區電阻RW的目的。圖4為增加了保護環的反相器剖面圖。

從圖中看出所謂保護環即是在N襯底區P溝道器件的周圍加上接電源Vdd的N+環;在P阱區N溝道器件的周圍加上接Vss的P+環。

3.1.2 合理布局電源接觸孔

合理布局電源接觸孔,可以降低橫向電流密度和襯底電阻RS,減小寄生晶體管的放大倍數, 同樣可以達到抑制閂鎖的目的。需注意的問題如下[4]:

(1)采用接襯底的環形Vdd電源線(P阱),并盡可能將襯底背面接Vdd;

(2)增加電源Vdd和Vss接觸孔,并盡可能加大接觸面積;

(3)P阱CMOS中接Vdd的孔盡可能安排的離阱遠一些,接Vss的孔要盡可能安排在阱的所有邊緣上。同時對每一個接Vdd的孔都要在相鄰的阱中配以對應的Vss接觸孔,并盡量使Vdd和Vss的接觸孔的長邊相互平行。

3.2 工藝方面考慮

3.2.1 外延襯底技術

外延襯底技術[5]主要是通過減小襯底電阻RS達到抑制閂鎖的目的。普通N型襯底工藝是將整個電路做在一個低摻雜的N-型襯底上,使得襯底電阻RS較大,外延襯底則是采用雙層襯底,即在低摻雜的N-型襯底下方還有一層較高摻雜的N+襯底,以此大大減小了襯底電阻RS,增加了閂鎖的預防水平。

3.2.2 倒退阱

類似于高注入的襯底,倒退阱可以降低阱的電阻RW,防止縱向的寄生三極管開啟。制作倒退阱有多種方法,如埋層的外延層,高能離子注入及反型雜質的注入等。

3.2.3 溝槽隔離

所謂溝槽隔離就是在PN有緣區之間形成一個絕緣的槽體,絕緣物質通常為二氧化硅,以此來降低橫向三極管的增益,削弱NMOS晶體管和PMOS晶體管之間可能形成的寄生連接,從而起到預防閂鎖的作用。槽的深度越深,對閂鎖的防治效果就越好。

3.2.4 SOI技術

SOI工藝技術是指在表層與襯底之間加入一層絕緣層,由于有了更高的阻抗,使電子遷移不會傳到下層,使電子束或電子本身的遷移速度加快,從而提高了整個芯片的性能,使芯片速度更快、耗電更少、電路密度更高。由于絕緣層的存在,阻斷了PNPN放電路徑的形成,從根本上避免了閂鎖的形成。

4 結束語

隨著CMOS集成電路的飛速發展,芯片上的器件尺寸越來越小,閂鎖效應的預防問題變得愈發重要,因此需盡可能地避免、降低或消除閂鎖效應的形成,從而為CMOS電路的廣泛應用奠定基礎。

[1]牛征.CMOS電路中的閂鎖效應研究[J].電子與封裝,2007,3.

[2]錢敏等.CMOS集成電路抗閂鎖策略研究[J].集成電路應用,2005,2.

[3]唐曉峰等.CMOS電路抗閂鎖研究[J].微處理機,2009,2.

[4]朱正涌.半導體集成電路[M].北京:清華大學出版社,2000.

[5]艾倫等著,馮軍等譯.CMOS模擬集成電路設計[M].北京:電子工業出版社,2005.

Overview on the Prevention of Latch-up Effect in CMOS IC

DONG Li-feng, LI Yan-li, WANG Ji-yuan

(Jiangxi University of Science and Technology,Ganzhou341000,China)

Latch-up effect is one of main cause that CMOS IC becomes invalid in application, and as device channel length becomes smaller and smaller, Latch-up effect in CMOS structure is stand out increasingly. Based on CMOS inverter in P-well, the structure of CMOS IC are presented.SCR equivalent circuit model is took to analyze the mechanism of latch-up in detail, gives three main conditions that latch-up becomes and sums up several kinds of key technology in prevention from layout and process.

CMOS IC; latch-up effect; SCR; prevention

TM341

A

1681-1070(2010)09-0028-03

2010-04-16

董麗鳳 (1981-),女,遼寧錦州人,2007年遼寧大學畢業,碩士,助教,研究方向為微電子學與固體電子學。