基于FPGA和DSP的擴頻信號發(fā)生器設(shè)計與實現(xiàn)

王 杰, 康 瀟

(民航河南空管分局, 河南 鄭州 451162)

0 引言

數(shù)字多波束天線擴頻通信系統(tǒng)作為一種具有較強的抗干擾能力和低信噪比門限的相關(guān)接收特性的通信體系,是現(xiàn)代通信領(lǐng)域的一個重要發(fā)展方向。我們在調(diào)試數(shù)字多波束天線擴頻通信系統(tǒng)時必要要用到專門設(shè)計的擴頻信號發(fā)生器,因此提出一種擴頻信號發(fā)生器實現(xiàn)方案。

1 擴頻信號產(chǎn)生原理及系統(tǒng)方案

擴頻通信可以顯著提高通信系統(tǒng)抗干擾的能力,特別是頻率選擇性衰落和多徑干擾。為此在發(fā)端輸入的信息先經(jīng)信息調(diào)制形成數(shù)字信號,然后由擴頻碼發(fā)生器產(chǎn)生的擴頻碼序列去調(diào)制數(shù)字信號以展寬信號的頻譜。展寬后的信號再調(diào)制到射頻發(fā)送出去[1]。一般的擴頻通信系統(tǒng)都要進行三次調(diào)制,一次調(diào)制為信息調(diào)制,二次調(diào)制為擴頻調(diào)制,三次調(diào)制為射頻調(diào)制。在擴頻通信中需要用高碼率的窄脈沖序列,即偽隨機碼或簡稱 PN碼。這類碼序列最重要的特點是近似噪聲的特性。但是真正的隨機序列是不可能重復(fù)和產(chǎn)生的,因此我們只能產(chǎn)生一種類

周期性的脈沖信號來近似噪聲的特性,二元M序列是一種最常見的偽隨機序列我們采用它作為我們的擴頻序列[3]。

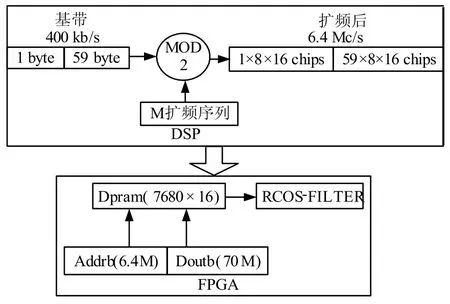

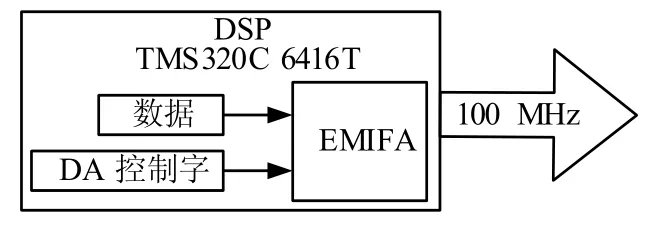

在硬件平臺上,本系統(tǒng)(見圖1)采用TI公司的TMS320C 6416T,它的主頻最高可達 600 MHz,可以滿足高性能數(shù)字信號處理的要求,故我們采用它作為主處理器來實現(xiàn)用戶數(shù)據(jù)擴頻和D/A控制字的設(shè)置[2]。

圖1 系統(tǒng)方案框

擴頻中使用128位大M序列,擴頻碼數(shù)據(jù)速率6.4 Mc/s。為了便于之后對中頻載波進行調(diào)制,我們把碼速率插值到70M樣本/秒,之后經(jīng)過余弦滾降濾波器濾波后使用BPSK調(diào)制方式調(diào)制到中頻70 MHz[2]。數(shù)據(jù)流程見圖2。

圖2 數(shù)據(jù)流

2 硬件接口設(shè)計

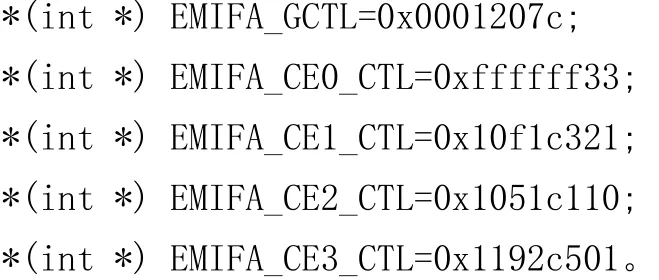

DSP訪問片外存儲器必須通過外部存儲器接口(External Memory Interface,EMIF)。C6416的 EMIF具有很強的接口能力。C64xx提供 2個獨立的 EMIF:EMIFA和EMIFB。EMIFA提供64bit寬度的外總線數(shù)據(jù)接口,EMIFB提供16bit寬度的外總線數(shù)據(jù)接口。EMIF的時鐘ECLKOUTn是基于EMIF輸入時鐘在內(nèi)部產(chǎn)生的。

為了保證DSP與FPGA的數(shù)據(jù)傳輸能夠穩(wěn)定進行,它們之間的連接通過EMIFA實現(xiàn)。EMIF接口設(shè)計的一個重要問題就是根據(jù)PCB板的布線情況來調(diào)整一些重要的延時,具體控制寄存器設(shè)置如下:

接口設(shè)計中的 FPGA端要根據(jù) EMIFA的時序圖來編寫FPGA的接口模塊。圖3為C6416與Vetrix2接口的寫時序圖,根據(jù)這個時序圖可以編寫FPGA中接口的時序:

圖3 C6416與Vetrix2接口的寫時序

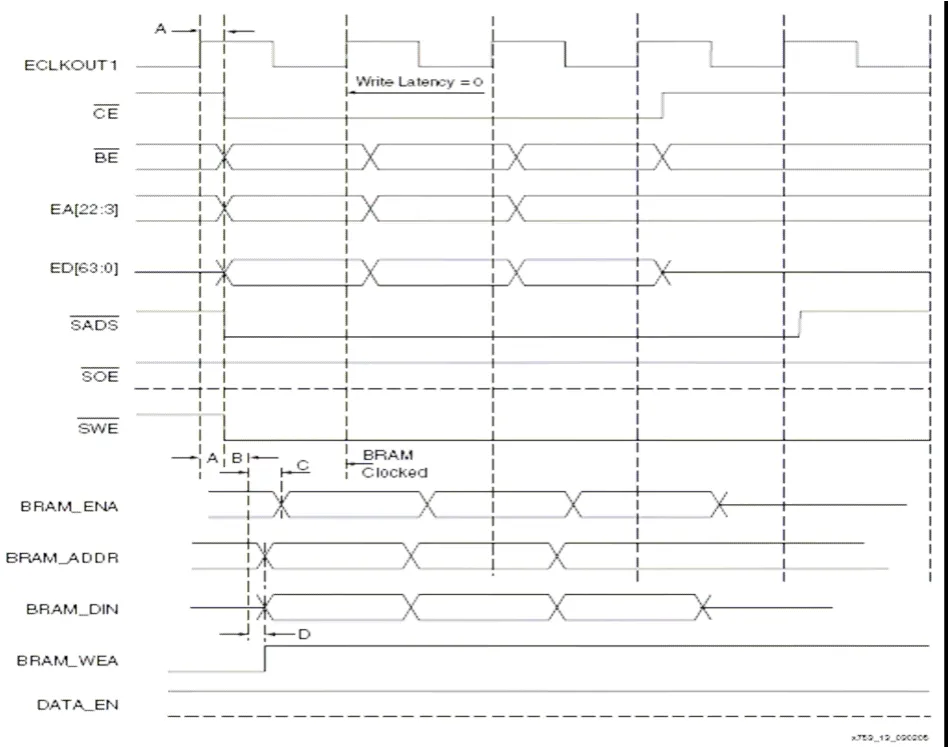

AD9777與FPGA通信使用SPI接口。它可以支持四根信號線:時鐘信號線SCLK, 使能信號CS,串行數(shù)據(jù)輸入輸出端口 SDIO,串行數(shù)據(jù)輸出端口 SDO。其中可以只選用前三根信號線而不選用第四根SDO信號線。AD9777在SPI的通信協(xié)議的內(nèi)容包括:

①SDIO的數(shù)據(jù)在SCLK的上升沿被采樣;

②SDIO的數(shù)據(jù)在SCLK的下降沿被改變;

③SCLK在空閑狀態(tài)下,可以為高電平也可以為低電平;

④串行傳輸過程中,MSB模式的時序。

根據(jù)AD9777的串口時序圖和DSP的EMIFA的端口時序設(shè)計這個模塊,實現(xiàn)了DSP對AD9777控制參數(shù)的設(shè)置。使用EMIFA的輸出時鐘aeaclkout1分頻產(chǎn)生SPI端口(見圖4)使用的spiclk用于控制移存器把從DSP收到的16位寬的數(shù)據(jù)aed轉(zhuǎn)換為1位寬的串行數(shù)據(jù)spi_sdio。使用EMIFA的地址輸出aea控制SPI端口使能spicsb,spicsb為低電平時輸出串行數(shù)據(jù)spicsb。

圖4 SPI模塊結(jié)構(gòu)

3 軟件設(shè)計

3.1 DSP控制和數(shù)據(jù)生成

DSP部分的主要功能是對用戶數(shù)據(jù)擴頻,控制AD9777的工作方式,其結(jié)構(gòu)如圖5。

圖5 DSP部分功能示意

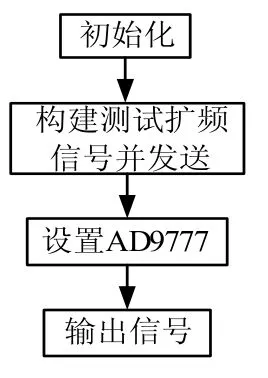

DSP部分程序有main.c,signal_gen.c。main.c的功能是產(chǎn)生擴頻序列,同時控制AD9777調(diào)制生成BPSK信號,流程如下頁圖6。

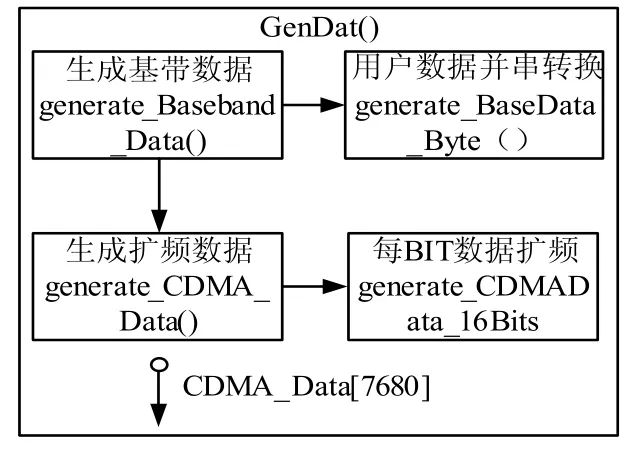

signal_gen.c的主要函數(shù)是GenDat(),功能是實現(xiàn)對用戶數(shù)據(jù)的訓(xùn)練序列插入并擴頻處理,程序流程如下頁圖7。其中函數(shù) void generate_BaseData_Byte(unsigned char Dat , char* dp)實現(xiàn)把char類型的并行數(shù)據(jù)轉(zhuǎn)換為bit流形式的串行數(shù)據(jù)。并且為了便于實現(xiàn)BPSK調(diào)制,我們使用了雙相不歸零碼,這樣與載波相乘即可完成 BPSK調(diào)制。

圖6 main.c軟件流程設(shè)計

圖7 GenDat()內(nèi)部流程

擴頻時,把采用的128位M序列存貯于數(shù)組中,利用查表進行相乘直接實現(xiàn)擴頻,擴頻序列可調(diào),性能穩(wěn)定可靠。

在本系統(tǒng)的應(yīng)用中,AD9777的輸入時鐘70M,數(shù)據(jù)速率70 MHz,載頻70 MHz,根據(jù)芯片資料提供的最佳參數(shù)設(shè)置,我們設(shè)置PLL2倍頻,進行2倍插值,fs/2調(diào)制,經(jīng)過實驗證明,這樣的參數(shù)設(shè)置可以提供最優(yōu)的信號輸出。

3.2 .FPGA處理部分

本系統(tǒng)采用Verilog硬件描述語言,RTL級描述了系統(tǒng)功能。FPGA中模塊的劃分如圖8所示。

4 設(shè)計的調(diào)試結(jié)果

圖9為在Chicoscope中觀測到的進入升余弦滾降濾波器之前的碼型和經(jīng)過升余弦滾降濾波器之后送往 AD9777的碼型。經(jīng)過系統(tǒng)的調(diào)試和使用證明這是一種成功的擴頻信號發(fā)生器。

圖8 FPGA內(nèi)部模塊

圖9 Chicoscope中觀測到的信號碼型

5 結(jié)語

為了驗證此系統(tǒng)的正確性與實用性,我們進行了大量的實驗。我們首先在Xlinx自帶調(diào)試軟件Chicoscope中觀測到的進入升余弦滾降濾波器之前的碼型和經(jīng)過升余弦滾降濾波器之后送往 AD9777的碼型,其后又在在頻譜儀上觀測的70MHz 上經(jīng)過BPSK調(diào)制的中頻信號的頻譜。比對觀察發(fā)現(xiàn)信號升余弦濾波前后的碼型正確,產(chǎn)生的中頻鐘型波形狀標(biāo)準(zhǔn)。經(jīng)過在數(shù)字多波束天線系統(tǒng)的接收機調(diào)試過程中的使用,證明了這是一種使用方便和發(fā)射信號靈活的試驗用擴頻信號發(fā)生器

[1] 王濤,彭茜,李威.基于中低速率短波擴頻通信系統(tǒng)設(shè)計[J].通信技術(shù),2009,42(08):39-41.

[2] 楊小牛,樓才義,徐建良.軟件無線電原理與應(yīng)用[M].北京:電子工業(yè)出版社,2001:208-209.

[3] Pickholtz R L,Schilling D L,Milstein L B.Theory of Spread Spectrum Communications[J].A Tutorial Special Issue of IEEE Trans.comm.,1982,30(05):45-46.