基于EDA仿真軟件Multisim在全加器設(shè)計中的應(yīng)用探析

摘 要:隨著電子技術(shù)的快速發(fā)展,電子設(shè)計自動化(EDA)已經(jīng)成為現(xiàn)代電子設(shè)計的重要手段。Multisim作為一種廣泛應(yīng)用于電子電路仿真與設(shè)計的軟件,為相關(guān)領(lǐng)域的研究者、工程師提供了便捷的工具和平臺。文章使用EDA仿真軟件Multisim通過軟件直接生成、利用軟件作為輔助通過門電路、譯碼器、數(shù)據(jù)選擇器設(shè)計實(shí)現(xiàn)全加器為例,探析Multisim在電子電路設(shè)計中的應(yīng)用方法和優(yōu)勢。結(jié)果表明Multisim仿真軟件設(shè)計電子電路在快速構(gòu)建、仿真和優(yōu)化全加器電路,以及提高設(shè)計效率和可靠性方面有明顯優(yōu)勢。

關(guān)鍵詞:EDA仿真軟件;Multisim;全加器;電路設(shè)計;仿真

中圖分類號:TP391.9 文獻(xiàn)標(biāo)識碼:A 文章編號:2096-4706(2024)17-0001-04

0 引 言

加法運(yùn)算是最基本的數(shù)字運(yùn)算,全加器是組合邏輯電路中的重要組成部分,是數(shù)字集成電路各模塊的核心部件[1]。加法器是構(gòu)成許多處理操作的基礎(chǔ),這些處理操作包括計數(shù)、乘法及濾波等[2]。使用EDA(電子設(shè)計自動化)軟件進(jìn)行全加器設(shè)計,能夠顯著提升設(shè)計效率和精確度。Multisim軟件是一款功能強(qiáng)大的電子設(shè)計軟件,它擁有豐富的元件庫和強(qiáng)大的仿真功能,為全加器設(shè)計帶來了諸多便利。本文通過一個具體的全加器設(shè)計實(shí)例,探析了Multisim在電子電路設(shè)計中的應(yīng)用方法和優(yōu)勢。

1 Multisim軟件介紹

Multisim 是美國NI公司推出的電路仿真軟件,該軟件分析功能強(qiáng)大、操作簡單、用戶界面友好、使用更加方便直觀[3],是一款電子設(shè)計自動化(EDA)軟件,具有豐富的電路元件庫、虛擬儀器庫和強(qiáng)大的仿真功能。用戶可以在軟件中搭建電路圖,對電路進(jìn)行仿真和測試,實(shí)時觀察電路性能。Multisim還支持與其他EDA軟件的接口,方便用戶進(jìn)行數(shù)據(jù)導(dǎo)入導(dǎo)出。

2 全加器的設(shè)計原理

全加器又稱全加電路,主要應(yīng)用于計算機(jī)系統(tǒng)和數(shù)字邏輯電路中。全加器是一種基本的算術(shù)電路,用于執(zhí)行兩個二進(jìn)制數(shù)A和B的加法操作,并根據(jù)接收到的低位進(jìn)位信號C進(jìn)行處理[4]。全加器不僅可以處理一位進(jìn)位,還可以處理多位進(jìn)位,具有較高的靈活性和實(shí)用性。

全加器的基本構(gòu)成包括兩部分:半加器和進(jìn)位輸出。半加器是全加器的核心部分,用于計算兩個二進(jìn)制數(shù)之間的和,同時判斷是否有進(jìn)位產(chǎn)生。進(jìn)位輸出則用于傳遞上一位的進(jìn)位信息,以實(shí)現(xiàn)多位全加器的級聯(lián)。在全加器的工作過程中,首先將兩個二進(jìn)制數(shù)按照位數(shù)對齊,然后通過半加器計算每位上的和。當(dāng)兩數(shù)之和為0時,半加器輸出0;當(dāng)兩數(shù)之和為1時,半加器輸出1;當(dāng)兩數(shù)之和為2時,半加器輸出1并產(chǎn)生進(jìn)位;當(dāng)兩數(shù)之和為3時,半加器輸出0并產(chǎn)生進(jìn)位,以此類推。全加器的另一個重要特點(diǎn)是能夠處理連續(xù)的進(jìn)位。當(dāng)某一位產(chǎn)生進(jìn)位時,進(jìn)位輸出會將其傳遞給下一位,從而實(shí)現(xiàn)多位的全加運(yùn)算。這種級聯(lián)方式使得全加器能夠處理更復(fù)雜的數(shù)字運(yùn)算,滿足不同位數(shù)二進(jìn)制數(shù)的加法需求。

全加器在數(shù)字電路中屬于組合邏輯電路,組合電路是指電路在任何時刻產(chǎn)生的穩(wěn)態(tài)輸出僅僅取決于該時刻輸入變量取值組合,而與過去的輸入值無關(guān)。組合電路的設(shè)計是利用多種門元件實(shí)現(xiàn)所需的功能。此電路的設(shè)計分為五步:1)根據(jù)全加器的基本原理,確定邏輯輸入變量和邏輯輸出變量,賦予邏輯值。2)根據(jù)邏輯關(guān)系,列出真值表。3)根據(jù)真值表,寫出邏輯函數(shù)的最小項表達(dá)式。4)化簡邏輯函數(shù),并根據(jù)可能提供的邏輯電路類型,求出所需要的表達(dá)式形式。5)畫出與所得表達(dá)式相對應(yīng)的邏輯電路圖。下面就根據(jù)此步驟設(shè)計全加器。

2.1 真值表及表達(dá)式

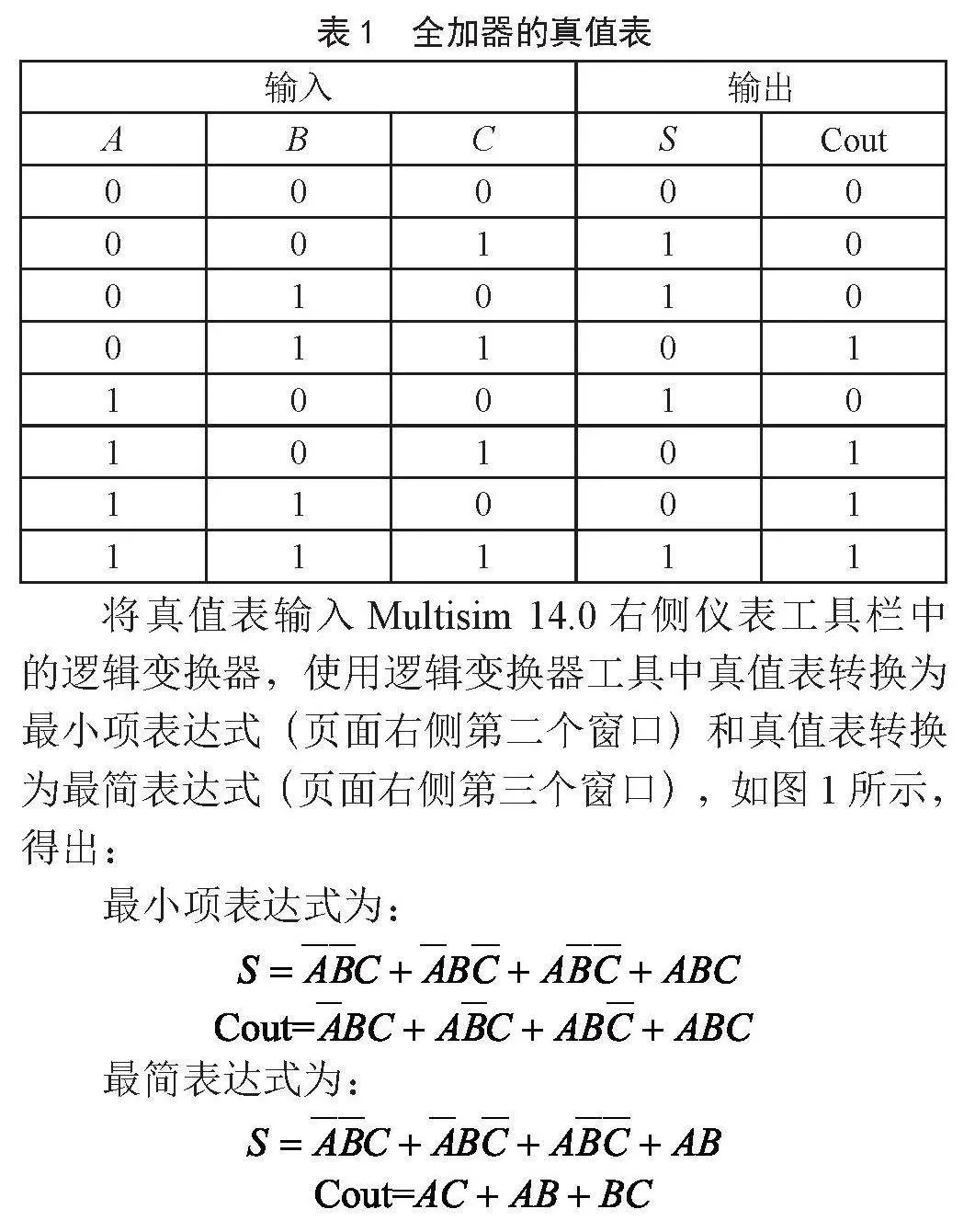

下面就兩個一位二進(jìn)制加法器為例進(jìn)行設(shè)計,首先確定變量及賦予邏輯值,輸入變量為加數(shù)A、被加數(shù)B、低位進(jìn)位C,輸出變量為和數(shù)S、向高位進(jìn)位Cout,列出真值表[5],如表1所示。

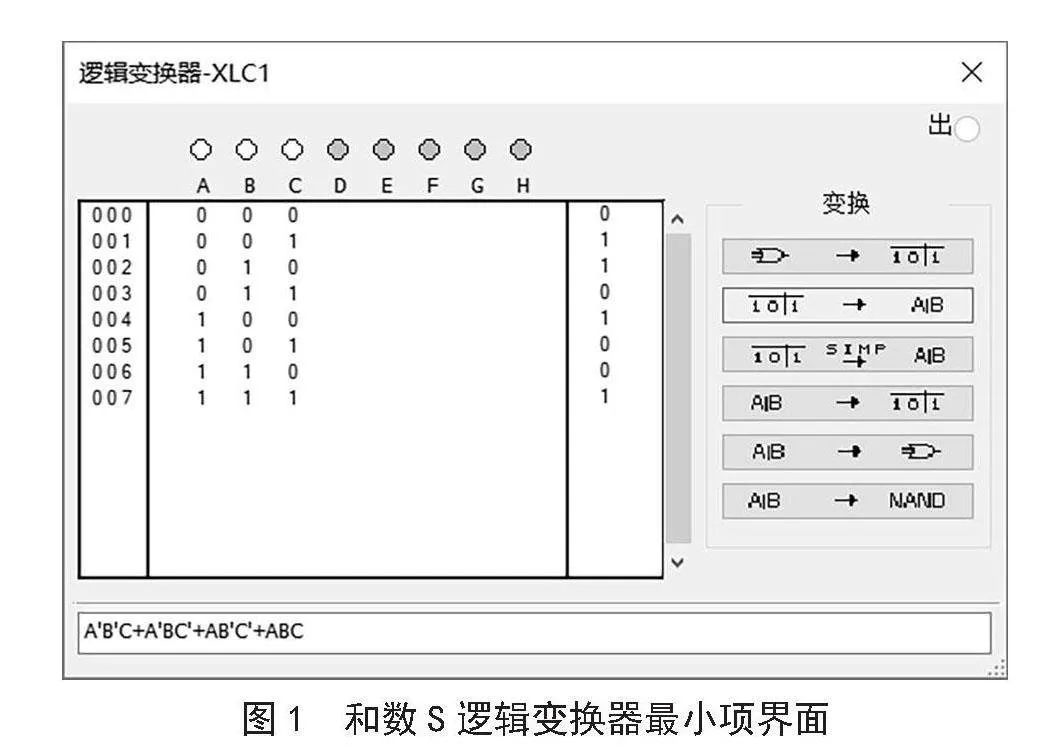

將真值表輸入Multisim 14.0右側(cè)儀表工具欄中的邏輯變換器,使用邏輯變換器工具中真值表轉(zhuǎn)換為最小項表達(dá)式(頁面右側(cè)第二個窗口)和真值表轉(zhuǎn)換為最簡表達(dá)式(頁面右側(cè)第三個窗口),如圖1所示,得出:

最小項表達(dá)式為:

最簡表達(dá)式為:

2.2 兩個一位二進(jìn)制全加器的四種實(shí)現(xiàn)方法

四種實(shí)現(xiàn)方法如下:

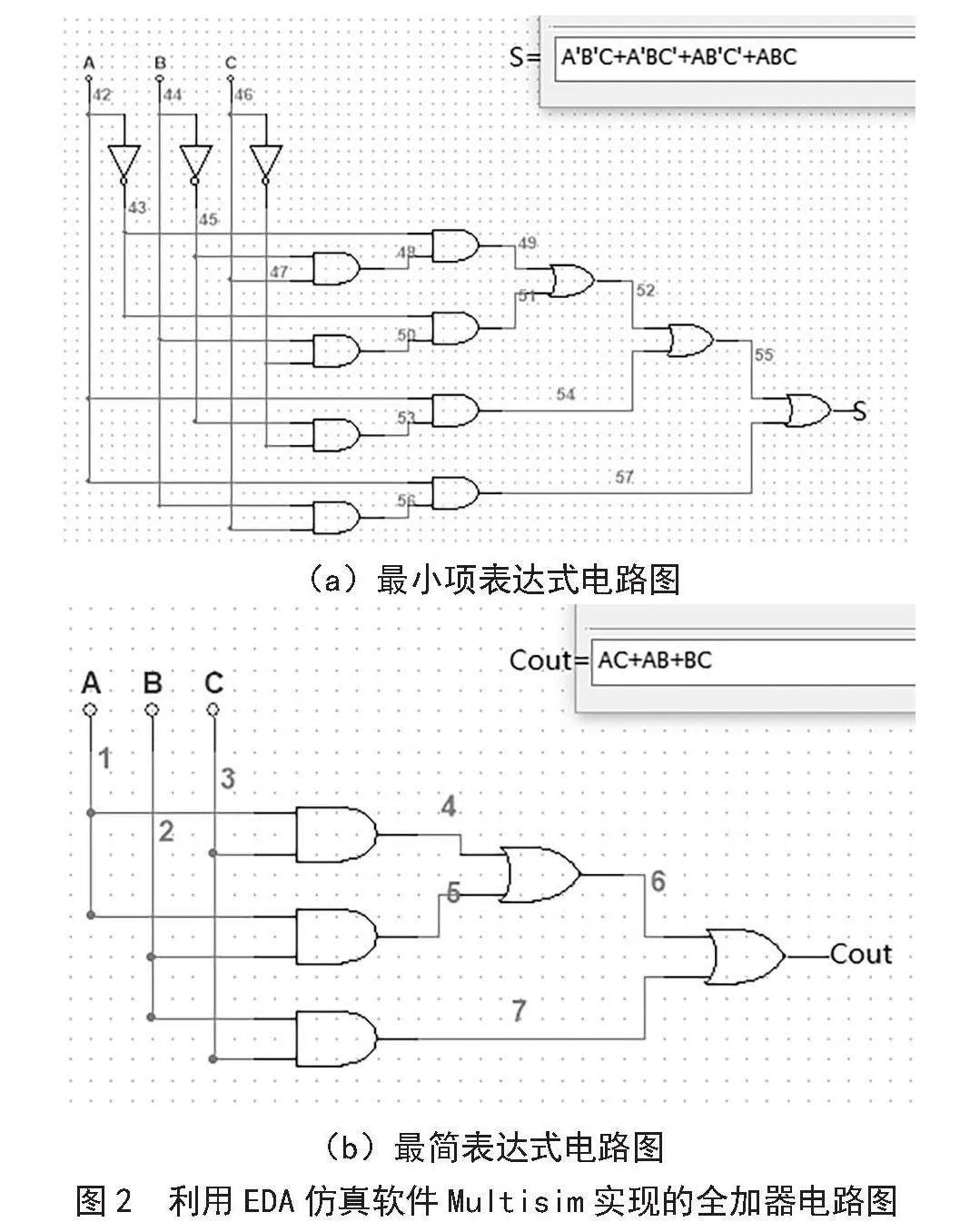

1)利用EDA直接生成。使用EDA仿真軟件Multisim 14.0的邏輯變換器窗口,將表達(dá)式轉(zhuǎn)換為電路圖(頁面右側(cè)第五個窗口)可得最小項表達(dá)式的電路圖、最簡表達(dá)式的電路圖,即可完成加法器的設(shè)計,以最簡表達(dá)式為例,電路圖如圖2所示。最簡表達(dá)式是與門的電路設(shè)計,在數(shù)字電子技術(shù)電路中常用的電路還有與非門,選擇表達(dá)式轉(zhuǎn)換為與非門電路圖按鈕(頁面右側(cè)第六個窗口)即可完成與非門電路圖設(shè)計,與非門的電路圖就不在此贅述。

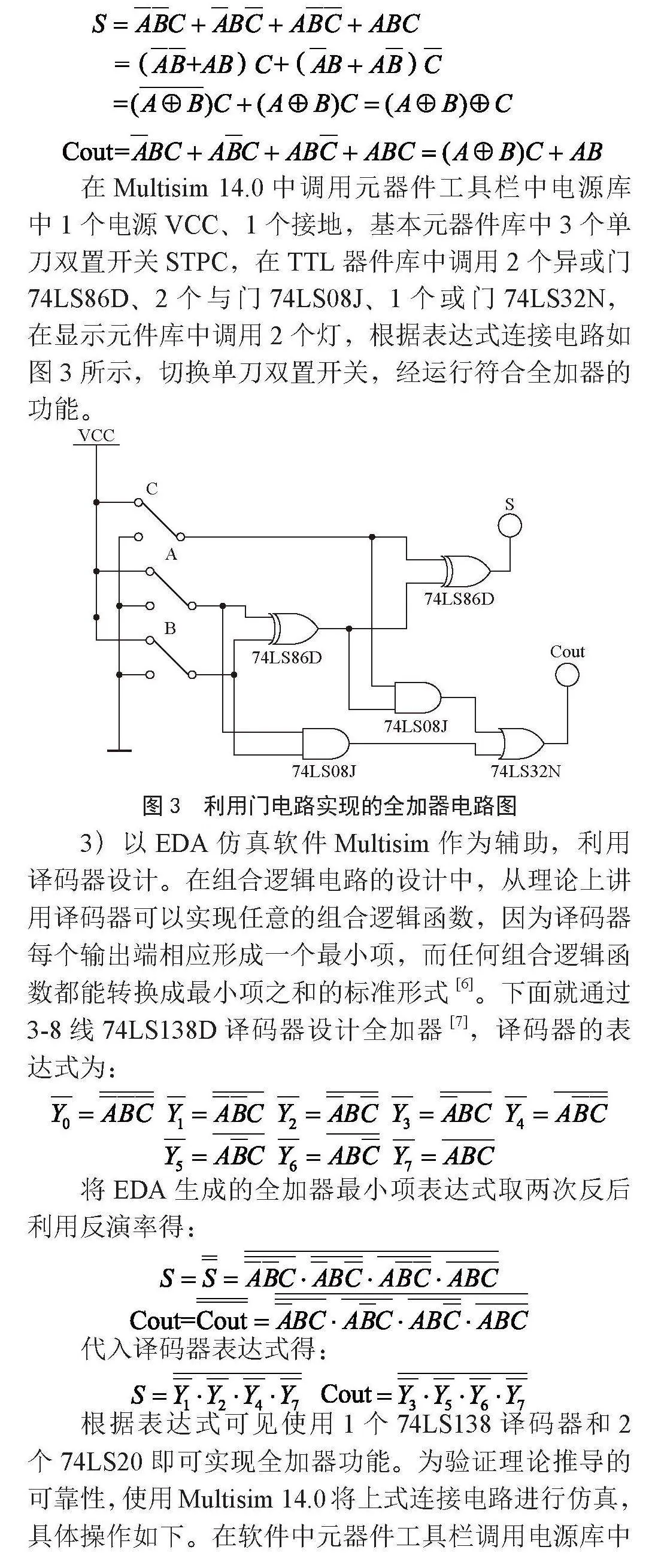

2)使用EDA仿真軟件Multisim作為輔助,利用門電路設(shè)計。在公式化簡邏輯表達(dá)式時,不同的化簡方式最簡表達(dá)式可能不唯一,下面將Multisim得出的最小項表達(dá)式進(jìn)行化簡可以設(shè)計出其他全加器電路,有:

在Multisim 14.0中調(diào)用元器件工具欄中電源庫中1個電源VCC、1個接地,基本元器件庫中3個單刀雙置開關(guān)STPC,在TTL器件庫中調(diào)用2個異或門74LS86D、2個與門74LS08J、1個或門74LS32N,在顯示元件庫中調(diào)用2個燈,根據(jù)表達(dá)式連接電路如圖3所示,切換單刀雙置開關(guān),經(jīng)運(yùn)行符合全加器的功能。

3)以EDA仿真軟件Multisim作為輔助,利用譯碼器設(shè)計。在組合邏輯電路的設(shè)計中,從理論上講用譯碼器可以實(shí)現(xiàn)任意的組合邏輯函數(shù),因為譯碼器每個輸出端相應(yīng)形成一個最小項,而任何組合邏輯函數(shù)都能轉(zhuǎn)換成最小項之和的標(biāo)準(zhǔn)形式[6]。下面就通過3-8線74LS138D譯碼器設(shè)計全加器[7],譯碼器的表達(dá)式為:

將EDA生成的全加器最小項表達(dá)式取兩次反后利用反演率得:

代入譯碼器表達(dá)式得:

根據(jù)表達(dá)式可見使用1個74LS138譯碼器和2個74LS20即可實(shí)現(xiàn)全加器功能。為驗證理論推導(dǎo)的可靠性,使用Multisim 14.0將上式連接電路進(jìn)行仿真,具體操作如下。在軟件中元器件工具欄調(diào)用電源庫中1個電源VCC、2個接地,基本元器件庫中3個單刀雙置開關(guān)STPC,TTL器件庫中1個74LS138C譯碼器、2個74LS20C與非門,顯示元件庫中2盞燈,連接電路如圖4所示,切換單刀雙置開關(guān),經(jīng)運(yùn)行驗證能實(shí)現(xiàn)全加器的功能。

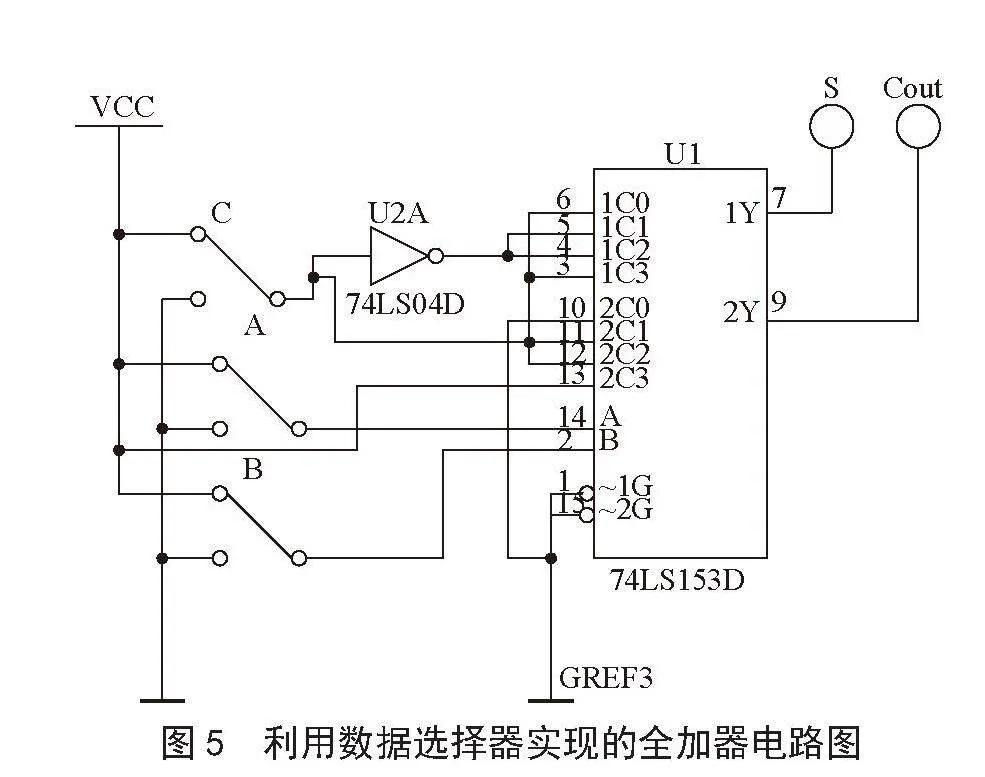

4)使用EDA仿真軟件Multisim作為輔助,利用數(shù)據(jù)選擇器設(shè)計。數(shù)據(jù)選擇器又叫“多路開關(guān)”。數(shù)據(jù)選擇器在地址碼(或叫選擇控制)電位的控制下,從幾個數(shù)據(jù)輸入中選擇一個并將其送到一個公共的輸出端。根據(jù)數(shù)據(jù)選擇器的輸出特點(diǎn),數(shù)據(jù)選擇器具有標(biāo)準(zhǔn)與或表達(dá)式的形式,提供了地址變量的全部最小項,通過對照比較法可以實(shí)現(xiàn)多變量的任意組合邏輯電路。下面用74LS153雙輸入多路數(shù)據(jù)選擇器,設(shè)計實(shí)現(xiàn)全加器。74LS153輸入信號有4個分別是C0、C1、C2、C3,選擇控制信號2個分別是A1、A0,輸出信號1個Y,此外還有1個輸出控制信號ST。輸出Y的邏輯表達(dá)式為:

當(dāng)ST=0時,有 A1A2=00,Y=C0

A1A2=01,Y=C1

A1A2=10,Y=C2

A1A2=11,Y=C3

當(dāng)ST=1時,Y恒為0。

為實(shí)現(xiàn)全加器功能,將全加器的表達(dá)式與數(shù)據(jù)選擇器表達(dá)式相等,經(jīng)使用對照比較法需令全加器的A=A1,B=A0,S=Y1,Cout=Y2,可得:

根據(jù)如上理論推導(dǎo),使用1個74LS153數(shù)據(jù)選擇器和1個74LS04非門可實(shí)現(xiàn)全加器功能。為驗證理論推導(dǎo)的可靠性,使用Multisim 14.0連接電路進(jìn)行仿真,具體操作如下。調(diào)用元器件工具欄中電源庫中1個電源VCC、2個接地,基本元器件庫中3個單刀雙置開關(guān)STPC,在TTL器件庫中1個74LS153D數(shù)據(jù)選擇器、1個74LS04D,顯示元件庫中2盞燈,連接電路如圖5所示,切換單刀雙置開關(guān),經(jīng)運(yùn)行驗證能實(shí)現(xiàn)全加器的功能。

以上介紹了結(jié)合EDA仿真軟件Multisim設(shè)計全加器的四種方法,方法一是使用仿真軟件直接生成,其余方法均使用EDA仿真軟件作為輔助。后三種方法通過仿真軟件先輸入真值表,再將真值表轉(zhuǎn)化為最小項表達(dá)式分別通過手動化簡、74LS138芯片的最小項輸出器的特性、74LS153多位選擇器輸出特點(diǎn)對照比較設(shè)計得出理論全加器電路圖,最后使用軟件進(jìn)行仿真驗證。

對比方法一EDA直接生成和方法二手動化簡設(shè)計電路發(fā)現(xiàn),在使用EAD生成的最簡表達(dá)式電路圖可以自動優(yōu)化電路布局,使得全加器的結(jié)構(gòu)更加緊湊,減少面積占用,提高芯片的集成度,同時可以減少研發(fā)人員的工作量,降低設(shè)計成本,設(shè)計可以快速完成提高設(shè)計效率。但鑒于實(shí)現(xiàn)邏輯功能的表達(dá)式并不唯一、電路設(shè)計不唯一,在使用EDA仿真軟件設(shè)計電路時,組合邏輯電路可靈活地根據(jù)實(shí)際中現(xiàn)有的資源情況選擇設(shè)計方法。

本文介紹了四種生成全加器的方法,每種方法的第一步都是使用仿真軟件直接生成最小項表達(dá)式,跳過根據(jù)真值表寫出邏輯函數(shù)的最小項表達(dá)式的步驟,操作方便不宜出錯,尤其針對新手使用者在基本最小項表達(dá)式都不熟悉的情況下保證了正確率、簡單直觀易上手[8]。

方法二在設(shè)計電路中使用常用的異或門電路來實(shí)現(xiàn),通過公式化簡法有意識地將最小項表達(dá)式化簡為異或門電路。方法三利用譯碼器可以實(shí)現(xiàn)任意的組合邏輯函數(shù)可以作為一個最小項輸出器的特點(diǎn)設(shè)計實(shí)現(xiàn)。方法四利用數(shù)據(jù)選擇器具有標(biāo)準(zhǔn)與或表達(dá)式的形式提供了地址變量的全部最小項的特點(diǎn)設(shè)計實(shí)現(xiàn)。可見我們在使用EDA仿真軟件設(shè)計電路時具有其局限性,豐富的設(shè)計經(jīng)驗加軟件的熟練使用是保證設(shè)計實(shí)現(xiàn)的關(guān)鍵。

后三種方法通過EDA仿真軟件進(jìn)行電路布局和測試,這對于電路理論基礎(chǔ)相對薄弱而邏輯思維和編程能力較強(qiáng)的設(shè)計者尤為適合。EDA技術(shù)可以使設(shè)計者突破硬件源方面的限制,充分發(fā)揮想象力和創(chuàng)造性,設(shè)計出別具特色的作品[9]。使用EDA仿真軟件進(jìn)行布局和連線,用戶界面簡潔、操作簡單,可以更好地為設(shè)計者提供便利,比起實(shí)物連接更可靠,減少動手操作的錯誤,提高了整體設(shè)計效率。連線完成點(diǎn)擊運(yùn)行即可開始仿真,實(shí)驗不受時間、地點(diǎn)、設(shè)備的限制,可以有效降低實(shí)驗故障率,避免因?qū)嶒瀮x器數(shù)量種類限制無法操作或因為連線錯誤導(dǎo)致儀器損壞,可有效減小設(shè)計成本[10]。

3 結(jié) 論

Multisim作為一款功能強(qiáng)大的EDA仿真軟件,在全加器設(shè)計中的應(yīng)用具有顯著優(yōu)勢。通過Multisim電子設(shè)計工程師可以快速構(gòu)建、仿真和優(yōu)化全加器電路,提高設(shè)計效率和可靠性。本文以實(shí)際案例為依據(jù),詳細(xì)介紹了Multisim在全加器設(shè)計中的具體應(yīng)用方法和技巧,希望能為相關(guān)領(lǐng)域的研究者和工程師提供參考。

參考文獻(xiàn):

[1] 李林,張躍軍,張會紅.基于線計算的全加器設(shè)計 [J].寧波大學(xué)學(xué)報:理工版,2022,35(1):40-47.

[2] 楊曉雷.Multisim11在《電工技術(shù)基礎(chǔ)與技能》教學(xué)中的應(yīng)用研究 [D].上海:上海師范大學(xué),2013.

[3] 趙軍紅.集成式高性能低功耗Quasi-Pseudo-NMOS/DT-CPL-TG全加器電路設(shè)計 [D].西安:西安電子科技大學(xué),2005.

[4] 周文宸.基于55nm工藝的超前進(jìn)位加法器設(shè)計 [D].濟(jì)南:山東大學(xué),2023.

[5] 李宏偉.精度可配置低延時加法器設(shè)計 [D].南京:東南大學(xué),2022.

[6] 楊方.基于譯碼器和數(shù)據(jù)選擇器進(jìn)行組合邏輯電路設(shè)計 [J].喀什師范學(xué)院學(xué)報,2012,33(3):51-52.

[7] 高美蓉.基于門電路的消除譯碼器競爭冒險方法 [J].寶雞文理學(xué)院學(xué)報:自然科學(xué)版,2022,42(3):77-80.

[8] 尚濤.組合邏輯電路自動合成的方法研究 [D].武漢:武漢科技大學(xué),2009.

[9] 呂念芝.基于Multisim與EDA技術(shù)的數(shù)字邏輯實(shí)驗教學(xué)改革研究 [J].工業(yè)和信息化教育,2022(7):82-86.

[10] 萬嘉譽(yù).五款虛擬仿真軟件在高中電學(xué)實(shí)驗中應(yīng)用的對比研究 [D].昆明:云南師范大學(xué),2023.

DOI:10.19850/j.cnki.2096-4706.2024.17.001

作者簡介:向春艷(1990.01—),女,漢族,新疆沙灣人,助教,碩士,研究方向:物理學(xué)、教育技術(shù)學(xué);陳雪嬌(1995.05—),女,漢族,新疆昌吉人,助教,碩士,研究方向:電氣自動化;薛喜紅(1994.12—),女,漢族,陜西榆林人,助教,碩士,研究方向:電氣自動化;張海龍(1990.08—),男,漢族,甘肅定西人,助教,碩士,研究方向:電氣自動化;李子豪(2004.10—),男,漢族,新疆昌吉人,專科在讀,研究方向:機(jī)電一體化技術(shù)。

收稿日期:2024-02-20

Application Analysis of Simulation Software Multisim in Full Adder Design

Based on EDA

XIANG Chunyan, CHEN Xuejiao, XUE Xihong, ZHANG Hailong, LI Zihao

(Xinjiang Vocational University, Urumqi 830013, China)

Abstract: With the rapid development of electronic technology, Electronic Design Automation (EDA) has become an important means of modern electronic design. As a software widely used in electronic circuit simulation and design, Multisim provides convenient tools and platforms for researchers and engineers in related fields. This paper uses EDA simulation software Multisim as an example, which directly generates through software and uses software as auxiliary to design and realize the full adder through the door circuit, decoder, and data selector, so as to analyze the application methods and advantages of Multisim in electronic circuit design. Results show that the design of Multisim simulation software in electronic circuits has obvious advantages in rapid construction, simulation, optimization of full adder circuits, and improving design efficiency and reliability.

Keywords: EDA simulation software; Multisim; full adder; circuit design; simulation