異構雙核處理器失速告警系統設計

魏璐達,宣曉剛,楊 飛,張美仙,賈少龍

(航空工業太原航空儀表有限公司,山西 太原 030006)

0 引言

飛機失速是飛機迎角(angle of attack,AOA)超過臨界AOA,機翼升力面出現嚴重的氣流分離,導致飛機阻力急劇增大、升力驟然下降的現象。飛機失速會導致飛機失控,引發飛行事故。為保證飛行安全,民航局適航司規定,要在民用飛機上加裝失速告警系統(stall warning system,SWS)[1-2]。飛行員通過SWS獲得飛機運行時的失速告警、保護信息,以及相應的控制指令,從而執行相應的操作,以確保飛機不進入失速危險狀態。

目前,歐美、俄羅斯等國家和地區的軍用和民用飛機加裝的SWS大多是基于單核處理器,或者采用多處理器同步時鐘的方法構建余度告警計算機,并采用雙余度失速告警計算機(stall warning computer,SWC)的方法來滿足適航法規對安全性的要求。隨著技術的發展,失速判斷已經從根據飛機AOA和空速等參數來判斷飛機是否進入失速狀態,發展到利用AOA、側滑角、法向過載、空速、突風影響到地效應影響等多種飛行參數進行綜合分析和處理。采用單核處理器的雙余度SWS,在同一處理器上對解算數據進行數據一致性檢查將產生可信度的問題,使輸出指令的誤判率增加。采用多處理器同步時鐘的方法明顯增加了計算機系統的復雜度和成本,且設備的基本可靠性平均無故障工作時間(mean time between failure,MTBF)顯著降低,難以滿足適航安全性要求。

針對以上問題,本文提出了一種基于異構雙核處理器的SWS設計方案。該方案在SWS功能的基礎上,采用異構雙核處理器對解算數據進行監測比對,僅在雙核解算的數據一致時才會輸出失速告警指令等信息。這樣的設計提高了輸出指令的準確性,可防止因單核處理器無法在同一處理器上進行數據比對而產生的誤操作。這提高了SWS的可靠性和安全性,同時降低了設備的復雜度和成本。

1 SWS功能及架構

1.1 SWS功能

SWS通過在飛機接近失速時向飛行員發送告警和控制信息,確保飛行員及時操縱飛機,使飛機迅速恢復到正常狀態來保證飛行安全[2]。SWS一般由AOA傳感器、SWC、告警裝置等組成[1]。

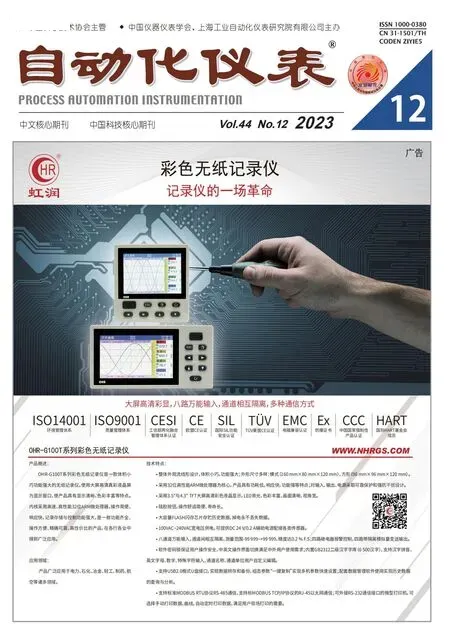

典型的SWS架構如圖1所示。

圖1 典型的SWS架構

為了避免飛機側滑時AOA傳感器進入氣流遮蔽區,造成AOA傳感器測量AOA失真,AOA傳感器一般安裝于機頭兩側的飛機蒙皮表面。AOA傳感器采集飛機的AOA信號,在SWC中將修正后的AOA信號與失速告警AOA預設值進行比較。當AOA大于失速告警AOA時,SWC接通告警裝置,即振桿器(stick shaker actuator,SSA)。SSA會令駕駛桿抖動,并伴有燈光告警和語音告警來提醒飛行員采取措施,以免飛機進入失速狀態。當AOA大于發動機點火預設值時,SWC向發動機控制系統發出點火指令[1,3]。

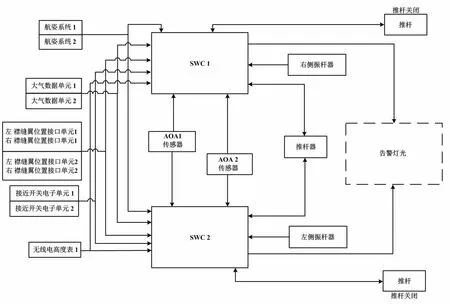

1.2 SWS架構

為滿足SWS的功能,本文設計的SWS由2只AOA傳感器、2臺SWC和2只SSA組成。其中,AOA傳感器用于采集飛機AOA信號并發送給SWC。SWC作為系統核心設備,對采集的AOA信號數據作修正處理,并將機上其他設備(如航電系統、結冰探測系統等)發送的數據進行邏輯運算和分析,以判斷飛機是否接近失速。在接近失速時,SWC對外發出告警和保護指令。SSA作為告警裝置,根據失速告警指令進行抖振以提醒駕駛員進行操作,避免飛機進入失速狀態。本文設計的SWS架構如圖2所示。

2 SWC功能與設計

2.1 SWC功能

SWS中的核心控制部件為SWC。SWC通過AOA傳感器采集飛機AOA信息,并將采集的信息進行修正從而得到真實AOA。SWC除了接收飛機AOA信息,還需接收飛機上其他系統發送的信息,如馬赫數、高度、姿態、襟縫翼構型、結冰等。SWC對接收到的數據進行解算,并根據解算結果判斷飛機真實AOA是否接近氣動失速。當解算結果得出飛機處于接近氣動失速狀態時,SWC會發出失速告警、自動點火和失速保護指令,向飛行員提供告警指示,從而保護飛機不進入失速危險狀態。

本文設計的SWC具有以下功能。

①SWC向AOA傳感器提供激勵信號,并接收AOA傳感器輸出的2路AOA信號。采集到的2路AOA信號作為原始數據用于計算飛機局部AOA。此外,AOA傳感器具有加熱功能。SWC會監控AOA傳感器的加熱狀態。

②SWC通過數據總線接收外部輸入數據;根據接收的數據信息解算AOA、臨界AOA和失速速度。

③當真實AOA接近臨界AOA或空速接近失速速度時,SWC輸出告警驅動信號給同側SSA和燈光告警、語音告警系統,以提醒飛行員采取措施;同時,向機組告警系統輸出告警狀態。

④當真實AOA繼續增大到失速保護控制AOA,SWC發出保護指令給SSA,同時發出保護狀態給機組告警系統。當真實AOA小于失速保護控制AOA一定數值時,SWC停止發出保護指令。

⑤當真實AOA繼續增大至點火AOA,SWC持續發出點火指令給左、右發動機;同時發出點火狀態給機組告警系統。若真實AOA小于點火AOA一定數值時,SWC停止發出點火指令。

此外,本文設計的SWC還需遵循適航規章、標準和指南。針對運輸類飛機,與失速相關的專用條款有《運輸類飛機適航標準》(CCAR25-R4)中第25.207條款和《Safety Assessment of Transport Airplanes in Commercial Service》(SAE ARP5150A-2019)附錄A表A2等。基于以上描述,提高SWC設計的安全性、降低失速告警指令的誤導/無告警的錯誤率尤為重要。為提高設計的可靠性和安全性,SWC會對解算結果進行監控并對數據一致性進行判斷,將AOA信號等關鍵信息和輸出的失速告警指令等信息數據作一致性比較,以輸出告警指令、保護指令和點火指令等信息。因此,本文設計的關鍵是處理器的選擇。本文設計采用2個單核處理器或1個雙核處理器,以滿足對運算結果監測的需求。

2.2 SWC的設計

2.2.1 處理器選擇

傳統SWS的設計采用2個單核中央處理器(entral processing unit,CPU)構建雙余度SWC,以滿足系統對于安全性的要求。假設的雙CPU機載計算機設備如圖3所示。

上述設計對系統的復雜度和成本要求較高,且2個單核CPU的使用給數據一致性的比對帶來了困難。此外,在CPU的選擇上,單核處理器有其局限性。

這些局限性在于:單核CPU主頻的提升已達到工藝加工的極限;在單核CPU中,單一線程不能提高系統的并行性,處理速度相較于雙核CPU慢很多;CPU主頻的提升帶來了功耗的增加,使散熱量加大,且目前沒有保證CPU正常穩定工作較好匹配的散熱系統來更好地處理散熱;對于大型功能需求的處理,單核CPU表現出了缺陷和不足[4]。

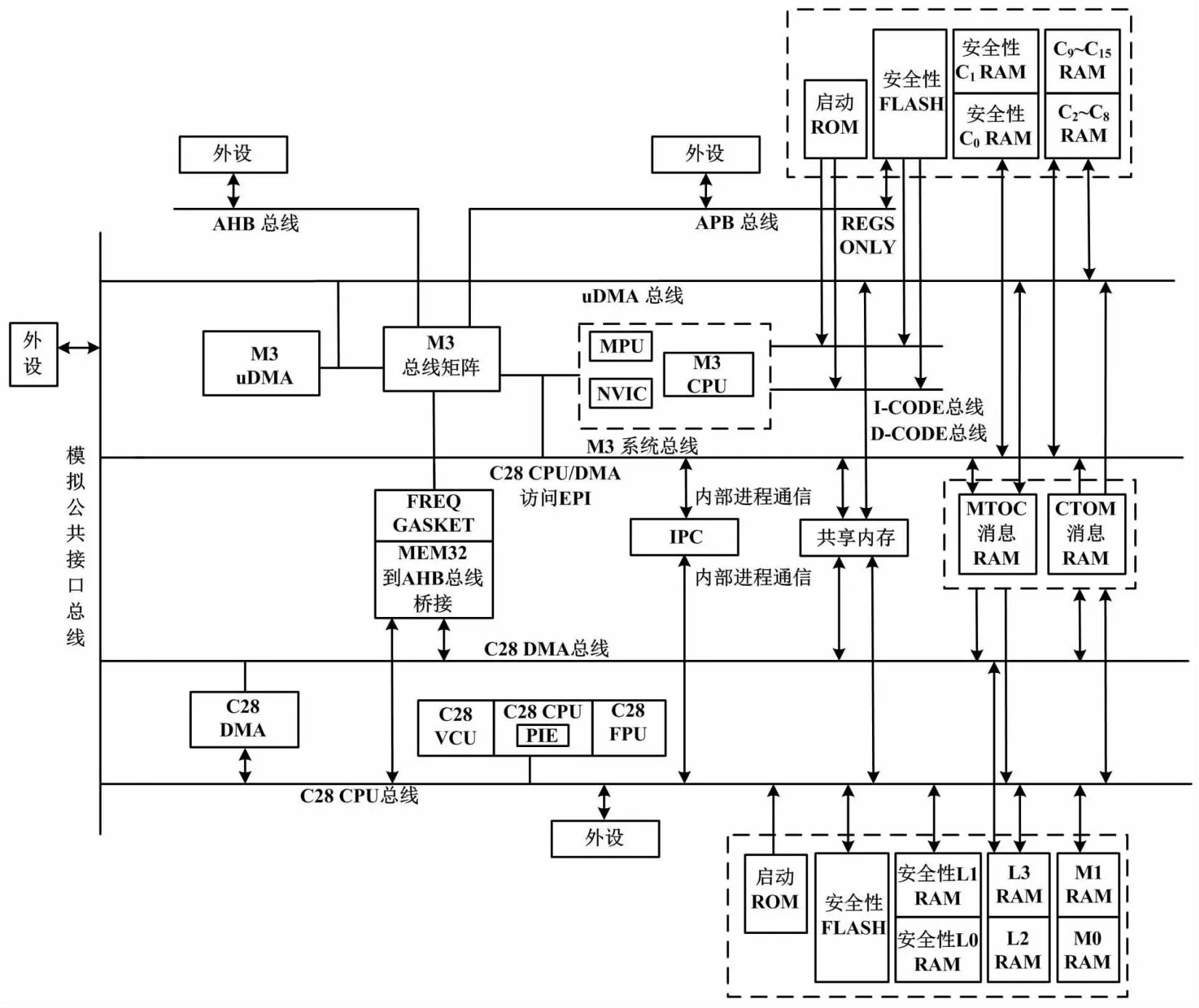

異構雙核CPU將2個不同的CPU內核集成在1個CPU芯片中。典型的異構雙核CPU架構如圖4所示。

圖4 典型的異構雙核CPU架構

異構雙核CPU具有不同結構的CPU內核。2個內核有獨自的內存和外設,且擁有各自的系統時鐘。雙核間通常使用CPU通信接口和共享內存進行數據交互。比較常見的異構雙核CPU架構有進階精簡指令集計算機機器(advanced reduced instruction set computer machine,ARM)+數字信息處理器(digital signal processing,DSP)相結合的非對稱雙核架構[5-6]。異構雙核CPU可以大幅提升計算能力,改善性能。將所要執行的任務劃分到2個內核中,可在較短的時間內完成任務。這樣就能在特定時間內處理更多的任務[4]。同時,異構雙核CPU所帶來的余度設計提高了系統的可靠性,適用于復雜度高的可靠性系統[7]。

將上述單核CPU局限性和雙核CPU優勢進行比較,結合SWC對解算結果需要監測和比較的需求,本文選擇采用異構雙核CPU。其能更高效地實現SWC的功能。相較于采用2片單核CPU,使用1片雙核CPU的成本更低。

2.2.2 雙核CPU核間通信機制選擇

CPU核間通信(inter-processor communication,IPC)用于在2個CPU子系統間進行通信。其原理是2個CPU核之間通過全局共享內存、消息內存、IPC標志和中斷,對各內核工作狀態和信息進行傳遞[8]。

常見的雙核CPU核間通信機制有信號量、共享內存和消息隊列。

信號量是用于解決進程間同步和互斥問題的1種通信機制[4]。而基于共享內存的通信機制則為數據傳遞提供了1種更為有效的方式,是常用的核間通信機制。

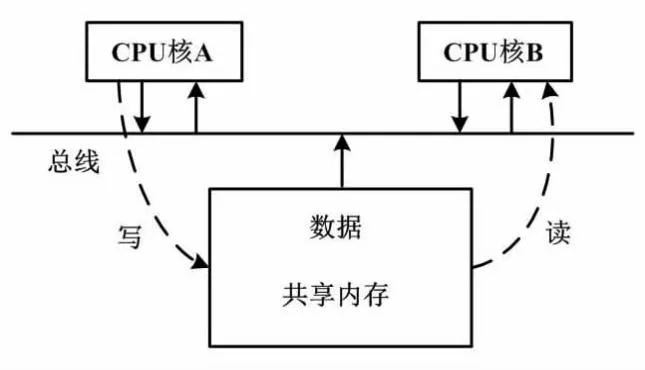

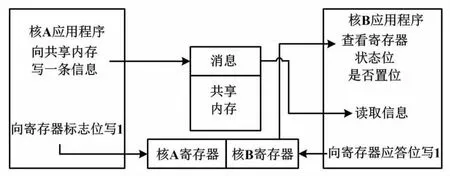

共享內存通信機制的原理是CPU核間共享1塊內存。2個內核都可以申請使用這塊共享內存進行讀寫操作。共享內存是數據傳遞媒介。共享內存通信機制如圖5所示。

圖5 共享內存通信機制

圖5中:CPU核A向共享內存寫入數據;CPU核B從共享內存中讀取這些數據。這樣便可完成核A到核B的核間通信[9]。

核間通信機制為消息隊列。它的實質是消息列表。用戶可以從消息隊列中添加和讀取消息,實現2個進程間的數據交換,且發送和接收進程均獨立進行。核間通信機制的不足是消息隊列中所含數據塊總長度有上限[4,10]。

3種核間通信機制中,共享內存是較高效的核間通信方式。共享內存無需對數據進行拷貝,而是直接讀寫。這在很大程度上提高了通信效率。對比3種雙核CPU核間通信機制可知:共享內存方式更為高效、便捷,能提高雙核間數據傳輸速率。因此,本文采用共享內存方式實現SWC中異構雙核間的數據交互。

2.2.3 異構雙核設計任務分配與實現

SWC中,異構雙核CPU執行的所有任務為數據采集和接收。其包含AOA信號采集、ARINC429總線數據接收、離散量信號接收等;接收的數據解析、整理和解算;將接收的原始數據傳輸給CPU的另一個核;監測數據解算結果的一致性;數據和指令的輸出。

通過對CPU所執行的任務進行合理分配,可以在保證滿足雙核設計需求的前提下最大程度提升雙核間通信速率。在任務的分配上,令CPU核A為主CPU、CPU核B為數據監測CPU。雙核之間采用共享內存方式進行核間通信,以實現數據傳輸和監測。核A負責數據的采集和接收;對接收到的數據進行解析、整理和解算;將接收的原始數據寫入共享內存中供核B讀取,并相應地從共享內存中讀取核B解算后的數據。在核A中對核A和核B解算的數據進行一致性判斷,如果所比較的解算結果一致,則對外輸出解算后的數據和指令。核B負責從共享內存讀取核A寫入的原始數據并對數據解算,將解算后的數據寫入共享內存供核A讀取。將任務進行上述分配,并通過使用共享內存進行數據讀寫操作,從而盡可能實現對程序執行過程的優化。異構雙核設計任務分配如圖6所示。

圖6 異構雙核設計任務分配

另外,設計時還需注意保持核A和核B的數據來自同一周期。對于輸出的失速保護指令,只有2個內核間解算結果一致且有效時,才可對外輸出。整個共享內存機制數據傳輸過程如圖7所示。

圖7 共享內存機制數據傳輸過程

3 其他設計

SWC對航電系統、航資系統等采用ARINC429總線數據的接收方式,對其他系統(如輪載系統)采用離散量總線的接收方式,并根據SWC數據接收方式的不同選擇合適的芯片進行外圍電路和程序的設計。此外,SWC需要對AOA傳感器輸出激勵信號,在選擇好的旋變傳感器芯片基礎上設計外圍電路,通過CPU控制來輸出傳感器所需的激勵信號。

4 結論

本文基于異構雙核CPU,設計了具有共享內存通信機制的SWC。SWC作為整個系統的核心設備,在設計時充分考慮安全性能等方面,實現了在同一CPU上對解算結果監控和數據一致性判斷的功能。經測試,共享內存通信機制使得數據間交互更加方便、快捷。結合系統設計要求,SWS宜采用共享內存通信機制進行雙核間數據監測和數據傳輸。在其他系統對于余度設計有要求時,可采用異構雙核CPU進行雙余度設計,以滿足系統可靠性、安全性、低成本的設計需求。