低功耗精密電源監控電路設計與開發

李虎群 張哲 吳飛龍 徐墨

關鍵詞:電源監控;上電復位;欠壓保護

中圖分類號:TN86;TP277 文獻標識碼:A

0 引言

隨著集成度的提高,單個芯片上包含了越來越多的復雜功能模塊。其中一些模塊必須在上電或者從節電模式恢復時,處于一定的已知初始狀態,從而保證能夠正確地執行操作。因此需要采用上電復位和欠壓復位信號對諸如觸發器、鎖存器和寄存器等存儲器件進行復位或置位[1]。作為數字電路核心的時鐘發生器,可能輸出不確定的時鐘,導致系統處于未知狀態。因此,需要上電復位電路和欠壓保護對電源和系統時鐘同時進行監控,保證在模擬電路能正常工作的電源電壓下,輸出波形、占空比和頻率正確穩定的時鐘[2]。

1 電源監控電路的原理

1.1 電源監控電路的電壓檢測構架

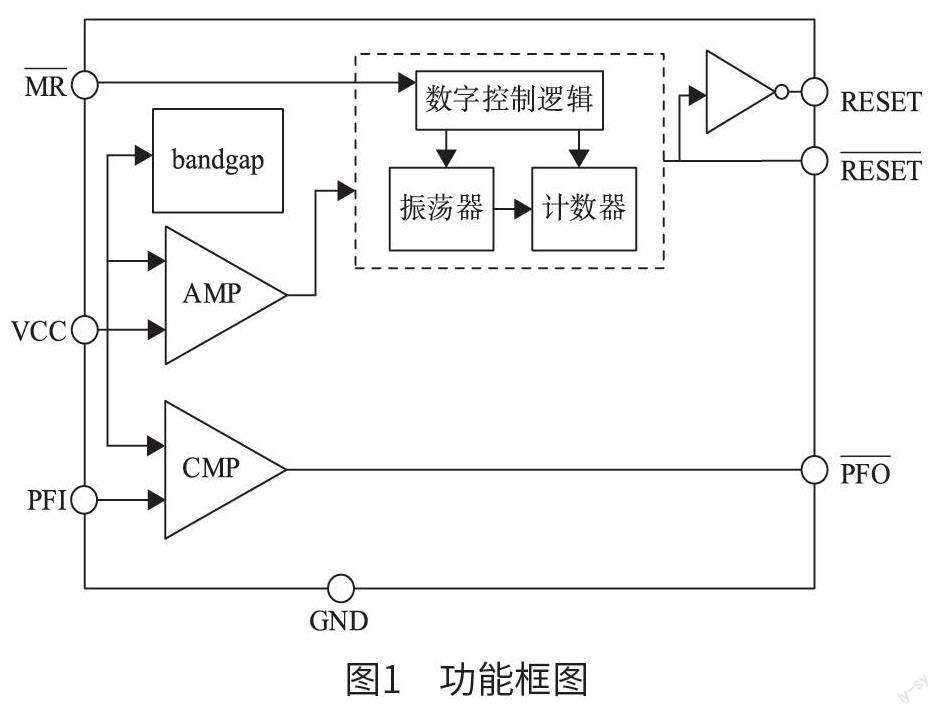

本文設計了一種高精度的電源電壓監控電路, 內部包括低溫票帶隙基準(bandgap) 電路、電源比較電路(AMP)、可調電壓失效比較器(CMP)、振蕩器、計數器和數字控制邏輯5 個模塊。低溫票帶隙基準電路為芯片提供一個低溫漂的基準電壓,電源放大器、電源錯誤指示輸入(PFI)比較器利用這個基準電壓來判斷電源電壓是否處于正常工作范圍內。電源比較電路和可調電壓失效比較器設計為低失調的,確保能精確判斷電源電壓是否正常;振蕩器用于產生基準時鐘信號,提供給計數器計數以產生固定寬度的復位脈沖。

1.2 電源監控電路設計原理

本文設計的監控電路,用于監測3 ~ 5 V 微處理器系統中的3 V 電源,同時具有復位和電源錯誤指示等功能。

復位電路用于保持微處理器為已知狀態,防止在系統掉電時出現代碼執行錯誤。在系統上電過程中,一旦電路供電電壓(VCC)達到1.2 V,復位信號(RESET)將保證為低電平。隨著VCC 繼續上升,一旦VCC 大于RESET 閾值,內部計數器計數200 ms 后,RESET 變為高電平。RESET 有低電平有效和高電平有效兩個輸出。

1.3 電源監控電路設計

1.3.1 低溫票帶隙基準設計與實現

低溫票帶隙基準通過將一個正溫度系數的電壓和一個負溫度系數的電壓以合適的比例進行疊加,得到一個接近零溫度系數的電壓[1]。負溫度系數一般由一個正向偏置PN 結決定,在維持通過結的電流不變的情況下,結兩端的電壓有負溫度系數,大約為-2 mV/℃。而正溫度系數由不同電流密度的兩個正向偏置PN 結決定,其結電壓的差值可實現具有正溫度系數的電壓[3]。

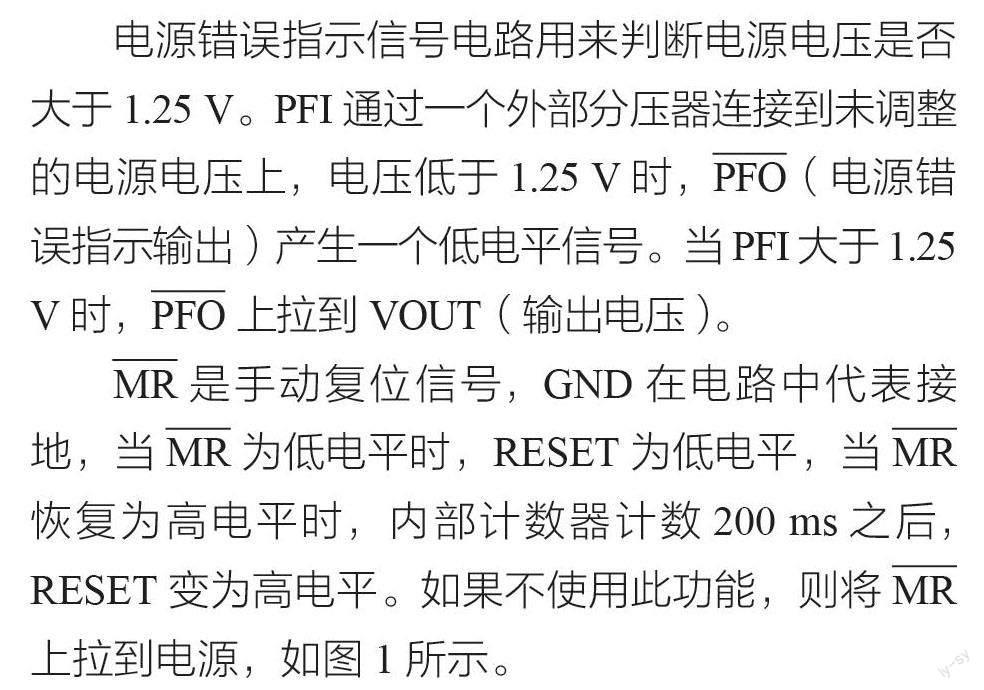

如圖2 所示,由于運放的反饋作用,A 點和B點的電壓相等,同時R1和R2的另一端接在一起,所以R1和R2兩端的電壓相等;由于它們的阻值成比例,且運放不吸收電流,所以流過Q0 和Q1的電流可根據R1 和R2 的阻值比例進行計算[4]。

作用在R0兩端的電壓是具有不同電流密度的雙極型晶體管(BJT)的Vbe 電壓的差值,它具有正溫度系數。決定Q0和Q1不同電流密度的因素如下:一是R1和R2的電阻比;二是Q1/Q0的并聯個數比m。R0兩端電壓的計算方法是:

△Vbe=VT×ln(mn)。 ( 1)

其中,n 是R1/R2的電流比。VT 是熱電壓(thermalvoltage),在室溫下大概為28 mV。在面積開銷合理的情況下,應讓△Vbe 盡量大一些,它可以減少低溫票帶隙基準電路對于運放輸入失調電壓的敏感度。流過R0和R2的電流是一樣的,所以只需要調節R2和R0的電阻比,就能將正溫度系數電壓放大一倍,同時這個正溫度系數又是疊加在Q1具有負溫度系數的Vbe 上,所以得出結論:只要合理地選擇了BJT 的電流密度以及電阻阻值的比例,就可以在Vref_out 處得到一個幾乎不隨溫度變化的帶隙電壓[5]。

1.3.2 低功耗振蕩電路及定時器的設計與實現

芯片復位信號寬度需要用定時器確定,而定時器的時鐘需要振蕩器來產生。當芯片檢測到電壓過低時,需恢復到正常振蕩器才開始工作,因此振蕩器需要快速響應、快速起振并達到所需的頻率。快速起振并實現低功耗的振蕩電路和定時器是本設計中的一個重點要求[6]。

2 電源監控電路的仿真

2.1 電源監控電路前仿真

2.1.1 電源電壓

圖3 是RESET 和RESET1 引腳有效最小電壓值前仿真圖。圖中介紹了RESET 引腳和RESET1引腳的前仿真的具體連接方式。表1 為RESET 和RESET1 引腳有效最小電壓值。

2.1.2 靜態電流

靜態電流前仿真圖如圖3 所示。電源監控電路靜態電流的前仿真結果如表2 所示。

從前仿真圖以及靜態電流的前仿真結果來看,當VCC 介于復位閾值電壓(VRST)和5.5 V 之間時,靜態電流的最大值為37 μA,符合設計要求。

2.1.3 復位閾值電壓及遲滯電壓

表3 為復位閾值電壓及遲滯電壓(VHYS)的前仿真結果。從表3 中可以得出,前仿真中復位閾值電壓VRST和遲滯電壓VHYS 均符合設計要求。

從前仿真圖以及前仿真結果來看,RESET 和RESET1 的引腳有效最小電壓值為970 mV,滿足設計要求。

2.1.4 復位信號脈沖寬度

表4 為復位信號脈沖寬度前仿真結果。從表4的前仿真結果可以看出,VRST 和VHYS 復位信號脈沖寬度均滿足設計要求。

2.1.5 輸出高低電平

輸出高低電平前仿真結果如表5 所示。從表5 可以得出,輸出高低電平的前仿真結果均符合設計要求。

2.2 電源監控電路后仿真

與前仿真類似,對電源監控電路也分別做了關于“電源電壓”“靜態電流”“復位閾值電壓及遲滯電壓”“復位信號脈沖寬度”“輸出高低電平”的后仿真測試,其中這些后仿真結果均符合設計要求。

3 版圖設計

版圖(layout)集成電路設計者將設計并模擬優化的電路轉化成一系列幾何圖形,其包含了集成電路尺寸大小等有關器件的所有物理信息。集成電路制造廠家根據這些信息來制造。

3.1 版圖概述

本電源監控電路的工藝流片選擇華潤上華“0.25 μm BCD”工藝加工,該工藝經過大規模量產,工藝穩定,可靠性高。根據上述設計結果,設計版圖。

3.2 芯片面積

本電源監控電路設計的芯片面積如表6。

3.3 電源監控電路芯片示意圖

按照上述方案開展了電源監控電路芯片的原理設計、仿真驗證和版圖設計,完成了電路的設計工作。圖4 為電源監控電路芯片示意。

4 結論

本電路通過低溫票帶隙基準設計,其上電復位和欠壓保護的精度和溫度特性良好。在-55 ~ 125℃全溫度范圍內在上電、斷電和掉電過程中提供一個復位信號,兼容TTL/CMOS 手動復位輸入,兼容高/ 低電平有效(RESET/ ?RESET)。仿真證明該電路閾值電壓隨溫度變化極小,性能更加穩定可靠,相較于分離元器件,其能夠顯著提高系統的可靠性和精度,并且實現了更低的功耗。