基于Chipyard的RISC-V處理器設計與實現

譚飛鴻,蘇成悅

(廣東工業大學物理與光電工程學院,廣州 510000)

0 引言

在計算機領域,軟硬件之間的接口規范就是指令集[1]。RISC-V 是一個自由開放的指令集,具有良好的模塊化結構,可用于多種應用場景的芯片定制[2]。國內已涌現大量的基于RISC-V指令集架構的芯片,如平頭哥半導體公司研發的應用于物聯網的處理器CK902[3]、中國科學院計算機技術所研發的RISC-V 處理器“香山”[4]以及芯來科技研發的廣泛應用于嵌入式領域的處理器蜂鳥E203[5]等。Chipyard 是一個基于Chisel開發的處理器生成器框架,它集成芯片從設計到驗證的全流程工具鏈,降低了芯片開發難度,基于Chipyard 框架開發的多款處理器芯片已流片[6]。

本文將在Chipyard 框架下實現基于RISC-V指令集架構的五級流水線處理器設計,并在FPGA 上完成板級驗證,Dhrystone測試性能達到1.27 DMIPS/MHz。

1 RISC-V指令集架構及流水線設計

采用增量指令集架構(instruction set architecture,ISA)的計算機體系結構,處理器迭代過程中為保持向后的二進制兼容,ISA 的體量逐漸增大,而RISC-V 采用模塊化的方式規避體量問題[7]。RISC-V 基于基本軟件棧,提供多個標準擴展,而無需為冗余的指令分攤成本。

1.1 RIISSCC--VV指令集

RISC-V 開發團隊于2017 年正式發布第一版規范,規定指令的格式、操作方式、數據類型和內存管理機制等內容[8]。規范凸顯RISC-V 的可裁剪性和定制性,實現不同應用場景下的處理器設計需求。RISC-V 指令集由一個基礎指令集和多個擴展指令集構成,工作在特定的工作模式下[9]。

最新一版規范規定了五種基礎指令集[10],分別是弱內存次序指令集RVWMO、32 為整數指令集RV32I、64 位整數指令集RV64I、128 位整數指令集RV128I 和32 位嵌入式整數指令集RV32E。RVWMO內存一致性模型由內存模型原語、指令依存句法和程序次序組成,并滿足加載值公理、原子性公理和進度公理[11]。RV32I、RV64I 和RV128I 都屬于整數指令集,區別在于寄存器的位寬大小。RV32E是用于嵌入式設計的指令集,它僅有16個整數寄存器[12]。基礎指令集格式一共有六種,以RV32I為例,如圖1所示。

圖1 RV32I的六種基礎指令格式

擴展指令集是RISC-V 靈活性的體現,可與基礎指令集組合應對各種應用場景。截至2022年6月,規范共發布40多種擴展指令[10]。

1.2 RIISSCC--VV編譯鏈

編譯器將高級編程語言編譯成可執行文件,RISC-V 編譯鏈有其獨特的函數調用規范(calling convention)[13]。函數調用時規定是否保留寄存器數據,若過程和方法不產生其它調用,將由程序二進制接口(application binary interface,ABI)自由分配寄存器,無需保存和恢復[14]。鏈接器將目標代碼和機器語言模塊進行鏈接,使編譯和匯編相互獨立進行,節約時間開銷。加載器將可執行文件加載到內存中,并跳轉至程序執行的開始地址,常用的編譯工具有riscv-gnu-toolchain[15]。

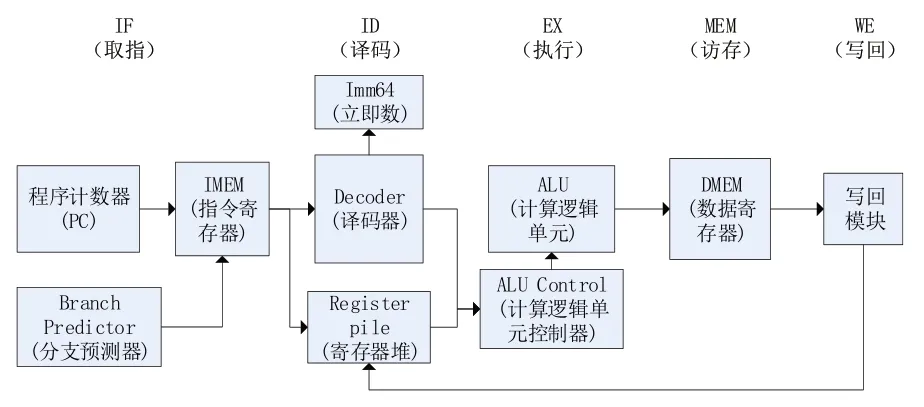

1.3 五級流水線設計

流水線技術能使多條指令重疊執行,它將有效提高指令整體執行速度[16]。流水線級數與寄存器的電路延時和硬件面積有關[17]。圖2 所示為流水線整體設計圖,包括取指(IF)、譯碼(ID)、執行(EX)、訪存(MEM)、寫回(WE)。

圖2 五級流水線總體結構

取指階段程序計數器(PC)從指令寄存器(IMEM)取出指令,分支預測模塊會預測下一條指令;譯碼階段將提取指令操作碼、功能碼、立即數、目的寄存器和源寄存器等信息;執行階段由ALU 和ALU 控制器執行運算。當指令涉及對內存的讀寫操作,將進入訪存和寫回階段。

2 Chipyard框架

Chipyard 為敏捷的SoC 開發提供統一的框架和工作流程,通過配置和互連多個獨立IP 以確保SoC 的完整性[18]。生成的SoC 可以通過FPGA加速和電子設計自動化軟件(EDA)進行驗證,最后通過可移植的超大規模集成電路(VLSI)設計流程獲取GDSⅡ數據庫。GDSⅡ是一個二進制文件,用于重構版圖信息,以此制作掩模版[19]。

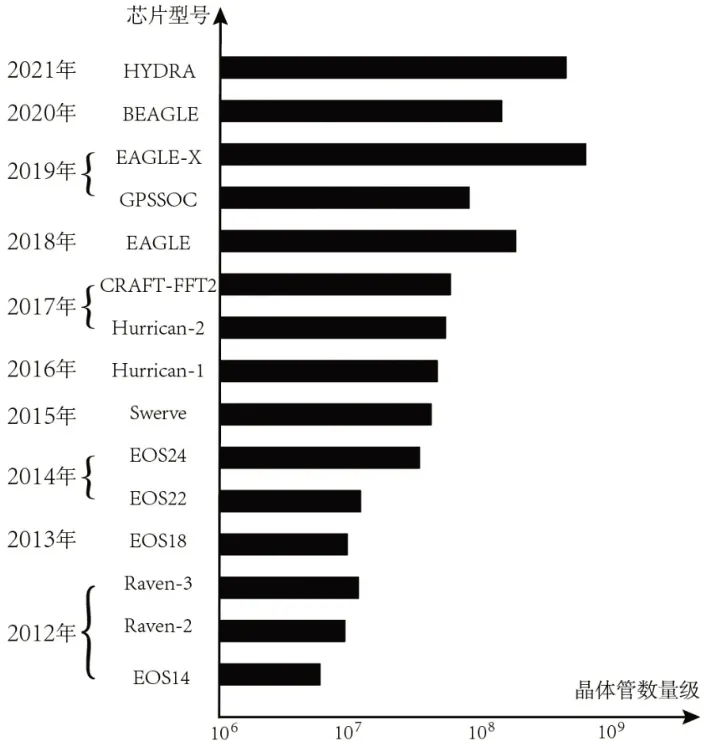

截至2021 年,基于Chipyard 框架開發的已實現流片(Tape Out)的SoC 復雜度呈現出逐年增加的趨勢[18],如圖3所示。

圖3 基于Chipyard框架構建的RISC-V SoC測試芯片的復雜度變化趨勢

2.1 Chhiisseell敏捷開發

Chisel(constructing hardware in a scala embedded language)采用Scala 作為宿主語言[20],Scala 基于JVM(java virtual machine)開發。傳統處理器開發主要基于Verilog 和VHDL 語言,但二者功能復用性差,同等電路設計較Chisel代碼更繁瑣。Chisel具有面向對象、函數式編程、參數化編程和類型推理的特性[21]。Chisel可進行復雜電路設計,并創建可復用的電路模塊,編譯成Verilog代碼在EDA中進行仿真。

Chisel并不是高層次綜合(high-level synthesis,HLS),而是屬于寄存器轉換級(register transfer level,RTL)語言,而HLS是將行為級描述的高級語言編譯成RTL,例如C/C++編寫程序,并直接將其轉化為Verilog代碼[22],這將降低硬件開發的靈活性和顆粒度。處理器開發和迭代過程中涉及大量參數,許多模塊可以通過派生、繼承和重載來實現,使得基于Chisel開發的優勢得以凸顯。

2.2 Chippyyaarrdd框架構成

Chipyard 包括可配置、模塊化和開源的IP,涵蓋SoC 設計階段全流程。Chipyard 繼承于Rocket Chip 框架[23],Rocket Chip 同為伯克利團隊基于Chisel 開發的SoC 生成器。Chipyard 在Rocket Chip 基礎庫上增加大量的IP,比如伯克利亂序機(BOOM)[24]、Hwacha 矢量單元[25]、數字信號處理模塊(DSP)、內存系統和外設等。

Chipyard 依賴靜態接口用于集成IP 核,硬件生成階段動態生成編碼、內存映射和總線,在內存映射IO(MMIO)外圍作為加速器和控制器[26]。在本文的處理器設計中,處理器核由具備Linux 能力的Rocket 核組成,支持RV64GC,擁有浮點單元和虛擬內存。相較其他直接替換內核的SoC 開發框架,Chipyard 的通用內核配置接口提高了開發效率。

2.2.1 Chippyyaarrdd開發流程

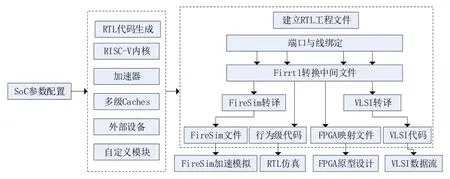

Chipyard 框架整合大量工具包,用于SoC 設計周期內的三個主要環節:前端RTL 設計、系統驗證和后端芯片物理設計。

由于Chisel 在SoC 設計到實現流程中會缺失原始信息,導致Chipyard 在前端RTL 設計中不能直接生成RTL 文件,所以要通過FIRRTL 作為中間態(IR),再由FIRRTL編譯器生成Verilog代碼[27]。基于Verilog 或SystemVerilog 的設計框架在仿真、模擬和物理設計之間轉換時必須依賴特定的設計腳本,而基于FIRRTL 編譯器的轉換方法更加靈活,可應用在Chipyard 框架集成的Chisel設計中。

圖4展示Chipyard 的開發流程,根據設計需求進行SoC 參數配置,主要包括RISC-V 內核、加速器、Caches、外部設備和自定義模塊,通過軟件建立RTL 文件工程,并將生成的處理器部署在FPGA 上。Chipyard 擁有開源的RTL 仿真器Verilator,框架中的Makefile 將根據SoC 的結構完成仿真可執行文件和頂層設計文件的生成和軟件匹配,并輸出測試結果。Chipyard對最終生成的處理器可直接進行FPGA部署,如由亞馬遜EC2 公共云推出的FireSim FPGA 加速仿真平臺[28],FireSim 可以模擬時序行為、I/O 和外設,配合Chipyard 框架的全系統性可以完成硅前驗證和性能評估。Chipyard后端物理設計中支持模塊化VLSI 流程,如Hammer VLSI 模塊[29],可通過抽象化軟件API 生成Tcl 腳本、時鐘約束和功率規格對特定供應商的組件進行復用和模塊化。

圖4 Chipyard通過生成器支持多種轉換的設計流程

SoC開發作為計算機科學的重要領域也面臨著可重復性危機[30],當一個低級電路需要升級為更高級的電路被應用時,軟件棧需要跟蹤所有硬件接口并保持版本匹配,這使軟件工作負載管理復雜度增加。FireMarshal[31]是基于RISC-V 的全棧硬件開發的軟件工作負載管理工具,可實現自動化工作負載生成、開發和評估,通過允許用戶以可存儲、版本控制、共享無歧義可讀形式描述和共享工作負載來使得Chipyard避免重復性危機。如圖5所示,全棧式硬件開發組件在系統迭代中會保留大部分原先版本,FireMarshal 使核心應用邏輯和部分組件與新的SoC 設計一致,只改變內核和驅動配置以適應新的系統,這將大大減少SoC設計中的重復性工作。

圖5 Chipyard使用FireMarshal進行軟件工作負載管理

2.2.2 軟核配置

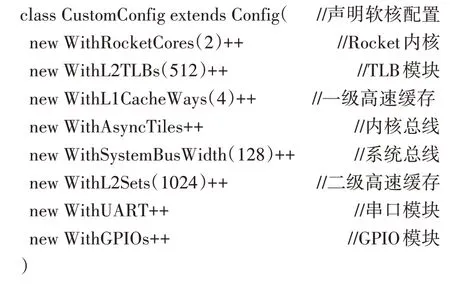

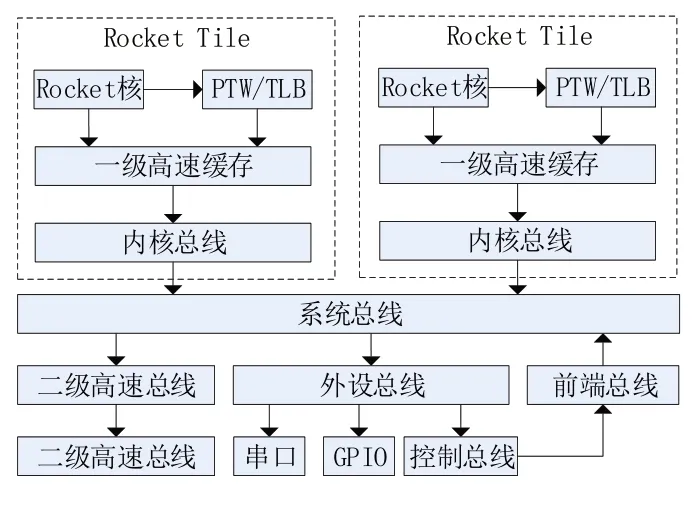

圖6 所示為RISC-V SoC 結構設計圖,各部分對應代碼如下。

圖6 RISC-V SoC結構設計圖

Rocket核是順序執行流水線內核,指令集所需數據可從頁表控制器(page table walker,PTW)中獲取,PTW 包含虛擬地址和物理地址之間的映射表,虛擬地址在編譯時由鏈接器生成,由頁號和頁偏移組成,頁號用于檢索頁表得到物理塊號,并與頁偏移一起載入物理地址寄存器中。內核總線用于一級高速緩存(cache)和系統總線上的設備之間的通信,系統總線(system bus)包括數據總線、地址總線和控制總線。二級高速緩存連接內存總線,內存總線通常是通過AXI 轉換器連接DRAM 控制器;外設總線則是連接各個外部設備,包括串口、GPIO 等。CPU 可通過前端總線和外部通信,如內存系統可通過前端總線對DMA設備進行讀寫。

3 驗證測試

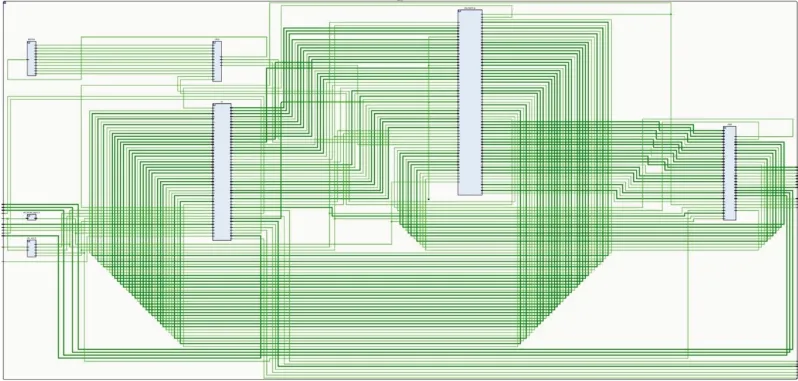

Chipyard框架生成的處理器并不以電路圖形式呈現,Chisel 進行處理器設計和實現是解耦的,缺少集成環節,故在轉換Verilog 代碼過程中會損失端口信息,而且在ECO(engineering change order)階段,Chisel 無法精確控制網表生成,使后端實現需要重新做布局規劃(floor plan),而在Firrtl 層面允許設計者自定義轉換(transform)[27],所以Chisel 在生成電路圖前會先編譯成Firrtl文件,進而生成Verilog文件。

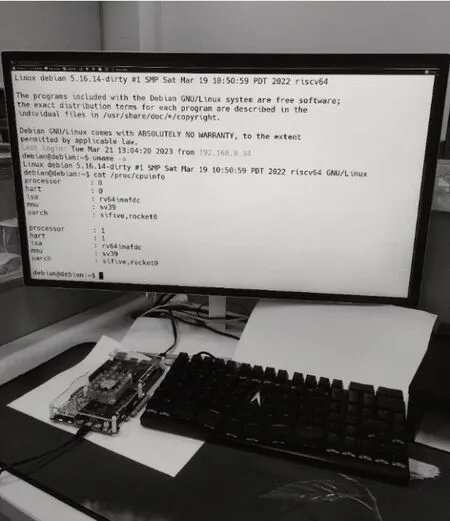

圖7為Chipyard生成的RISC-V SoC的電路原理圖,利用EDA 生成比特流并固化在FPGA 上,部署Linux操作系統,通過網絡實現人機交互。存儲器管理單元(memory management unit,MMU)是通過快表(translation lookaside buffer,TLB)來實現地址轉換[32],Linux 操作系統采用分頁式內存管理機制。圖8為FPGA板級驗證的實物展示。

圖7 基于Chipyard生成的RISC-V SoC的電路原理圖

圖8 FPGA板級驗證實物

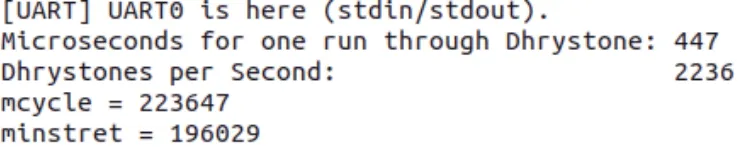

Dhrystone 是誕生于1984 年的綜合性測試程序,輸出結果代表每秒運行Dhrystone的次數,因其簡潔、直觀,至今依舊被廣泛應用于CPU性能測試。圖9為RISC-V SoC 的Dhrystone測試結果,結果顯示SoC每秒運行2236次Dhrystone程序。

圖9 Dhrystones運行結果

4 結語

本文驗證了一種高效的RISC-V SoC 開發方法,并在FPGA 上成功運行,Chipyard 支持日益復雜和差異化的定制SoC。從表1 中得出部分處理器對比結果,本文所設計的SoC 的跑分與STM32F407VET6相近,性能優于基于ARM 的第二代樹莓派處理器。

表1 各架構典型的處理器Dhrystone跑分比較