面向疏浚工程的電阻層析測(cè)量系統(tǒng)優(yōu)化設(shè)計(jì)

于 濤,羅 剛,辛長(zhǎng)浩,岳士弘

(1.中交天津航道局有限公司,天津 300457; 2.天津大學(xué)電氣自動(dòng)化與信息工程學(xué)院,天津 300072)

0 引言

疏浚工程[1]主要集中在海域作業(yè)。船體時(shí)常會(huì)產(chǎn)生大范圍的靜電,并且船上有大量用于保證疏浚作業(yè)正常進(jìn)行的高功率電子器件。這會(huì)導(dǎo)致疏浚船體上存在大量的、各種頻率的電磁噪聲。目前,電阻層析測(cè)量系統(tǒng)已經(jīng)應(yīng)用于疏浚工程中[2-3]。電阻層析測(cè)量系統(tǒng)包括3個(gè)主要部分,分別為傳感器、數(shù)據(jù)采集系統(tǒng)和上位機(jī)。數(shù)據(jù)采集系統(tǒng)是電阻層析系統(tǒng)的核心部分,不僅通過(guò)傳感器完成測(cè)量對(duì)象信號(hào)采集,還要把信號(hào)通過(guò)通信接口傳到上位機(jī)進(jìn)行參數(shù)檢測(cè)和控制。若要保證數(shù)據(jù)采集系統(tǒng)對(duì)應(yīng)的測(cè)量系統(tǒng)在疏浚船體上正常運(yùn)行,則需要對(duì)當(dāng)前系統(tǒng)進(jìn)行深度優(yōu)化,以提高信噪比[4-6]。在實(shí)際工況中,疏浚管道內(nèi)的泥漿流速較快。然而,當(dāng)前測(cè)量系統(tǒng)的采集信號(hào)頻率較低,測(cè)量周期內(nèi)的管道截面會(huì)產(chǎn)生較大變化,造成單組測(cè)量值與疏浚管道截面分布的一致性無(wú)法保證。為了提高系統(tǒng)的實(shí)時(shí)性以及信號(hào)采集的精度和穩(wěn)定性,需要提升系統(tǒng)的信號(hào)頻率。

本文主要圍繞電阻層析的數(shù)據(jù)采集系統(tǒng)以及上位機(jī)系統(tǒng)進(jìn)行相關(guān)優(yōu)化,以提高測(cè)量的激勵(lì)信號(hào)頻率、采集速率和測(cè)量系統(tǒng)在疏浚管道上作業(yè)的精確性以及穩(wěn)定性。

1 電阻層析數(shù)據(jù)采集系統(tǒng)

當(dāng)前普遍使用的電阻層析數(shù)據(jù)采集系統(tǒng)的主要參數(shù)如下:采集速度為60 fps;信噪比為52 dB;系統(tǒng)信號(hào)頻率為80 kHz。該系統(tǒng)具有集成度高、易于擴(kuò)展、傳輸速度快等特點(diǎn)[7-8]。

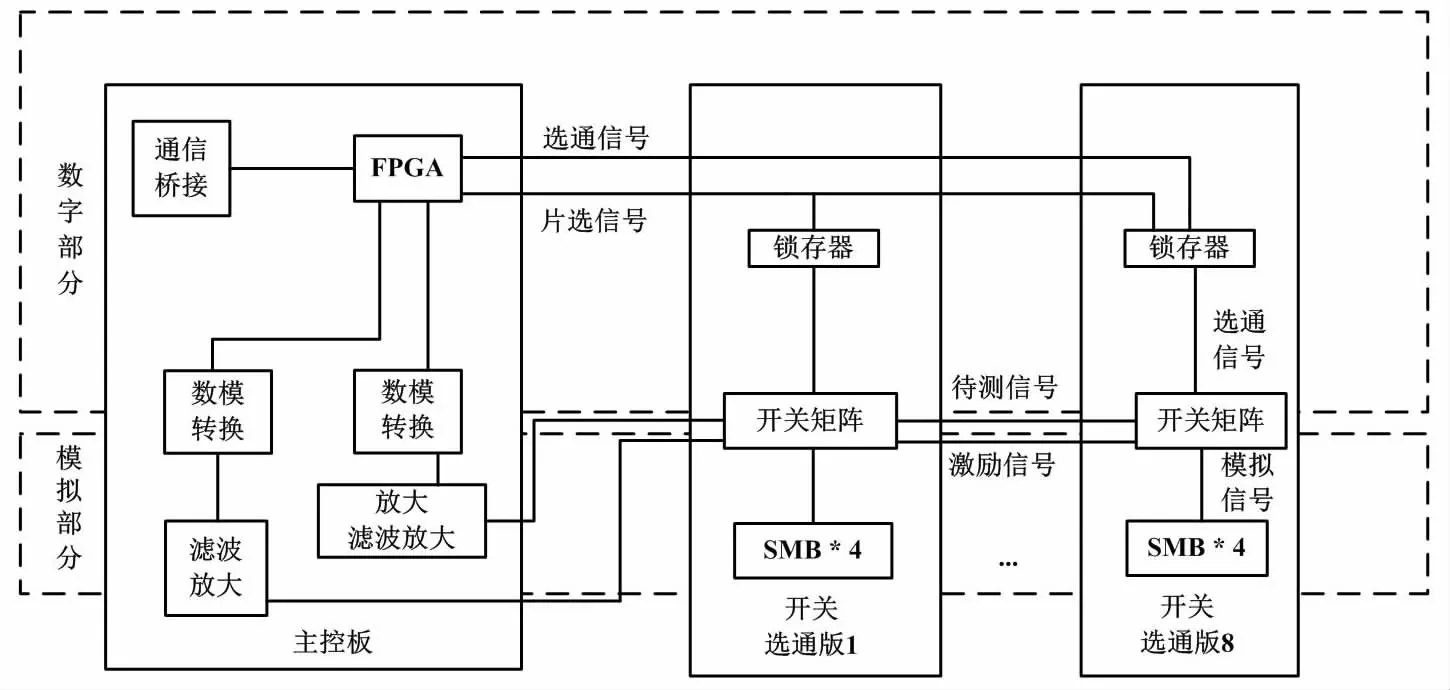

數(shù)據(jù)采集系統(tǒng)是整個(gè)電阻層析測(cè)量系統(tǒng)的核心,主要由主控板和選通板組成。數(shù)據(jù)采集系統(tǒng)的主要功能為激勵(lì)信號(hào)的產(chǎn)生、測(cè)量信號(hào)的捕捉、模擬到數(shù)字/數(shù)字到模擬轉(zhuǎn)換、選通電路的切換、測(cè)量信號(hào)的解調(diào)及可編程放大、與上位機(jī)的通信等。

主控板的核心功能如下:核心處理單元現(xiàn)場(chǎng)可編程門陣列(field programmable gate array,FPGA)接收上位機(jī)相關(guān)命令并進(jìn)行相關(guān)處理;FPGA產(chǎn)生的數(shù)字信號(hào)轉(zhuǎn)換為模擬信號(hào),并經(jīng)過(guò)一系列的放大濾波傳輸至激勵(lì)電極;對(duì)測(cè)量電極端的電流進(jìn)行差分濾波,并將其轉(zhuǎn)換為數(shù)字信號(hào)傳輸至核心處理單元FPGA;將接收到的測(cè)量信號(hào)進(jìn)行解調(diào)放大并傳輸至上位機(jī)。選通板共8個(gè)。每個(gè)選通板均可以對(duì)4個(gè)電極進(jìn)行選通,并分別對(duì)應(yīng)了雙排各16個(gè)電極。選通板主要負(fù)責(zé)對(duì)各電極進(jìn)行“激勵(lì)”“測(cè)量”“接地”3個(gè)狀態(tài)的選通。當(dāng)16個(gè)電極中的1個(gè)電極選通為“激勵(lì)”狀態(tài)、1個(gè)電極為“測(cè)量”狀態(tài)時(shí),其余14個(gè)電極皆為“接地”狀態(tài)。數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)如圖 1所示。

圖1 數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)示意圖

2 數(shù)據(jù)采集系統(tǒng)的優(yōu)化

2.1 影響數(shù)據(jù)采集系統(tǒng)性能的主要因素

影響信噪比的主要因素如下[9-10]。 疏浚管道內(nèi)泥漿成分復(fù)雜,并且受其他電磁元件的干擾,被測(cè)場(chǎng)域攜帶大量的電磁信號(hào)。這會(huì)導(dǎo)致測(cè)量回路中攜帶大量的高低頻噪聲。因此,需要在測(cè)量回路中進(jìn)行頻譜分析,并觀察噪聲的頻域分布,從而增加相應(yīng)的濾波器以消除相關(guān)噪聲。

影響采集速率的主要因素如下[11]。數(shù)據(jù)采集系統(tǒng)的信號(hào)采集速率主要由系統(tǒng)的單個(gè)周期時(shí)間決定,即獲取1組480個(gè)測(cè)量值的時(shí)間。影響系統(tǒng)單個(gè)周期時(shí)間的主要因素有電極狀態(tài)選通的速率、FPGA釋放的信號(hào)頻率和通信模塊的傳輸速率。

當(dāng)前系統(tǒng)獲取雙排電極測(cè)量值的主要方式為串行選通[12],即進(jìn)行第一排電極選通測(cè)量后,進(jìn)行第二排電極的選通測(cè)量。這種串行方式嚴(yán)重降低了8個(gè)選通板電極狀態(tài)選通的速率。對(duì)此,可以通過(guò)將選通方式改為并行方式,降低系統(tǒng)的單個(gè)工作周期時(shí)間。并行的電極選通方式需要占據(jù)FPGA雙倍的輸入/輸出(input/output,I/O)引腳。然而,當(dāng)前FPGA的剩余I/O資源不足以支撐這樣的改變,所以需要更換FPGA芯片,重新進(jìn)行外圍電路的設(shè)計(jì)以及I/O資源的分配。

整個(gè)系統(tǒng)中的激勵(lì)信號(hào)頻率與測(cè)量信號(hào)頻率相同,都來(lái)源于FPGA芯片中的直接數(shù)字式合成器(direct digital synthesizer,DDS)知識(shí)產(chǎn)權(quán)(intellectval property,IP)核。然而,采集系統(tǒng)中的信號(hào)頻率不僅僅由FPGA決定。電路設(shè)計(jì)中的數(shù)模(diagtal to analog,D/A)轉(zhuǎn)換模塊、模數(shù)(analog to digital,A/D)轉(zhuǎn)換模塊、濾波器的截止頻率,以及開關(guān)芯片的截止頻率,都是決定信號(hào)頻率的關(guān)鍵因素。從目前各電子元器件的最高工作頻率來(lái)看,影響系統(tǒng)信號(hào)頻率的主要因素為A/D轉(zhuǎn)換芯片、開關(guān)芯片以及通信模塊。對(duì)此,可以通過(guò)選擇具有更高工作頻率的相關(guān)芯片來(lái)提高系統(tǒng)高頻率運(yùn)行的可行性。

在整個(gè)測(cè)量周期當(dāng)中,上下位機(jī)通信占據(jù)了大部分時(shí)間,所以提升通信模塊的傳輸速率對(duì)提高系統(tǒng)的采集速率至關(guān)重要。

綜合上述對(duì)信號(hào)干擾以及工作頻率的分析,后續(xù)研究將圍繞FPGA測(cè)量回路、A/D轉(zhuǎn)換、選通電路這3個(gè)方面進(jìn)行相關(guān)優(yōu)化。

2.2 測(cè)量回路優(yōu)化

測(cè)量回路主要用于接收從傳感器電極上流出的電流信號(hào),并將其傳輸至FPGA。測(cè)量信號(hào)攜帶了場(chǎng)域電導(dǎo)率分布的相關(guān)信息。然而,由于疏浚管道場(chǎng)域內(nèi)信號(hào)冗雜,測(cè)量信號(hào)中會(huì)攜帶各種頻率的噪聲,故需要在測(cè)量回路中增添一系列的信號(hào)處理電路,從而得到高精度的測(cè)量信號(hào)。

通過(guò)示波器觀察AD8129差分轉(zhuǎn)單端后獲得的測(cè)量信號(hào)可知,其中含有遠(yuǎn)高于80 kHz的高次諧波。經(jīng)觀察,此高次諧波信號(hào)大約處于4 MHz的頻段。故本文選擇二階Salley-Kelly低通濾波器,并設(shè)置其截止頻率為3 MHz。此時(shí),測(cè)量信號(hào)中的大部分噪聲信號(hào)已被濾除,有利于提高信噪比。

2.3 A/D轉(zhuǎn)換優(yōu)化

相敏解調(diào)是在FPGA得到測(cè)量值過(guò)程中的關(guān)鍵步驟。該步驟要求經(jīng)FPGA采樣得到的A/D數(shù)字信號(hào)必須與DDS IP核輸出的數(shù)字信號(hào)在分辨率與信號(hào)頻率上達(dá)到一致,即A/D轉(zhuǎn)換模塊與D/A轉(zhuǎn)換模塊在分辨率與采樣頻率上應(yīng)保持一致。所以數(shù)據(jù)采集系統(tǒng)中的信號(hào)頻率不只由DDS IP核輸出端直接決定, A/D轉(zhuǎn)換過(guò)程也是關(guān)鍵限制條件。以下對(duì)A/D轉(zhuǎn)換過(guò)程涉及的分辨率、采樣頻率等關(guān)鍵參數(shù)進(jìn)行分析。

①分辨率。分辨率代表數(shù)字信號(hào)量的最低有效位發(fā)生變化時(shí)所帶來(lái)的模擬量變化。分辨率越高,則數(shù)字量的變化越精細(xì)。分辨率表示數(shù)字信號(hào)量的位寬,故A/D轉(zhuǎn)換芯片位寬越大,輸出的數(shù)字信號(hào)精度越高。

②采樣頻率。A/D轉(zhuǎn)換輸出的單周期信號(hào)量個(gè)數(shù)由A/D轉(zhuǎn)換芯片的采樣頻率以及模擬信號(hào)的頻率決定。

(1)

式中:f為模擬信號(hào)頻率,Hz;fs為采樣頻率,Hz;N為單周期信號(hào)量個(gè)數(shù)。

不同的單周期信號(hào)量個(gè)數(shù)直接決定了A/D轉(zhuǎn)換的最終效果。單周期信號(hào)量個(gè)數(shù)越多,則輸出的數(shù)字信號(hào)與模擬信號(hào)的相似性越高。

根據(jù)當(dāng)前對(duì)系統(tǒng)信號(hào)頻率的需求,若要獲得更高的信號(hào)頻率,并且保證當(dāng)前單周期信號(hào)量的個(gè)數(shù),必須提高A/D轉(zhuǎn)換模塊以及D/A轉(zhuǎn)換模塊的采樣頻率。當(dāng)前系統(tǒng)D/A轉(zhuǎn)換模塊與A/D轉(zhuǎn)換模塊的采樣頻率均為10 MHz,由FPGA直接提供。其中:D/A轉(zhuǎn)換芯片AD9764最高采樣頻率為125 MHz;A/D轉(zhuǎn)換芯片AD9240最高采樣頻率為10 MHz。當(dāng)前的采樣頻率即AD9240的最高采樣頻率,所以AD9240芯片直接限制了數(shù)據(jù)采集系統(tǒng)的信號(hào)頻率。

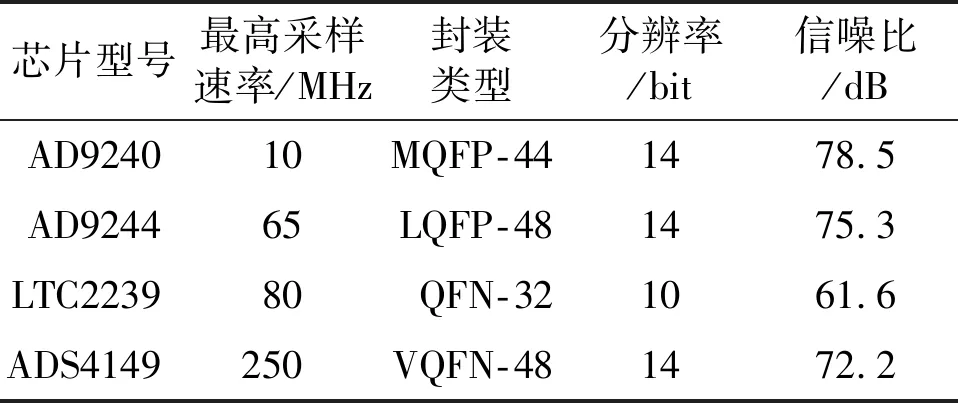

綜合上述分析,必須通過(guò)更換A/D轉(zhuǎn)換芯片才能提高數(shù)據(jù)采集系統(tǒng)的信號(hào)頻率。目前常見(jiàn)的A/D轉(zhuǎn)換芯片的性能參數(shù)如表1所示。

表1 常見(jiàn)的A/D轉(zhuǎn)換芯片的性能參數(shù)

綜合考慮采樣頻率、成本、精度等條件,本文采用14位高速A/D轉(zhuǎn)換器AD9244。為了使FPGA獲得完整的數(shù)據(jù),本文需要對(duì)基于FPGA的采樣時(shí)刻和AD9244的D/A轉(zhuǎn)換過(guò)程進(jìn)行分析。

AD9244 A/D轉(zhuǎn)換模塊外圍電路設(shè)計(jì)如圖2所示。

圖2 AD9244 A/D轉(zhuǎn)換模塊外圍電路設(shè)計(jì)

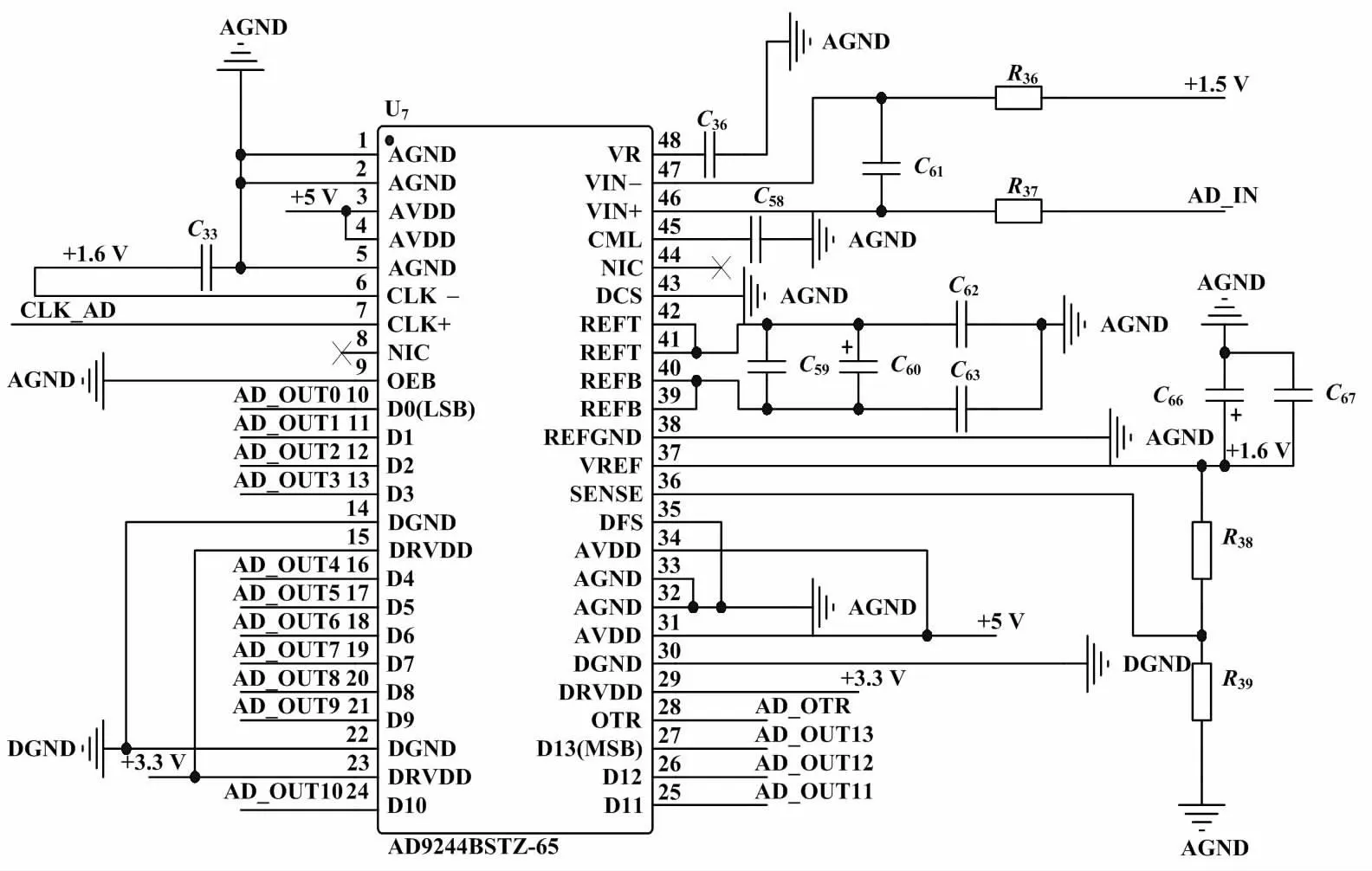

AD9244 A/D轉(zhuǎn)換時(shí)序如圖3 所示。

圖3 AD9244 A/D轉(zhuǎn)換時(shí)序圖

由于AD9244的轉(zhuǎn)換時(shí)間tOD為4~5 ns,即AD9244在轉(zhuǎn)換時(shí)間tOD范圍后才可以輸出穩(wěn)定的數(shù)字信號(hào)。FPGA采樣點(diǎn)應(yīng)在數(shù)字信號(hào)穩(wěn)定時(shí)進(jìn)行采樣。

AD9244的采樣頻率最高為65 MHz,周期為15 ns。在最高采樣頻率下,AD9244的下半周期數(shù)據(jù)理論穩(wěn)定,所以FPGA應(yīng)選擇在時(shí)鐘下降沿進(jìn)行采樣,從而保證獲得穩(wěn)定的數(shù)字信號(hào)。

2.4 選通電路優(yōu)化

在數(shù)據(jù)采集系統(tǒng)中,選通電路是電極與激勵(lì)測(cè)量回路建立鏈接的關(guān)鍵部分。在整體的激勵(lì)測(cè)量過(guò)程以及選通過(guò)程中,若要提高信號(hào)頻率并且加快開關(guān)切換速度,對(duì)開關(guān)芯片的導(dǎo)通時(shí)間、通路電阻、漏電流、隔離度以及通路切換時(shí)間都提出了一定的要求。對(duì)于當(dāng)前使用的DG413這類隔離度較低的金屬-氧化物-半導(dǎo)體(metal-oxide-semiconductor,MOS)開關(guān)芯片,在通路信號(hào)頻率較高的情況下無(wú)法達(dá)到阻塞信號(hào)的作用。因此,要提高信號(hào)頻率,必須更換當(dāng)前使用的開關(guān)芯片。

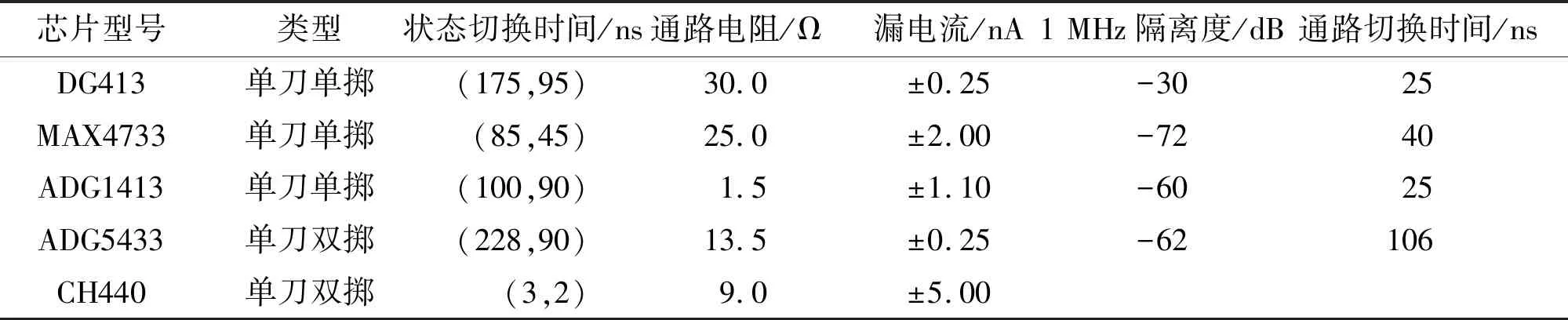

目前常用模擬開關(guān)芯片的性能參數(shù)如表2所示。

表2 常用模擬開關(guān)芯片的性能參數(shù)

信號(hào)頻率較高的電路除了對(duì)隔離度有較高要求外,對(duì)開關(guān)芯片中的導(dǎo)通電阻、通路切換時(shí)間也提出了一定的要求。常用的開關(guān)芯片中單刀單擲開關(guān)ADG1413以及單刀雙擲開關(guān)ADG5433都基本滿足要求。

若采用單刀單擲開關(guān),則無(wú)需對(duì)原有的選通電路單元進(jìn)行結(jié)構(gòu)修改,只要將原有的DG413更改為ADG1413即可。

若采用單刀雙擲開關(guān),則可以有效減少開關(guān)數(shù)量。但這樣仍需要針對(duì)漏電流問(wèn)題進(jìn)行電路結(jié)構(gòu)調(diào)整,以消除其對(duì)測(cè)量結(jié)果的影響。

3 優(yōu)化系統(tǒng)驗(yàn)證

為了驗(yàn)證本文方案對(duì)電阻層析數(shù)據(jù)采集系統(tǒng)的優(yōu)化性能,測(cè)試先將FPGA的輸出波形頻率設(shè)置為160 kHz,再將AD9764與AD9240的采樣頻率設(shè)置為20 MHz,最后將RS485的波特率修改為2 Mbit/s。此時(shí),整個(gè)系統(tǒng)的激勵(lì)頻率為160 kHz。本文利用優(yōu)化后的電阻層析數(shù)據(jù)采集系統(tǒng),對(duì)當(dāng)前系統(tǒng)的信噪比進(jìn)行靜態(tài)試驗(yàn)驗(yàn)證。其中:靜態(tài)水盆裝置內(nèi)徑為16 cm;液相背景采用電導(dǎo)率為260 μs/cm的自來(lái)水。

激勵(lì)大小設(shè)置為2 V。在純液態(tài)下,試驗(yàn)連續(xù)采集1 000組測(cè)量值,并利用連續(xù)多組測(cè)量值數(shù)據(jù)對(duì)當(dāng)前系統(tǒng)進(jìn)行信噪比分析。

信噪比的計(jì)算式如下。

(2)

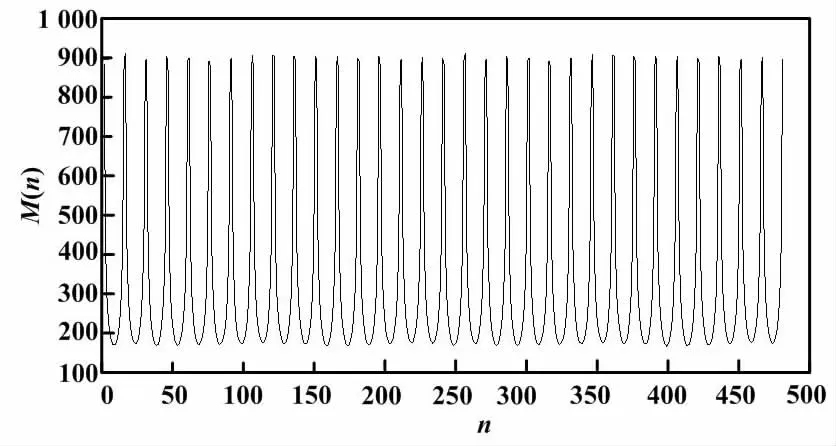

測(cè)量值序列由480個(gè)測(cè)量值組成。電阻層析測(cè)量系統(tǒng)的單組測(cè)量值結(jié)果如圖4所示。

圖4 電阻層析測(cè)量系統(tǒng)的單組測(cè)量值結(jié)果

若需要衡量整個(gè)電阻層析測(cè)量系統(tǒng)的抗干擾能力,則必須分別計(jì)算電阻層析數(shù)據(jù)采集系統(tǒng)對(duì)480個(gè)測(cè)量值的信噪比,再計(jì)算所有結(jié)果的期望,從而得到整個(gè)系統(tǒng)的信噪比。

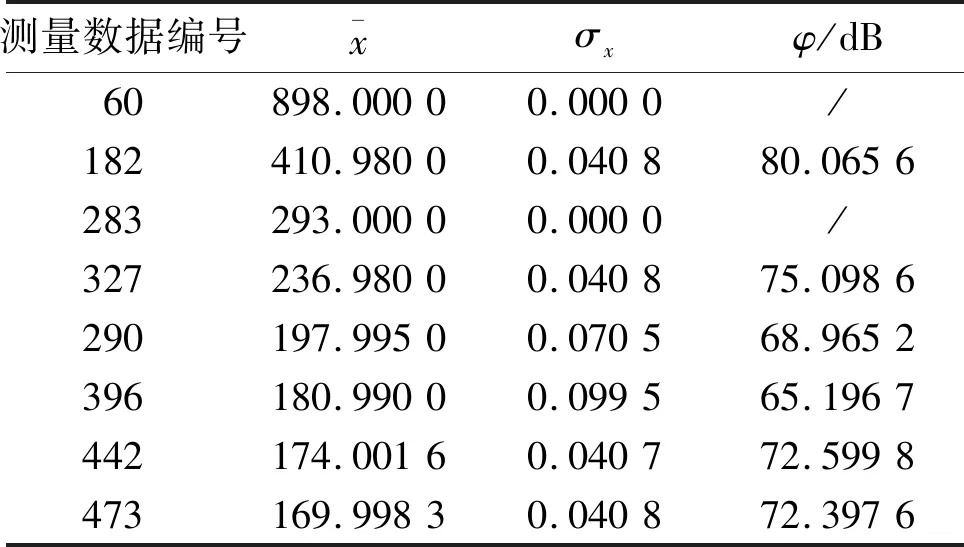

部分測(cè)量值的信噪比如表3所示。

表3 部分測(cè)量值的信噪比

由表3可知,大部分測(cè)量值的信噪比都在65 dB以上,且部分測(cè)量值在1 000組數(shù)據(jù)中沒(méi)有任何波動(dòng)。其標(biāo)準(zhǔn)差為0,信噪比很好。在計(jì)算所有測(cè)量值的信噪比期望時(shí),信噪比為“/”的參數(shù)設(shè)置為100 dB,從而得到當(dāng)前系統(tǒng)的信噪比為73 dB。綜合上述分析,系統(tǒng)整體的信噪比相較于原有系統(tǒng)的52 dB得到了顯著的提升。

4 結(jié)論

針對(duì)當(dāng)前疏浚工程的測(cè)量要求,本文在現(xiàn)有電阻層析測(cè)量系統(tǒng)基礎(chǔ)上,圍繞電阻層析測(cè)量系統(tǒng)的傳感器陣列、數(shù)據(jù)采集系統(tǒng)和上位機(jī)測(cè)量系統(tǒng)3個(gè)部分進(jìn)行優(yōu)化。首先,本文根據(jù)疏浚管道的實(shí)際工況以及電阻層析技術(shù)對(duì)傳感器陣列的要求,對(duì)傳感器陣列進(jìn)行了耐久性、穩(wěn)定性和抗干擾性方面的優(yōu)化。其次,從電阻層析數(shù)據(jù)采集系統(tǒng)出發(fā),分析了影響其信噪比以及采集速率的主要因素,分別從電路層面的3個(gè)方面進(jìn)行了相關(guān)優(yōu)化,并利用試驗(yàn)數(shù)據(jù)進(jìn)行了采集系統(tǒng)性能的驗(yàn)證。驗(yàn)證結(jié)果表明,系統(tǒng)信噪比由原有的52 dB提升到了73 dB。最后,本文圍繞當(dāng)前數(shù)據(jù)采集系統(tǒng)的改進(jìn),分別對(duì)上位機(jī)的通信模塊以及數(shù)據(jù)預(yù)處理模式作適配升級(jí)。整體優(yōu)化后的電阻層析測(cè)量系統(tǒng)較原有系統(tǒng)性能得到了顯著提升。