基于虛擬時反測向系統的FPGA課程教學研究與實踐

于智欣

摘要:FPGA設計課程內容復雜且應用靈活,傳統的授課方法使得課程內容變得抽象,不易被學生理解。因此,結合當下最熱門的電子偵察領域,利用一種虛擬時反測向新技術,結合FPGA設計實現一種新的測向系統。該系統的設計采用Xilinx公司FPGA開發板,通過信號的傳輸、控制、處理以及存儲等技術手段,比較全面地學習和探索了FPGA設計的基礎功能。這樣不僅能夠提高學生的學習興趣,同時鍛煉了學生的動手能力,更好地提升了學生對于該課程知識和技術的掌握。

關鍵詞:FPGA;虛擬時反;測向系統;教學研究與實踐

一、前言

FPGA是指現場可編程門陣列(Field Programmable Gate Array,FPGA),其優勢能夠解決定制電路的不足以及克服原有可編程器件門電路數有限的缺點[1]。目前主要以Xilinx和Altera兩家公司的開發板作為主流,它們各自有配套的軟件,其中分別以為Vivado和QuartusII使用最為廣泛,采用的編程語言以VHDL以及Verilog為主,同時配合C語言進行控制。通過FPGA可以進行多通道的設計,這種設計是基于FPGA設計最大的優勢,利用有限資源快速實現所需功能。FPGA設計作為一門實用性強的課程,通過傳統的授課方式進行講解不利于學生的理解,應該搭配前沿技術的系統設計,在實現系統功能的過程中逐步掌握該門課程的核心知識,快速完成本門課程的學習[1]。

時間反轉技術具有自適應聚焦特性,可以考慮將其應用于電磁信號測向領域中,這樣做能夠提高在復雜電磁環境下的測向性能。2004年G.Lerosey等人第一次成功地將時間反轉技術應用到了電磁實驗中。將時間反轉技術引入到輻射源目標探測領域中,通過對其原理的分析可知該技術具有良好的抗干擾性,適用于復雜的電磁環境。同時還對時間反轉理論的具體算法進行了分析和比較,發現其計算簡單、易于硬件工程實現的優勢[2]。

本文以提高系統運算速度、實現測向的實時性為基本要求,利用現有的技術提出一種基于虛擬時反被動DOA估計算法的FPGA并行實現方案,通過該方案的設計與仿真實現,增強學生的主觀能動性,進一步提高該課程的教學質量。首先給出硬件設計方案的原理,然后介紹該算法的硬件并行實現模塊的IP核,最后通過Xilinx公司的Virtex-7信號處理板完成實驗設計與驗證[3]。

二、測向系統的FPGA設計方案

通過天線陣接收一段時長的待測信號,然后利用一個測向系統對信號進行處理,該系統由A/D采集模塊、雙倍速率(Double Data Rate3,DDR3)數據傳遞模塊、虛擬時反被動測向并行算法的FPGA實現模塊以及上位機中能量最大值搜索模塊組成。首先使用AD采集卡采集一段待測的盲信號,通過DMA方式存入DDR3中待用,將與之對應的時延補償點以及下變頻數據由上位機計算完成后,通過PCIE總線協議(Peripheral Component Interconnect Express,PCIE)利用XDMA核將其存入DDR3對應地址中,以上數據都需要存在DDR3的固定地址。通過尋址方式將DDR3的數據利用DMA寫入虛擬時反被動測向的FPGA實現模塊,進行時延補償,使信號波形對齊,把運算結果再通過DMA方式存入DDR3固定地址下,最后通過PCIE上傳至上位機,進行能量最大值搜索,找到的最大能量值所對應的位置即為信源所在方向。數據的采集與傳輸采用文獻中的設計方案,本章重點介紹該系統中虛擬時反被動測向并行算法的FPGA實現模塊的設計[4]。

(一)雙通道數據傳輸原理

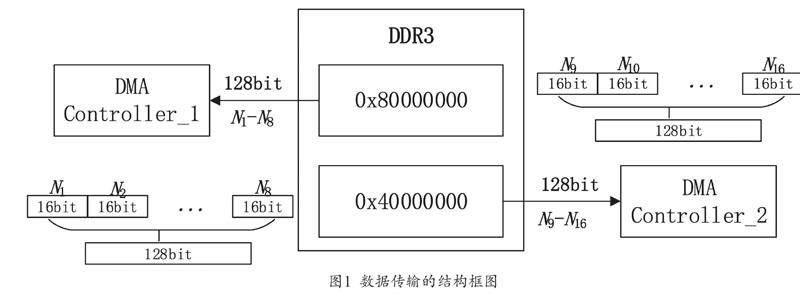

為了實現數據高速移動,且保證數據流不被阻塞,本文提出了一種基于FPGA的雙通道設計方案。兩個通道的數據移動分別由直接存儲器訪問(Direct Memory Access,DMA)控制器實現。在設計中,需要知道數據的基地地址和DDR3的數據量。這種設計不受天線陣陣型的限制,本章以16陣元的陣列進行設計。兩個通道待測信號分別存儲在DDR3的指定區域,數據的基址為0x80000000段和0x40000000段。每個地址單元存儲128bit數據,128bit數據代表8個16bit信號。為了更直觀地展示上述過程,給出了數據傳輸的結構框圖,如圖1所示。圖中N1-N8和N9-N16分別表示天線陣16個陣元接收到的數據。設天線陣有16個陣元,可將該陣列接收的信號分為兩組,即2個8元天線陣進行計算,整個設計分為兩個相同的通道。這兩個通道同時處理8個陣元接收的信號,數據移動方式和信號處理方式相同,但數據存儲的DDR3地址區域不同。由于兩條通道的設計原理是相同的[5],為簡便起見,下面將以一個通道(即8陣元的天線陣)為例進行描述。

(二)搜索域并行處理原理

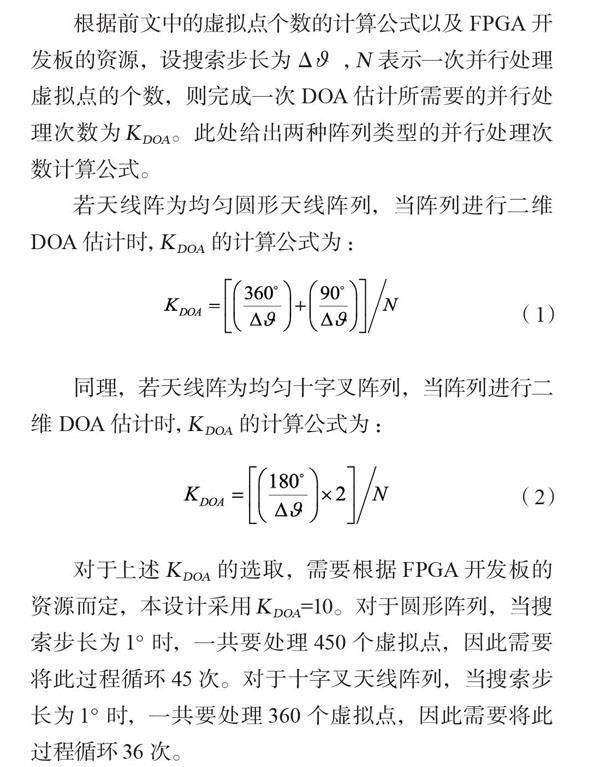

根據前文中的虛擬點個數的計算公式以及FPGA開發板的資源,設搜索步長為Δ? ,N表示一次并行處理虛擬點的個數,則完成一次DOA估計所需要的并行處理次數為KDOA。此處給出兩種陣列類型的并行處理次數計算公式。

若天線陣為均勻圓形天線陣列,當陣列進行二維DOA估計時,KDOA的計算公式為:

同理,若天線陣為均勻十字叉陣列,當陣列進行二維DOA估計時,KDOA的計算公式為:

對于上述KDOA的選取,需要根據FPGA開發板的資源而定,本設計采用KDOA=10。對于圓形陣列,當搜索步長為1°時,一共要處理450個虛擬點,因此需要將此過程循環45次。對于十字叉天線陣列,當搜索步長為1°時,一共要處理360個虛擬點,因此需要將此過程循環36次。

(三)硬件設計原理

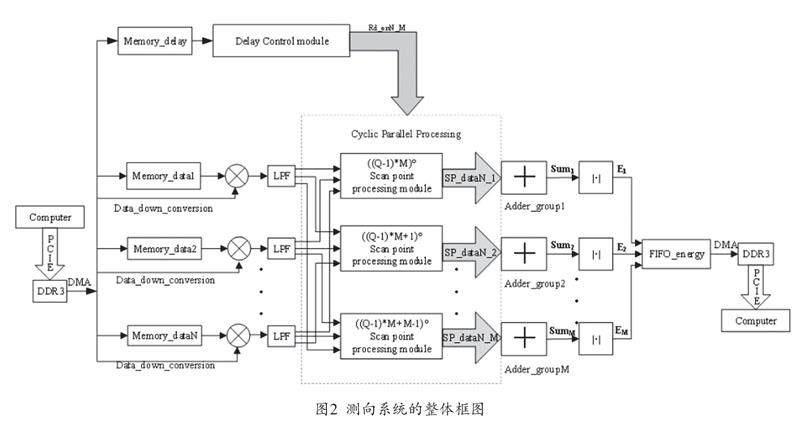

測向系統的整體框圖如圖2所示,本文將待測的信號存入計算機中,并利用計算機計算時延補償點以及下變頻數據,以上數據都通過PCIE方式寫入DDR3的固定地址中。通過DMA方式將DDR3的數據傳輸至FPGA中,并利用尋址方式分別寫入Memory_delay和Memory_data1~ Memory_dataN模塊中。Memory_delay中保存時延補償點,Memory_data1~ Memory_dataN分別保存天線陣1~N陣元的數據。下一步將DDR3中下變頻的數據利用DMA傳輸方式傳出,并與已保存的Memory_data1~ Memory_dataN中的數據做乘法運算,將結果經過低通濾波器(LPF)進行濾波,得到下變頻后的信號。然后將該信號輸入到循環并行處理模塊,該模塊中SP表示全部掃描點數,Q表示第幾次循環,其中Q=1,2,…,SP/M。M表示循環一次能夠處理的掃描點,M的選擇主要與信號處理板的資源有關,并且最好選擇能夠被SP整除的值。令每個掃描點處理模塊都有N路數據,利用控制數據存儲模塊的讀使能將掃描點處的多路信號對齊并輸出,讀使能信號是由Memory_delay中的時延補償點通過Delay Control module將時延點轉換為讀使能信號Rd_enN_M。將第M個模塊輸出的N路數據SP_dataN_M通過加法器組求和并求其能量值。由于資源有限,因此在硬件設計中掃描點能量值運算使用求信號和的絕對值來替代求信號和的平方。將最終求得的掃描點能量值E1~EM都保存在FIFO_energy中,當所有掃描點的能量值全部計算完成后,控制FIFO_energy的讀使能,將數據通過DMA的方式傳輸到DDR3中,最后通過PCIE的方式上傳至計算機中進行最大能量值搜索。

三、實驗分析

一次并行處理的測試點越多,測向實時性越好,但是還要考慮硬件資源的問題,在設計與調試過程中,根據經驗,不應占用全部資源,否則會使測向結果不穩定。

本設計中的算法由Verilog編程語言設計并將其封裝成Custom IP核,如圖3(a)所示,將Custom IP核與DMA控制器、MicroBlaze核和DDR3控制器相連。然后我們利用Vivado軟件的Synthesis and Development以及Generate Bitstream完成系統設計。綜合將高級抽象電路描述轉換為低級描述,實現用于系統布局和布線。在上述兩個進程中未報告任何錯誤時,通過Generate Bitstream函數生成Bitstream文件。最后將生成的比特流文件通過平臺電纜USB下載到FPGA板上,利用MicroBlaze核,通過SDK平臺植入C代碼指令控制整個測向系統,測試結果在上位機顯示。假設天線陣列是一個16陣元均勻分布的圓陣,系統時鐘為200MHz,信號類型為BPSK調制信號。本設計并行處理一次的測試點為10個,則經過布局布線生成比特流后,能夠得到FPGA信號處理板資源利用率如圖3(b)所示,該占用比例不影響測向結果[6]。

以對稱的去中心陣元十字叉天線陣列為例,根據該設計給出16陣元的去中心十字叉天線陣列,需要改變一次測向循環的次數,且預存的數據也按照十字叉天線陣列設計。利用vivado軟件自帶的仿真功能將測試結果進行了記錄,并通過軟件給出了誤差曲線。假設測試點選取的是 ,則測向結果如圖4所示。

四、結語

本文設計一種并行結構實現算法的硬件實現方案,通過Vivado軟件利用Verilog編程語言將該設計封裝成一個IP核,通過SDK平臺與C語言指令來控制數據搬移等功能。最終采用Xilinx公司的FPGA信號處理板完成該設計的驗證,實驗結果表明,該算法在保證較高的測向精度的同時能夠完成系統的實時測向。通過實踐周的方式在兩個班級中進行授課,通過課堂表現以及作業和考核的成績顯示,本次改革從根本上解決了學生對FPGA技術入門難的問題,也提高了教師的教學和科研能力。

參考文獻

[1]楊一峰.硬件輔助驗證產品解讀之FPGA開發板vs原型驗證系統[J].中國集成電路,2022,31(7):27-30+47.

[2]劉博,范玉進,張建軍.基于FPGA的多通道可編程DDC算法研究與實現[J].消費電子,2021(8):21-22.

[3]趙英瀟,蘇陽.基于FPGA的多通道雷達數據回放系統設計[J].電子科技,2023,36(2):1-6+21.

[4]翁天恒,袁永春,周榕,等.基于FPGA的DDR4多通道控制器設計[J].電子測量技術,2022,45(12):148-155.

[5]Jing LY,Zhang NM,He CB,et al.OTFS underwater acoustic communications based on passive time reversal[J].Applied Acoustics,2022,185:108386.

[6]劉海涵,呂衛祥.基于時間反轉變換的動目標相參積累算法[J].現代防御技術,2022,50(2):67-75.

基金項目:1.貴州省教育廳高等學校科學研究項目“基于虛擬時反法的5G精確定位關鍵技術研究”(黔教技〔2022〕263號);2.貴州省教育廳自然科學研究項目(黔教技〔2022〕029號、黔教合KY字[2021]022)