硅襯底氮化鎵大失配應力調控方法研究

王 歡,田 野

(哈爾濱師范大學 物理與電子工程學院,哈爾濱 150025)

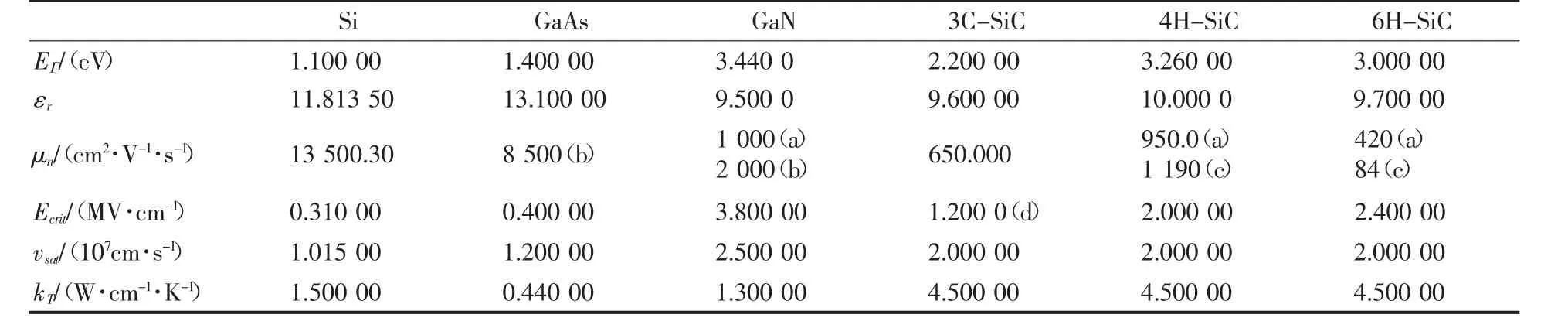

Ⅲ族氮化物,主要包括GaN、AlN、InN 及三元Al-GaN、GaInN、AlIn 和四元AlGaInN 合金材料。表1 為GaN 與其他幾種半導體材料基本性能的比較。由于GaN 和AlGaN 的熱導率較高,而且介電常數較低,適合制作小尺寸低功率中壓至高壓電力電子器件。且AlGaN/GaN 異質結處形成的二維電子氣面密度高達1013cm-2以上,較其他半導體異質結的二維電子氣(2DEG)面密度高近一個數量級,因此很適合制作微波高溫、高功率器件,即用于衛星、空間站及空間太陽能電站耐輻照全光譜太陽能電池器件;此外,GaN 是寬禁帶直接帶隙半導體,又很適合于制作短波長光器件;另外,利用GaN 禁帶寬,與AlN 和InN 形成三元或四元合金帶隙調控范圍超寬(0.7~6.2 eV)的特點,使得GaN適合研制可見光、紫外及近紅外波段光電器件(LED、LD 探測器)。赤崎勇等教授獲得了2014 年的諾貝爾物理學獎,因為研究的GaN 基藍光LED 開啟了人類新的照明市場。顯然,作為第三代半導體材料代表的GaN已經成為當前最具產業開發價值的寬禁帶半導體材料。而高質量、大尺寸GaN 材料的制備也就自然而然地成為了研究GaN 材料的前提和關鍵。

表1 GaN 與其他幾種半導體材料基本性能的比較

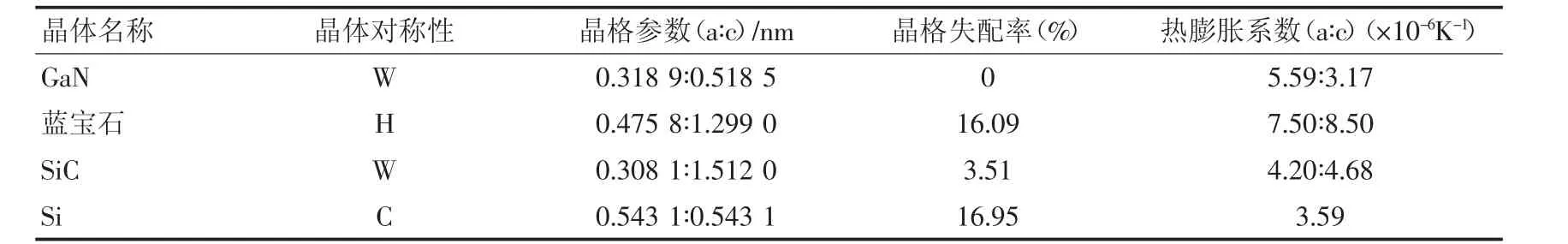

由于GaN 的熔點和飽和蒸汽壓較高,大尺寸的塊體GaN 非常不容易通過傳統的制備技術來獲得。就生長GaN 薄膜來說,GaN 單晶是最理想的襯底材料,其可以在很大程度上降低位錯密度,從而提高外延材料的晶體質量,延長GaN 基器件的工作壽命,提高發光效率。但是大尺寸GaN 單晶襯底制備困難、成品率低,還不能規模化生產,由此造成了大尺寸GaN 單晶襯底材料價格昂貴且稀缺,因而利用同質外延生長GaN 薄膜更加難以實現。所以目前,GaN 的生長主要采用異質外延法,用于異質外延的襯底有藍寶石襯底、碳化硅(SiC)襯底和Si 襯底。表2 為GaN 與常用襯底的各項參數。

表2 GaN 與常用襯底材料的參數

相較于藍寶石襯底和SiC 襯底,Si 襯底具有很多優勢:①Si 襯底的尺寸大且價格低廉(8 英寸Si 襯底僅需要300 元);②導熱導電性能好(可制備垂直結構器件并緩解功率器件散熱問題);③器件工藝成熟(可利用成熟硅微電子器件工藝,成本降幅可達75%)。GaN電子器件和Si(100)互補金屬氧化物半導體(CMOS)電路的集成允許將Si 電路的高度復雜性和靈活性與GaN 支持的大量新設備相結合,如發光二級管(LED)、晶體管(HEMT)、能量收集設備和濾波器等。目前,Si 基GaN 材料被廣泛研制于光電器件(激光器、探測器等)、射頻微波器件(射頻微波器件已開始在5G 無線通訊基站建設中應用)、功率電子器件(功率電子器件已在快充、節能家電及光伏發電逆變器大范圍推廣,并向汽車電子滲透)。

然而,以Si 為襯底異質外延GaN 是典型的大失配外延,需要面臨以下問題:①表面界面能問題。當GaN生長在Si 襯底上時,Si 襯底表面會先氮化形成不利于高密度GaN 成核生長的非晶氮化硅層,而且Si 表面會先與Ga 接觸,Ga 回熔會腐蝕Si 襯底表面,高溫下Si表面分解會高度擴散進入GaN 外延層形成黑色硅斑。②GaN 和Si 之間晶格常數(~17%)失配較大,通常會導致高密度的穿線位錯(TDD,通常為109~1010cm-2)和微裂紋網絡的形成。③GaN 和Si 之間熱膨脹系數的巨大失配(~54%),會使得GaN 從較高的生長溫度(高于100 ℃)降至室溫時,引入巨大的熱應力,從而導致GaN外延層出現裂紋,一般當GaN 外延層的厚度大于1μm時就會發生開裂,嚴重限制了GaN 外延層的厚度,而制作LED 器件所需要的GaN 薄膜厚度通常要高于2μm。以上這些問題的出現嚴重限制了Si 基GaN 光學器件、射頻微波器件和功率電子器件的發展。因此,如何改善Si 襯底上GaN 外延材料的質量,是Si 基GaN 器件研究的重點領域。

通過大量的文獻調研,本文從3 個方面綜述了Si 襯底GaN 大失配應力的調控方法:①緩沖層技術;②圖形化襯底技術;③柔性襯底技術。最后,針對現有方法的優缺點,展望了Si 襯底GaN 大失配應力調控的主要優化方向。

1 緩沖層技術

緩沖層(buffer)技術,是目前解決異質外延體系中應力和缺陷問題應用最廣的一類中間層技術。具有一定厚度的單層或多層結構的緩沖層,主要是通過阻止或抑制外延層中失配應變弛豫的方式來減少乃至消除材料體系中的位錯和缺陷產生。現有的緩沖層可歸納為3 種:晶格匹配緩沖層、組分漸變緩沖層和應變超晶格緩沖層。

1.1 晶格匹配緩沖層

與襯底晶格常數較接近的緩沖層稱為襯底匹配型晶格匹配緩沖層。這一類緩沖層通常適用于失配較小的異質外延體系,由于與襯底的晶格常數更為匹配,可以使襯底表面更加光滑平整,以提高后續的外延層質量。與外延層晶格常數較接近的緩沖層稱為外延層匹配型晶格匹配緩沖層。這一類緩沖層通常適用于失配較大的異質外延體系,比如以Si 為襯底異質外延GaN,雖然與外延層的晶格常數更為匹配,可以為外延層提供更合適的晶格生長模板,但與襯底之間的失配度并不小于外延層與襯底之間的失配度,所以內部依舊有存在缺陷和位錯的可能。但也正是因為這些位錯和缺陷的存在,弛豫掉了一部分失配應變,進而提高了外延層的晶體質量。

2000 年,Krost 通過引入薄的低溫AlN 夾層,在Si襯底獲得了厚度為1.3 μm 的無裂紋GaN。2002 年,R.Armitage 利用分子束外延法(MBE 法)在Si 襯底生長200 nm 厚的HfN(與Si 晶格失配僅為0.02%)緩沖層,隨后在Si(111)面和Si(001)面外延獲得了厚度分別為1.2 μm 和1.0 μm 的無裂紋GaN,且外延薄膜表面幾乎無應力。2011 年,利用多次插入低溫AlN 夾層方法,獲得了總厚度為14.3 μm 的無裂紋GaN 外延層。除此之外,ZnO、3C-SiC 也被用作Si 襯底GaN 異質外延時的緩沖層。

目前,在Si 襯底上生長GaN 應用最廣的是AlN緩沖層,其優勢在于:①AlN 可以阻擋Ga 和Si 的直接接觸,降低了Ga 和Si 反應的可能性;②當AlN 作為緩沖層時,Si 襯底上GaN 的張應力會轉變為壓應力,可以大大減少GaN 外延層的裂紋;③AlN 在Si 襯底表面有較好的浸潤性,很薄的AlN 即可在襯底表面形成連續性很好的展布,說明AlN/Si 的界面比AlN/真空的表面能小,非常適合作Si 襯底外延生長的緩沖層。因此關于AlN 作為緩沖層的研究比較深入,具體包括生長AlN 緩沖層的溫度、預鋪Al 的時間、厚度、TMAl 流量、Ⅴ/Ⅲ比對GaN 外延層的影響。

1.2 組分漸變緩沖層

組分漸變緩沖層是一種多層結構,每一單層的晶格常數可以從與襯底匹配逐漸過渡到與外延層相匹配,即襯底與外延層的晶格失配借以分布到各單層,達到降低或消除失配的目的。

2016 年,徐小青等借助AlN 緩沖層和多層AlxGa1-xN組分漸變緩沖層,在4 英寸Si 襯底上利用MOCVD(金屬有機氣相沉積)生長了1.25 μm 厚的GaN。實驗結果表明:通過優化4 英寸Si 襯底GaN 制備生長溫度和材料生長工藝,并降低AlGaN/GaN 異質結構中的O 和C雜質,將金屬接觸結構由正方形轉變為十字形,HEMT器件的2DEG 遷移率實現了高度均勻性(標準偏差降至0.72%),并提升到了2 161.4 cm2/V/s,超越了生產成本高昂的SiC 襯底GaN HEMT 器件的性能,展現了微波射頻技術的應用潛質。

同年,楊學林等利用MOCVD 在4 英寸p 型Si(111)襯底上外延生長出的AlxGa1-xN/GaN 異質結構,在室溫下2DGE 提高至2 260 cm2/V/s。X 射線衍射(XRD)結果顯示,其表面光滑且帶有清晰的原子臺階,電流-電壓(I-V)測試結果顯示,其上的肖特基二極管顯示出2×10-5A/cm2的超低反向泄漏電流密度和-30 V 的門偏壓,在室溫下的最大電子遷移率可達2 260 cm2/V/s。這表明AlN/AlxGa1-xN可以提高晶體的外延質量,而高質量的無裂紋表面可以顯著改善AlGaN/GaN 異質結構的電學性能。

2019 年,孫錢等借助于精心設計的Al 成分階梯梯度AlN/AlGaN 緩沖層,首次在Si 上獲得了10 μm 厚的無裂紋連續GaN,其TDD 為5.8×107cm-2。外延得到的10 μm 厚GaN 層具有鏡面和無裂紋表面,TDD 約為5.8×107cm-2,與陰極熒光光譜測試(CL)結果一致,此外,生長的GaN 外延層具有原子光滑的表面和清晰的臺階流動形態,在5 μm×5 μm 的面積上顯示出0.21 nm的均方根(RMS)粗糙度。這為在Si 襯底上構建高性能的GaN 器件,如探測器、功率器件甚至激光二極管奠定了基礎。

2020 年,Li Yue 等在4 英寸硅襯底上的制造了準垂直GaN 肖特基勢壘二極管(SBD),I-V 特性曲線顯示,所制備的SBD 在3 V 下具有1.6 kA/cm2的高通態電流密度,在-3 V 下具有10-7A/cm2的低反向電流密度,其通斷電流比高達1010,接近于GaN 襯底上SBD的通斷電流比。表明硅基GaN 上的垂直功率器件有望在低成本領域得到進一步應用。

1.3 應變超晶格緩沖層

在組分漸變緩沖層基礎上發展而來的應變超晶格緩沖層技術,是在襯底上先生長一組單層很薄的應變超晶格層,應變超晶格會引入一個應力場,應力場與穿透位錯相互作用后,能使位錯線被彎曲或拆斷而不能進入外延層中,其作用猶如一個位錯過濾器,可以提高外延層的質量。

2001 年,E.Feltin 通過插入AlN/GaN 超晶格,在Si上生長了0.9~2.5 μm 厚的無裂紋GaN 層。2009 年,Susai Lawrence Selvaraj 利用7 μm 厚AlN/GaN 超晶格,在Si 上制備了2 μm 厚的無裂紋GaN 層。2015 年,Jie Su等通過在AlN/AlGaN 與GaN 之間插入50~100 個周期的AlN/GaN 超晶格,實現了在Si 上生長2 μm 厚的無裂紋GaN 層。

緩沖層技術被用來解決Si 襯底GaN 大失配異質外延體系的核心在于:①先在Si 襯底表面預沉積一層Al 可以解決Si 襯底被氮化以及被Ga 回熔腐蝕的現象,即Al 與NH3先反應形成的AlN 充當了GaN 在Si 襯底上生長過程中阻擋層的作用;②AlxGa1-xN 組分漸變緩沖層作為GaN 在Si 襯底上生長的應力調控層,通過引入壓應力去補償GaN 生長過程中的張應力;③超晶格緩沖層作為GaN 在Si 襯底上生長的缺陷抑制層,可以阻擋位錯向上延伸。通過在Si 襯底上設計合理的緩沖層結構,不僅可以改善GaN 外延層的質量,還可以提高GaN 基器件的性能。

2 圖形化襯底

圖形化襯底技術,是指利用特殊手段(多為刻蝕手段)將襯底材料進行分割,使得一塊襯底材料被分割成具有周期性的小面積圖形結構。襯底的圖形化一般有2 種方式,一種是通過引入SiNx 或SiO2等介質膜,再利用光刻技術獲得介質膜分割線,將襯底分割成周期性的小面積圖形結構。另一種是利用物理或化學刻蝕的方法直接將襯底腐蝕出溝槽分割線,進而在襯底上形成周期性的小面積圖形結構。如圖1 所示。南昌大學江風益教授提出,于介質膜分割線,比較理想的尺寸為寬度5~8 μm,高度0.1~0.3 μm,溝槽分割線的理想尺寸為寬度10 μm 左右,深度15~20 μm。襯底材料被圖形化處理后,外延GaN 薄膜會有選擇性的先在襯底的部分區域進行生長,進而形成各個獨立的GaN 生長板塊,那么GaN 生長過程中的部分熱應力就會在沒有GaN 生長的區域進行釋放,GaN 薄膜的裂紋也隨著減少。另一方面,在圖形化Si 襯底上進行GaN 外延,避免了因GaN 硬度大難以刻蝕的問題,可實現GaN 在MEMS(微機電系統)中的應用。

圖1 圖形Si 襯底示意圖

2018 年,T. Hossian 等對圖形化Si 襯底上厚GaN的裂紋進行了統計并對應力進行分析。研究發現:隨著Si 襯底尺寸的增加,GaN 外延層內裂紋增加,應力也隨之上升;圖形間間隔高度的增加反而降低了GaN 層內的裂紋百分比,從而降低了其中應力;而圖形間間隔的寬度對GaN 層內的裂紋沒有顯著影響。拉曼光譜(Raman)測試結果顯示:對于12 μm 厚的GaN 薄膜,在結構中沒有集中應力的缺陷的情況下,產生裂紋的臨界應力約為1.8 GPa。

在圖形化襯底思想的指導下,研究者們引入了選擇性區域生長技術(SAG)和橫向過外延生長技術(ELO)。

2017 年,Tanaka 等利用SAG 法在Si 上生長了19 μm厚、無裂紋且純的GaN 層。在暴露的底層Si 表面上形成多面六角形盤,能夠在Si 上生長超過18 μm 厚的GaN,并將TDD 密度降低到107cm-2。為了突出厚且無裂紋的低TDD 硅上GaN 的潛力,以19 μm 厚的GaN為漂移層制作了金屬絕緣體半導體場效應晶體管(MISFT),結果表明可以在Si 上制造MISFT,并為在硅CMOS 平臺上集成垂直GaN 功率和光電器件鋪平道路。

圖形化硅襯底生長GaN 薄膜的應力控制主要源于2 個方面:一是通過圖形化生長減小GaN 膜的應變,單元圖形尺寸越小,則張應力降低的幅度越大;二是通過應力補償技術來進一步減小GaN 膜的張應力。圖形化襯底技術對于GaN 基器件十分重要。

3 柔性襯底

柔性襯底技術也稱作可協變中間層技術,是20 世紀90 年代初在緩沖層技術的基礎上發展而來的一類新中間層技術。其指導思想完全不同于傳統的緩沖層,是通過一薄層材料的彈性形變來吸收或釋放體系中的失配應變,從而減少乃至消除界面處或外延層內部位錯和缺陷產生。

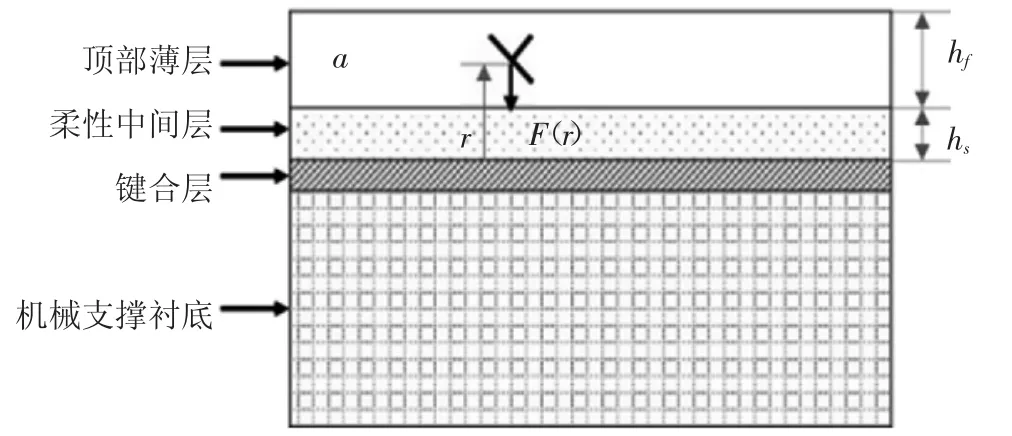

由圖2 可知,氧化物鍵合的SOI 襯底是由“頂層薄Si—SiO2絕緣埋氧層—底層Si”組成的三明治結構Si襯底材料。SOI 襯底的制備工藝相對簡單,是將具有高能量的大量氧離子利用工藝成熟的注氧技術注入到Si基體中,通過控制注入氧離子的劑量可以達到調控鍵和強度的目的。1997 年,J.Cao 提出“滑移理論”,闡釋了SOI 襯底能提高GaN 外延層質量的原因。在大失配外延體系中,外延薄膜最初以三維(3D)島狀的模式生長,然后小島之間合并,逐漸形成連續的二維薄膜,在合并處極易形成會穿透整個外延層的穿透位錯。SOI襯底由于頂層薄Si 的存在,外延層與襯底間的作用力較小,使得外延小島可以在頂層Si 表面自由滑動,可以在某種程度上減少小島在合并過程中所形成的位錯,提高外延GaN 的晶體質量。

圖2 柔性襯底示意圖

2019 年Roy Dagher 等將SOI 襯底圖案化為納米柱,并在其上得到了無裂紋、完全松弛的GaN,位錯密度為4×108cm-2。以納米級柱狀圖案為襯底增強了襯底與外延層間的柔順性,可以更好地釋放位錯,為降低GaN 的應變、TDD 及實現GaN 器件的轉移提供了新的思路。

2020 年,浙江大學宋鈺姿制備了一種降低GaN 外延層熱應力的新結構——SOI 表面懸浮超薄Si 膜。通過有限元方法模擬了新型結構上GaN 層在冷卻過程中的熱應力分布,模擬結果顯示這種新型襯底上GaN有效區域的熱應力可降低44%,進而降低了GaN 中的位錯和裂紋密度,還證實了埋氧層的缺失是導致GaN層熱應力降低的主要因素。

現有的柔性襯底已經在一些典型的失配外延體系中發揮重要作用,尤其是基于SOI 的器件具有集成度高、可靠性好和功能完善等優點,因此SOI 襯底在MEMS中得到廣泛的應用;另一方面,以“滑移理論”為支撐的SOI 襯底可提高GaN 外延層的質量,給予研究者新的靈感——實現柔性層與支撐襯底的弱鍵合或解耦合,可以更大程度上弛豫外延層的應力,降低外延層的位錯密度。

4 結束語

迄今為止,GaN 基器件已經取得了巨大的進步,但是GaN/Si 異質結構的材料質量和電學性質與已經比較成熟的藍寶石、SiC 襯底上異質結構相比,依然存在明顯差距,特別是Si 襯底上GaN 外延片上可見的殘余應力、局域陷阱態及其帶來的材料、器件可靠性問題還相當嚴重,應力和缺陷控制問題尚沒有根本解決。如何研究制備出更高質量的Si 襯底上GaN 基異質結構,依然是當前該領域高度關注的核心問題之一。Si 襯底上GaN 材料大失配外延制備技術仍處于發展中。在解決Si 襯底GaN 異質外延大失配體系中存在的問題時,緩沖層技術操作復雜,工藝繁瑣,未消除的殘余應力在下一步外延中還會引入新的位錯;圖形化襯底技術的制備過程存在著步驟復雜、對設備要求高、價格高昂和大面積圖案化制備的成功率低等問題;柔性襯底技術在實現柔性層與支撐襯底的弱鍵合或解耦合過程中還存在一些不足和技術局限性,并且高品質的SOI 襯底價格并不便宜,要達到廣泛應用和推廣,還需不斷地發展,并解決現存的技術問題。

未來在解決Si 襯底GaN 異質外延大失配應力的相關問題,一方面將借鑒以藍寶石、SiC 等為襯底異質外延GaN 的成熟工藝,另一方面,襯底與外延層之間的弱鍵合將成為解決大失配體系中應力問題的重要手段。隨著Si 基GaN 無裂紋厚度的增加以及位錯密度的降低,Si 基GaN 會突破以藍寶石為襯底外延GaN 在尺寸和成本上的限制,Si 基GaN 晶圓在LED 市場的份額會逐年增加,Si 基GaN 晶圓質量會更加符合嚴格的CMOS 工藝標準;Si 襯底GaN 材料研制的HEMT 微波射頻器件的性能可以達到甚至超過SiC 上GaN HEMT微波射頻器件性能;實現Si 襯底GaN 功率電子器件對傳統中低壓硅基功率電子器件的替代。