實用計數器的VHDL與Verilog HDL行為建模對比研究

2022-10-15 15:54:18楊云海章芬芬

現代信息科技

2022年15期

楊云海,章芬芬

(韶關學院 信息工程學院,廣東 韶關 512005)

0 引 言

硬件描述語言(以下簡稱為HDL)在電子設計自動化(以下簡稱EDA)過程中,可以用于數字電路的建模和仿真。計數器是一種常用的數字電路模塊,在設計的過程經常會被設計、調用。使用目前最為常用的兩種HDL(即VHDL與Verilog HDL)對實用計數器進行行為建模,并對比兩種語言的建模結果,對實用數字電路的設計有一定的指導作用,有一定的研究意義。

1 實用計數器功能規劃

考慮到計數器模塊的實用性,能更方便地引入到更高層級的設計中,計數器模塊的控制接口要比較豐富。除了要有時鐘(clk)輸入以外,還要包含的控制信號有:異步清零(rst)、時鐘使能(en)、同步裝載(ld),等等;需要留有4位的裝載數據輸入端口(din);需要安排4位的計數輸出端口(dout)和1位的進位(計滿)輸出端口(cout)。

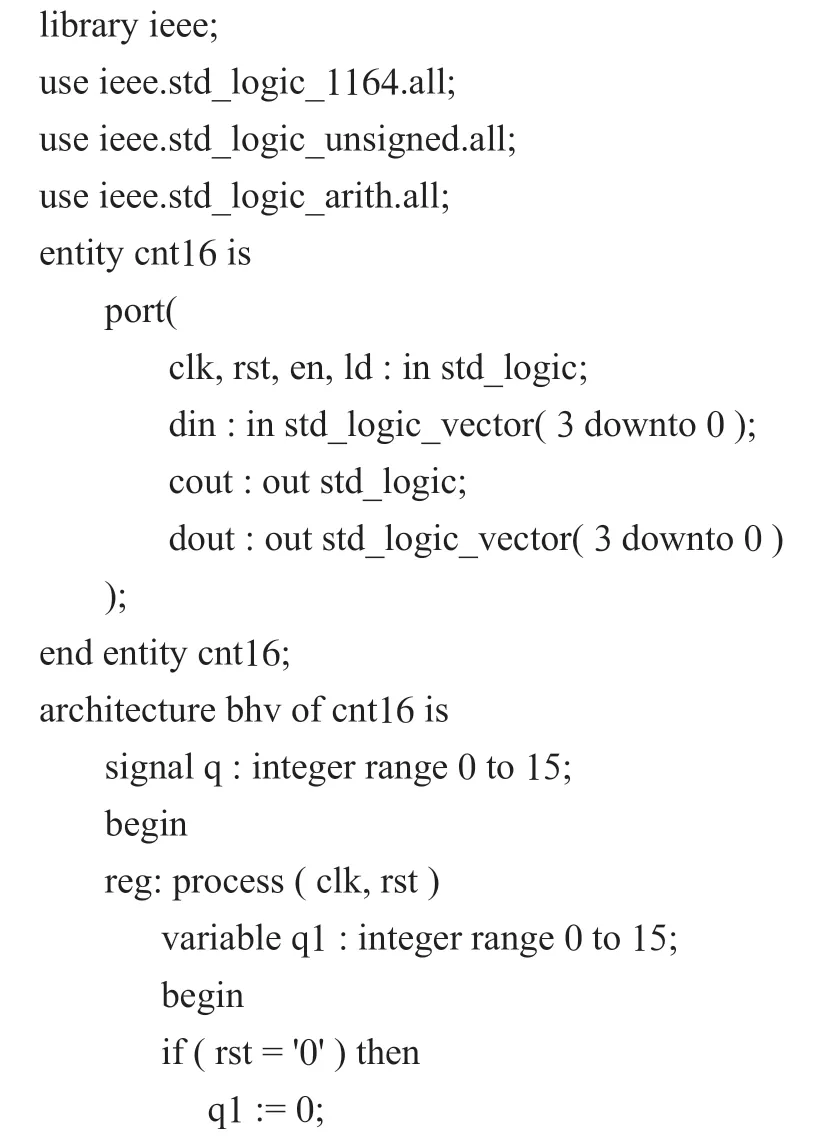

2 實用計數器的VHDL行為建模

按照功能規劃,使用VHDL行為描述語句對電路進行建模。電路模型的VHDL代碼如下:

在程序中,由于需要使用了標準邏輯矢量(STD_LOGIC_VECTOR)與整形數據的加法操作,對“+”運算符進行了重載,并且使用了數據類型轉換函數,在整形與標準邏輯矢量之間進行數據類型轉換。因此,需要打開IEEE庫中相應的包。

在結構體中定義了一個“q”信號,在“reg”進程中定義了一個“q1”變量。其中,“q1”變量用于暫存計數的結果,“q”信號用于把“q1”的計數結果傳遞出進程以外。這樣的設置,層次分明,結構清晰,提高了代碼的可讀性,為以后對模塊的修改提供了方便。

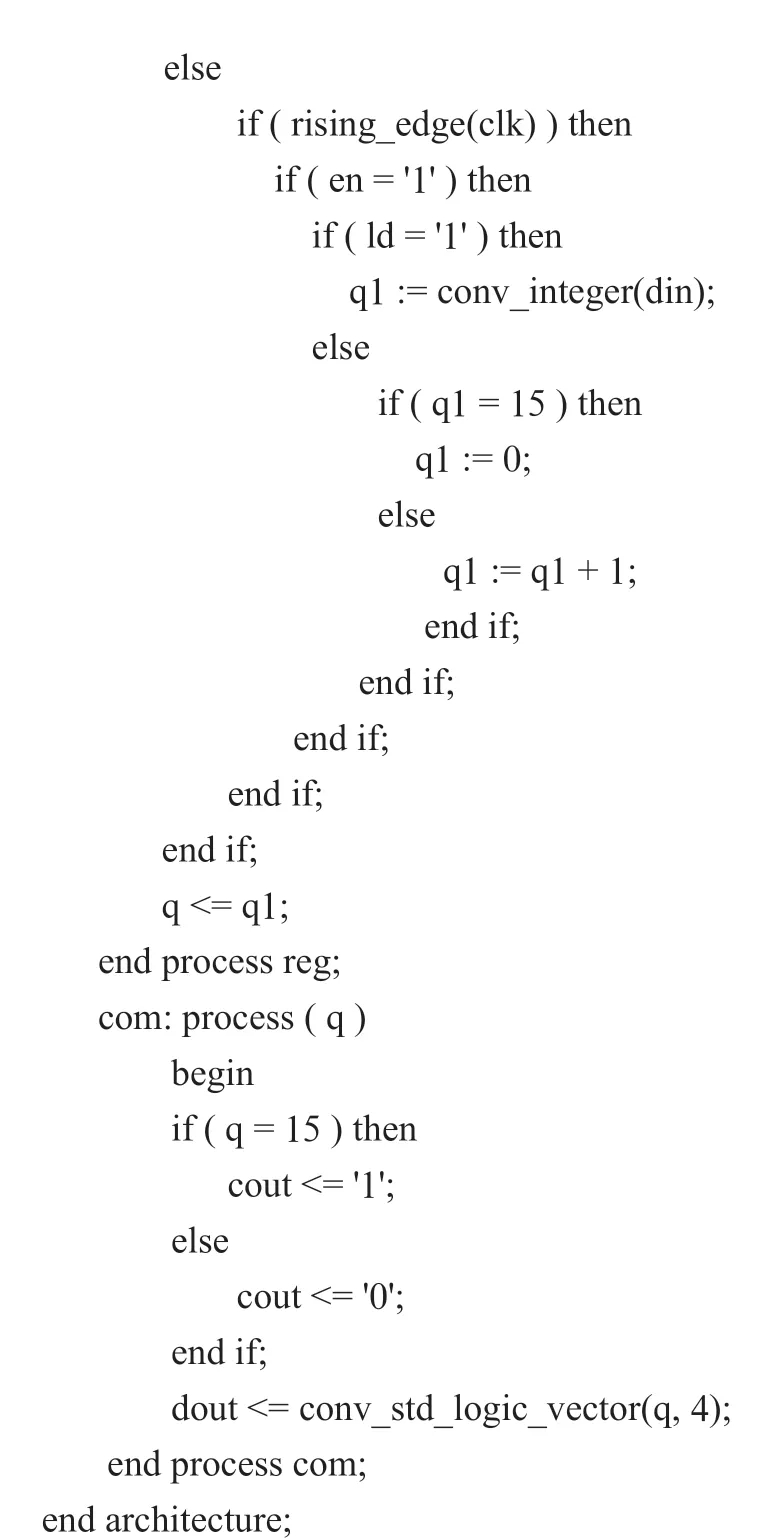

在代碼中,使用了2個進程(Process)表達電路的行為,進程的標號分別為:“reg”和“com”。……

登錄APP查看全文

猜你喜歡

中華詩詞(2022年6期)2022-12-31 06:41:24

現代裝飾(2020年7期)2020-07-27 01:27:42

流行色(2020年1期)2020-04-28 11:16:38

藝術啟蒙(2018年7期)2018-08-23 09:14:18

海峽姐妹(2017年7期)2017-07-31 19:08:17

中國科技論壇(2017年7期)2017-07-25 08:49:53

Coco薇(2017年5期)2017-06-05 08:53:16

媽媽寶寶(2017年2期)2017-02-21 01:21:24

國際漢語學報(2016年1期)2017-01-20 08:21:20

中國中醫藥現代遠程教育(2014年22期)2014-03-01 04:32:55