應用于模擬開關芯片的過壓保護電路設計*

張 林, 李婕妤,汪 洋, 金湘亮,2

(1.湘潭大學 物理與光電工程學院, 湖南 湘潭 411105; 2.湖南師范大學 物理與電子科學學院,湖南 長沙 410081)

0 引 言

模擬開關利用了金屬氧化物半導體(MOS)晶體管的導通和斷開特性,MOS晶體管能夠實現很低的導通電阻,也能在關斷時具有大的關斷阻抗。經過適當的設計,控制模擬開關的導通和關閉,實現電路的信號切換的作用。模擬開關由于其高性能和低功耗的特點而被廣泛用于數據通信、網絡、便攜式通信和消費電子設備。

近年來,由于模擬開關可以直接驅動多個揚聲器,因此對模擬開關的需求一直在增加[1]。通過使用模擬開關和零電壓偏置音頻放大器,多個揚聲器可以共享一個信號源,或者可以將多個信號源傳輸到單個揚聲器。而且,模擬開關可以顯著降低與音頻信號布線相關的噪音[2],并且可以大大降低信號的功耗。模擬開關是電子產品開發的重要方向。

現在的模擬開關主要由振蕩器、分頻器、負電壓源產生電路、過壓保護電路、電荷泵、輸入驅動電路組成[3]。振蕩器電路產生振蕩波形,經過分頻器得到穩定的波形;振蕩波形經過鎖存器得到負電壓源,整體電路可以傳輸負信號;輸入控制信號經過輸入驅動電路處理,控制電荷泵的升壓工作;電荷泵電路提升開關MOS晶體管的柵壓,高速傳輸信號,控制信號的傳輸;過壓保護電路檢測端口電壓情況,對電路實行過壓保護。

對于模擬開關而言,其傳輸的信號速度快,電壓變化>大。端口電壓變化的過大較快的情況下,容易對整體電路造成損傷,造成整體芯片的毀壞。所以,過壓保護電路對整體電路的防護有著重要意義,它保護著整體電路不受高壓損壞[4]。傳統的過壓保護電路是使用單獨的片外裝置實現的,不僅存在線路復雜,而且占較大的面積。因此,芯片的集成化是非常占優勢的[5]。

一般的過壓保護電路采用電阻分壓的形式,存在許多的缺點。即大的電流流過電阻,造成大的功耗[6]。而且,過壓閾值和恢復電壓閾值很接近,不適于端口的復雜電壓變化,容易毀壞芯片[7]。

針對上述問題,本文設計的過壓保護電路,具有低功耗和遲滯電壓的特點。設計的過壓保護有閾值電壓,對變化的電壓辨別后才開啟主體電路[8],同時,開啟時間和恢復時間較短,能夠快速反應過大的輸入電壓,也能在輸入電壓正常后快速恢復整體電路的運行。

1 電路的結構與設計原理

1.1 電路結構

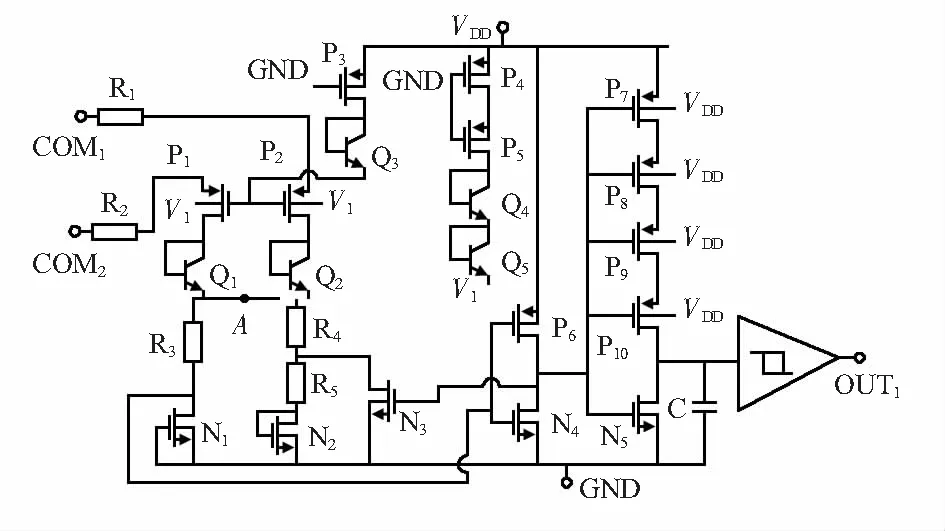

如圖1所示,設計的過壓保護電路。采用P溝道 MOS(PMOS)晶體管接收COM端的電壓,電壓轉換為電流,減少信號在傳輸過程中的損失。輸入端電壓過大后,P1,P2工作在飽和區,A點電壓提升,輸出OUT1為低電平。通過A點電壓的跳變,控制N4,P6組成的反相器的輸出,從而控制OUT1輸出保護或恢復信號。

圖1 過壓保護電路

電路設計了雙級遲滯電路,R3,R4,R5,N1,N2,N3組成第一級遲滯電路,第二級遲滯電路由RC延遲和遲滯比較器組成。

1.2 過壓保護設計原理

采用0.18 μm BCD工藝,PSub為工藝襯底。P1和P2共同的阱電位V1,V1通過Q5,Q4,P5,P4連接到VDD,當電路工作時,VDD將V1充電到接近VDD的電壓。忽略溝道調制效應,流過P1或P2的電流為

(1)

如果COM1或COM2的電壓過大,那么P1或P2的VGS將過大,造成流過的電流I過大。N1漏端的電壓變大,造成N3關閉,輸出OUT1為低電位。假設還未進行過壓保護,N3即將離開飽和區,流過N3漏端的電流為

(2)

A點的電壓經過電阻R3到N1的漏端,A點的電壓等于N1漏端的電壓,A點的電壓VA為

(3)

隨著COM端口電壓變大,電流I將變大,A點電壓上升。當電流I足夠大時,將能夠翻轉由P6,N4組成反相器的輸出電壓,這時反相器輸出為低電平,N3關斷,流過R4的電流將流向R5,N2。A點的電位將不斷提升,N3關斷更徹底,輸出OUT1為低電位。

COM端的電壓過壓后,N3是關斷的,流過R4的電流為I。那么,A點電位為

(4)

可以知道,輸入端COM電壓大于VP,H時,輸出OUT1為低電位。那么,VP,H為

(5)

其中,VCOM1-A的值為

VCOM-A=IR1+Vds,PMOS+VBEQ+I(R4+R5)

(6)

同理,COM端的電壓由過壓開始變小,流過的電流I變小,造成N3導通,輸出OUT1為高電平。輸入端COM電壓低于VP,L時,輸出OUT1為高電位,公式為

(7)

遲滯電壓范圍ΔVP為

(8)

可以知道,增加電路遲滯電壓范圍方法有幾種。適當增加R5電阻值、增加N3的寬長比或者減小N2的寬長比,提高過壓保護電路的抗干擾能力。

為了進一步防止外部電壓脈沖對電路的傷害,避免電路反復開啟,需要對第一級檢測電路的輸出做一個延遲判斷。在實際的應用中,輸入端口可能會有電壓脈沖,而第一級的檢測電路的輸出會受到干擾,對電路產生不利影響。采用一個RC延遲和一個施密特觸發器對N5漏端電壓檢測,作為第二級抗干擾信號的電路。

RC延遲是采用4個PMOS晶體管串聯到電容端,這4個PMOS相當于一個電阻R。電源電壓通過電阻對電容充電,電容的充電時間可以有效增大。對于RC延遲環節有

VC(t)|t=0=0

(9)

Ri(t)+VC(t)=VDDu(t)

(10)

列寫出微分方程

(11)

各項取拉氏變換,可以得到

RCsVC(s)+VC(s)=VDD/s

(12)

再轉換成時域函數,可以得到

(13)

可知,電容充電逐漸接近電源電壓VDD,適當大的電阻R和電容C能有效減緩充電速度。

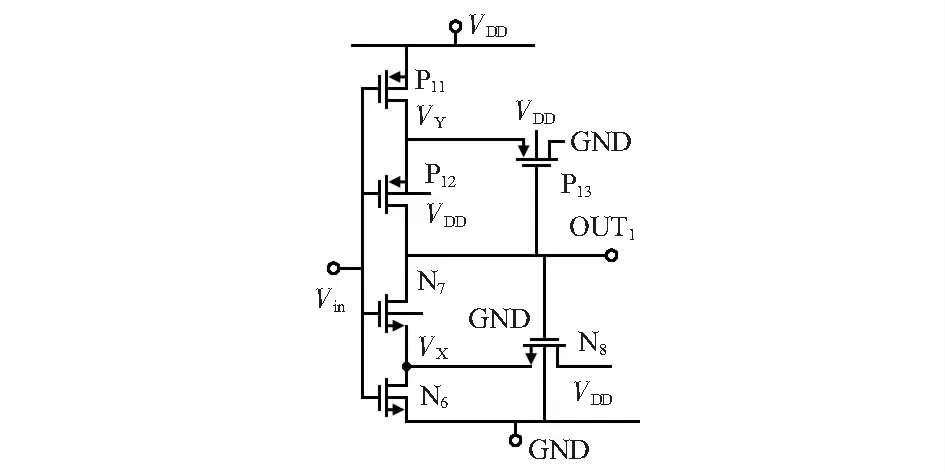

如圖2所示,設計了遲滯比較器電路。當N7開始導通后,輸出VOUT1開始下降,進一步關斷N8,從而降低VX電位。這又進一步增加N7管的導通程度。N7未導通時,根據流過N6,N8的電流相等的情況

(14)

設N6管和N8管寬長比為m1,即m1=β6/β8。聯立式上面兩式可得VH值

(15)

當電路實行過壓保護后,輸入端電壓恢復正常。那么,有一個的閾值電壓VL使電路恢復正常工作。令m2=β13/β11,同理,在PMOS晶體管的作用下,可以得

(16)

當m1,m2趨于無窮大時,ΔV趨近于(VDD-|Vthp|)-Vthn,m1,m2趨于無窮小時,ΔV趨近于VDD。所以,應適當讓β6小于β8,β11小于β13,提高電路的遲滯范圍,減少錯誤電壓給整體電路帶來的危害。

圖2 遲滯比較器電路

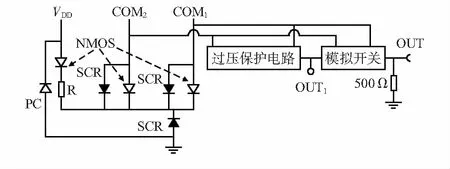

1.3 靜電防護設計

芯片在生產和使用過程中,不可避免地接觸靜電[9]。MOS晶體管的PN結耐壓有限,柵極的柵氧厚度有限。電壓過大后,容易造成柵氧擊穿和PN結擊穿。所以,必須增加器件的可靠性,添加靜電防護器件(ESD)[10]。

ESD的設計主要考慮4種放電模式,即PD模式(端口到電源)、PS模式(端口到地)、NS模式(地到端口)、ND(電源到端口)。根據PN結的正偏特性和反偏特性,確定導通電壓大小,正偏電壓大致取值0.7 V,反偏電壓根據工藝確定。另外,還要考慮的是電源到地、地到電源的放電,也要分析其導通電壓大小。根據放電路徑上的電壓大小,確定設計ESD的觸發電壓和維持電壓范圍。

如圖3所示,設計ESD電路防護網絡。因為模擬開關需要傳輸負信號,端口到地應做雙向ESD防護。端口的防護,采用單向的NMOS晶體管和SCR并聯導電,再通過一個公共的SCR到地[11]。該設計能增加靜電釋放的速度和大小,也能節省布圖面積。電路路徑耐擊穿電壓還與層次之間的距離有關。如果設計的ESD觸發電壓和維持電壓較高,那么可以考慮版圖上增大柵與源、柵與漏的距離,從而增大耐擊穿電壓。

圖3 靜電保護的設計

2 結果與分析

2.1 仿真結果

基于0.18 μm BCD工藝,使用Cadence軟件搭建電路,對過壓保護電路進行仿真。電源電壓為3.3 V,仿真得到的靜態電源電流200 pA左右,實現了低功耗的設計。除此之外,還對過壓保護電路的開啟時間、關斷時間和閾值電壓的性能進行仿真。

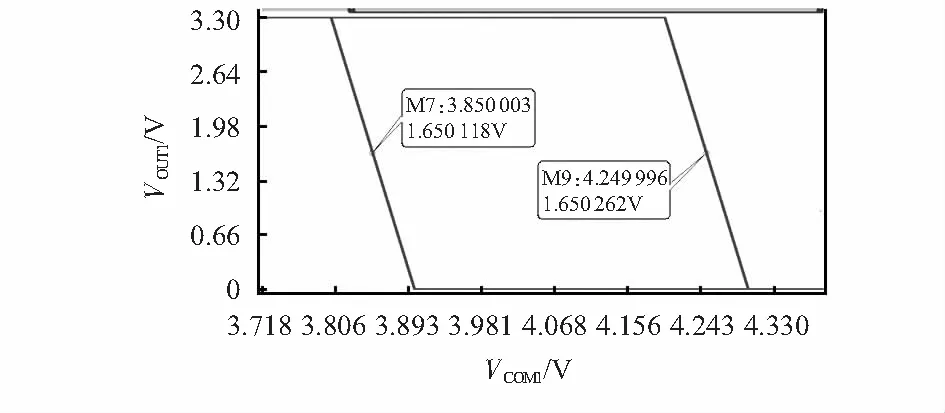

過壓保護電路的閾值電壓決定著輸出電壓的翻轉點,能有效抵抗干擾信號。如圖4所示,電源電壓為3.3 V,對過壓保護電路的閾值電壓仿真。可以看出,過壓保護電路的閾值電壓是4.25 V和3.85 V。COM1端口電壓VCOM1增大到4.25 V,輸出電壓VOUT1會跳變為0,輸出保護信號,實行過壓保護。COM1端口電壓VCOM1從過壓減小到3.85 V,輸出電壓VOUT1會跳變為VDD,開啟模擬開關電路。

圖4 過壓保護電路閾值電壓仿真

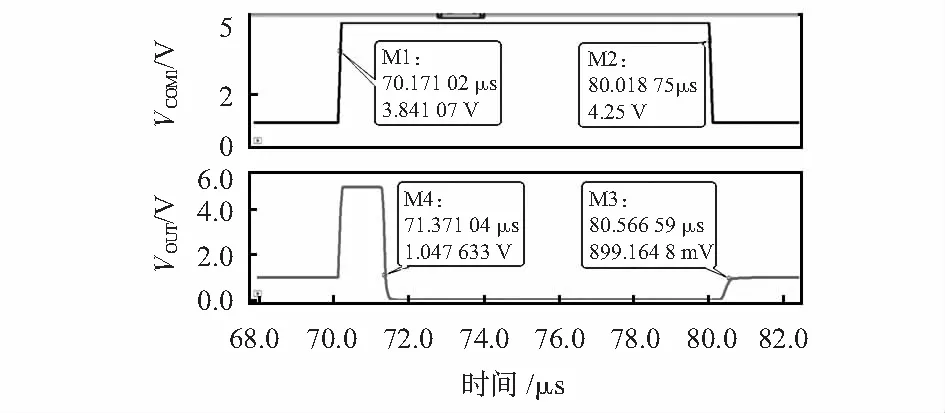

過壓保護電路的輸入、輸出瞬態圖如圖5所示,VCOM1是輸入信號,VOUT1是輸出信號。過壓保護反應時間是應對過大電壓的反應時間tFP,反映著電路過壓保護速度。經過Cadence軟件仿真,得到tFP為1.0 μs。過壓保護恢復時間tFPR是電路恢復正常的時間,經過仿真,可以看出,tFPR為0.035 μs。

圖5 過壓保護電路的輸入、輸出瞬態仿真

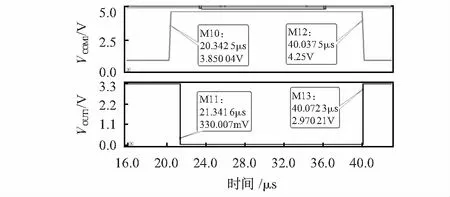

過壓保護電路對模擬開關保護仿真,如圖6所示,過壓保護電路影響模擬開關的作用。過壓保護電路對模擬開關起著保護的作用,VCOM1為輸入信號,VOUT為輸出信號。當COM1端口電壓過高時,過壓保護電路輸出低電平,關斷模擬開關。當COM1端口電壓恢復時,過壓保護電路輸出高電平,模擬開關正常工作,COM1端的信號傳輸到輸出端口。經過仿真,可知tFP為1.20 μs,tFPR為0.55 μs。

圖6 過壓保護電路對模擬開關保護仿真

模擬開關電路中存在著自身的電路結構,會對過壓保護電路有一定的延遲,所以,過壓反應時間和恢復時間會有些偏大。經過過壓保護電路的作用,模擬開關能夠實現過壓保護的功能。

2.2 測試結果與分析

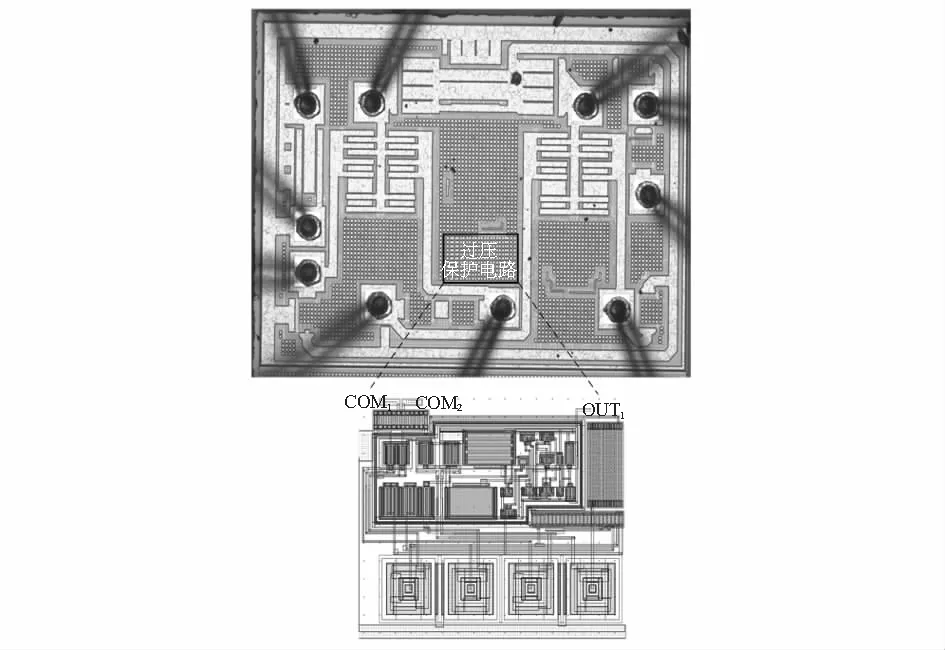

基于0.18 μm BCD工藝,采用3層金屬繪制版圖,并經過流片驗證。版圖的布局、布線,一是確保電路的性能和可靠性,二是合理布局并減小面積[12]。如圖7所示,過壓保護電路的版圖面積為102 μm×85 μm。

圖7 全芯片鏡像顯微圖和過壓保護電路版圖

如表1所示,列出了測試過壓保護電路對模擬開關實際作用的值。測試結果與仿真結果基本一致,沒有超出設定的應用要求。測試的結果有些偏大,原因可能是實際電路封裝中存在著大的電阻值和大電容值,或者是電源不穩定。設計的過壓保護電路符合應用的要求,達到了預計的效果。

表1 測試結果(25 ℃)

3 結 論

基于0.18 μm BCD工藝,本文設計了一種能應用在模擬開關中的過壓保護電路,采用雙級遲滯電路和延遲電路設計,能抗信號干擾。經過測試,該過壓保護電路對模擬開關的開啟閾值電壓為4.54 V,恢復閾值電壓4.12 V。開啟時間為2.80 μs,恢復時間為1.84 μs。設計的過壓保護電路具有抗干擾能力,較快的開啟和恢復,能很好地應用在模擬開關的領域。