一種非易失性可重構場效應晶體管研究

連丹純,劉 溪

(沈陽工業大學信息科學與工程學院,沈陽 110870)

1 引言

極性可控場效應晶體管,或稱可重構場效應晶體管(RFET),作為一個單一設備,可通過在操作期間重置施加在程序門上的電壓來靈活配置為N型或P型FET[1-3]。RFET以這一功能特點,在可編程邏輯陣列中發揮著獨特的優勢,使用比傳統CMOS技術更少的晶體管實現各種邏輯門[4-8]。然而,額外的編程門從本質上增加了金屬互連的難度,與單柵結構相比,當器件處于關閉狀態或反向偏置狀態時,始終在高壓水平下工作的程序門引起的局部電場增強也會增強頻帶彎曲,導致隧穿效應,增加功耗。這種效應對于高度集成的RFET尤其顯著。當編程門和控制門應用于極性相反的電壓時,這兩個門之間區域的隧穿效應將顯著增強。針對這一問題,在此提出一種非易失性浮動可編程門可重構場效應晶體管(FPG-RFET)。

2 器件結構

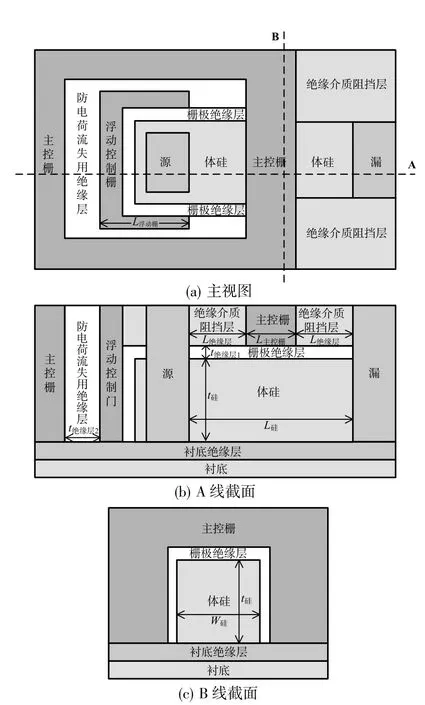

與傳統的RFET不同,FPG-RFET引入了非易失性電荷存儲層作為浮動程序門,而不是需要獨立電源的程序門,在浮動程序門中存儲的電荷可以通過控制門進行編程,所以本質上只需要一個獨立供電的門即可完成可重構操作。此外,控制門可以調節浮動編程門中的等效電壓,有效地降低靜態功耗和逆漏電流的產生。新設計器件結構如圖1所示。

圖1 新設計FPG-RFET結構圖

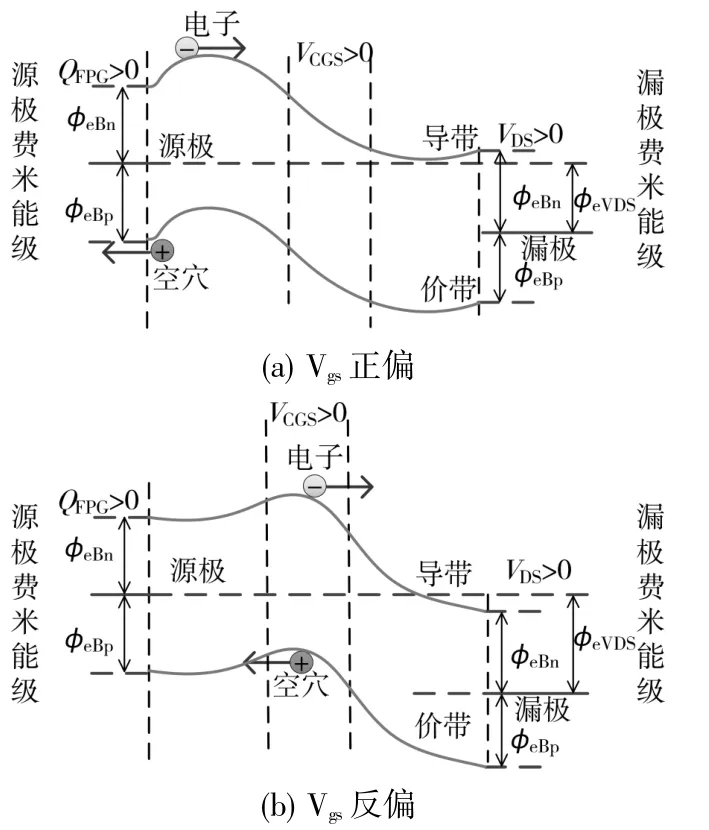

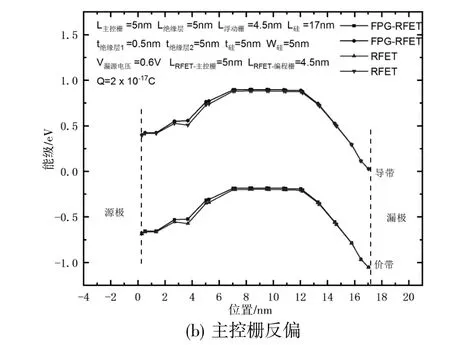

可見,所設計器件為平面溝道。以N型為例,源/漏極與硅界面形成具有肖特基接觸的阻擋結。采用金屬結在源漏區處形成肖特基勢壘,同時引入非易失性電荷存儲層作為浮柵控制門。當控制門寫入電荷被設置在特定值,即可調節器件的導通類型。以N型為例,新設計器件能帶分布情況如圖2所示。

圖2 新設計器件能帶圖

當非易失性電荷存儲層被寫入正電荷時,開關裝置工作在N模式。當柵電極處于正偏,如圖2(a),寫入正電荷的非易失性電荷存儲層和柵電極均對半導體隧穿層的隧道效應有所加強,因此可以產生較大的正向導通電流。電子空穴對主要由源區的帶帶隧穿產生。空穴流向源極,導帶電子可以容易地流向漏極,對于電子從源極到漏極沒有形成勢壘。

當柵電極處于反偏時,如圖2(b),寫入正電荷的非易失性電荷存儲層和柵電極對半導體隧穿層所產生的隧道效應會抵消掉一部分,使得此時產生的反向泄露電流遠小于正向導通電流,實現開關裝置的低反向漏電特性。電子空穴對主要由漏區帶帶隧穿產生,電子流向漏極。加入正電荷的浮動控制門會對空穴形成一個潛在的勢壘,能夠有效地阻止空穴從漏極流向源極,大量漏電流因此受到阻止[9]。

3 與傳統RFET性能比較

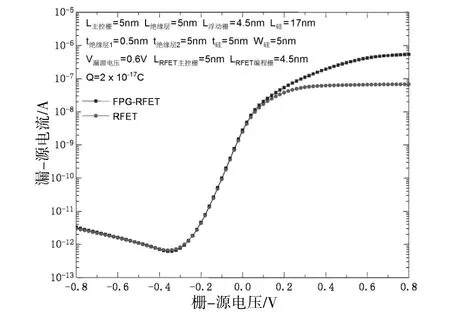

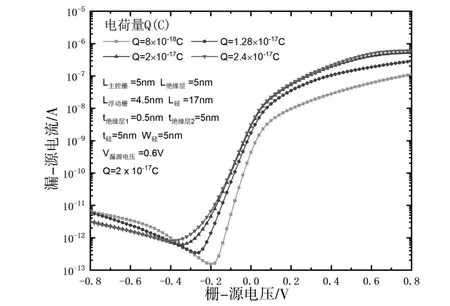

通過Silvaco Tools器件模擬來驗證所提FPGRFET與相同尺寸下傳統RFET的性能對比。如圖3所示為兩者傳輸特性曲線的對比結果。可見,兩者的反向電流基本一致,而FPG-RFET具有較高的正向電流,幾乎高出一個數量級。

圖3 兩種器件轉移特性對比

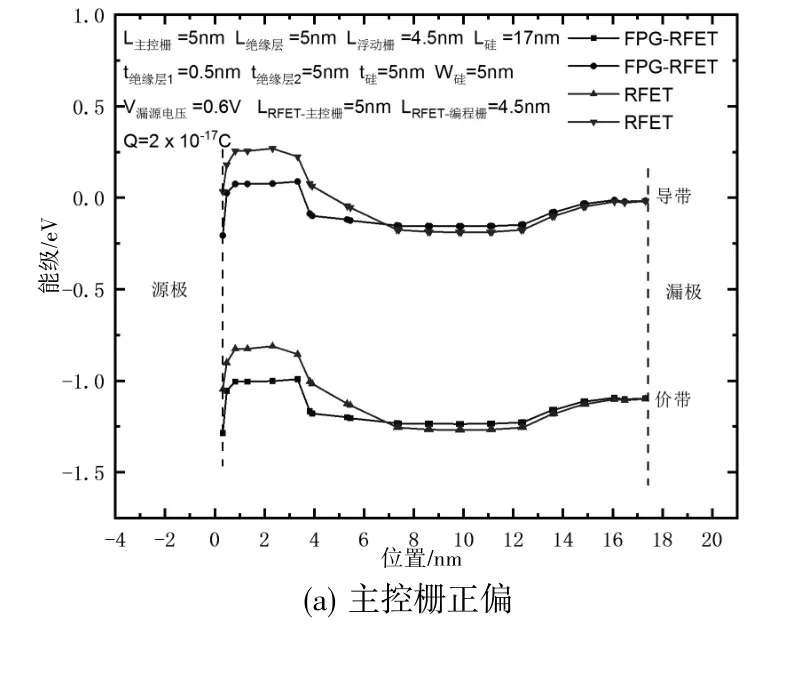

兩者能帶圖對比結果如圖4所示。

圖4 兩種器件能帶圖對比

可見,正偏條件下,FPG-RFET從源到漏的能帶彎曲比傳統RFET更平滑,故而可以擁有更高的正向電流。反偏條件下,兩者能帶圖基本一致,此證明二者在反向漏電流上具有同等的性能。

4 電荷數量對轉移特性的影響

向浮柵中加入不同電荷數量,相應的轉移特性曲線會顯示出明顯差異,如圖5所示。

圖5 浮柵中電荷數量對轉移特性曲線的影響

轉移特性曲線可分為三個工作狀態區:正向導通區、靜態工作區、反向漏電區。改變電荷數量對正向導通區的影響較為明顯,正向電流隨電荷量的增加而增加;反向漏電區所受的影響不太明顯,反向漏電流隨電荷的增加而降低,但其變化幅度較正向電流而言要小很多;在靜態工作區也有明顯影響,靜態工作區電流隨電荷量增大而增大,但同時也伴隨著亞閾值擺幅的增大。綜合來看,電荷量并不是越多越好,而是存在一個理想值。

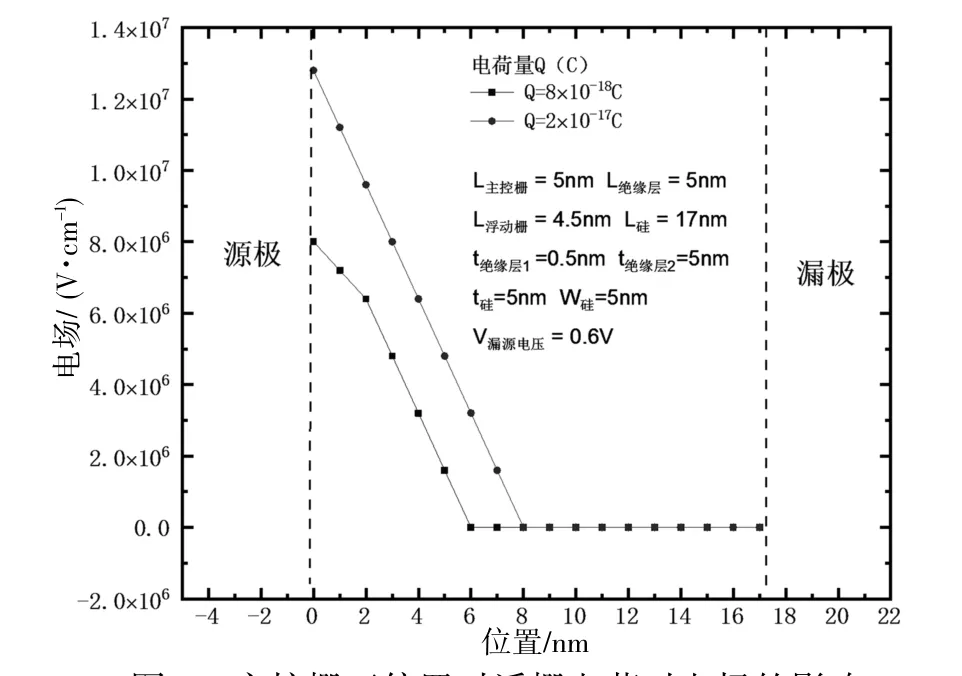

此處以主控柵處于正向偏置和零偏置兩種情況為例,討論應當加入多少電荷量最為合適。當主控柵電極處于正向偏置時,向FPG-RFET的非易失性電荷存儲層中加入不同電荷量,所引起的電場強度變化情況如圖6所示。兩個柵極之間的本征區域受到外加電壓,將導致能帶彎曲,產生帶帶隧穿效應。在圖中可以看出,隨著電荷量的增加,FPGRFET的主控柵和浮動控制門之間靠近漏極的本征區域的電場強度明顯增強了,在該區域,電場強度大的地方能帶彎折程度更大,隧穿距離更小,隧穿幾率更大,從而產生了更強的帶帶隧穿效應,最終形成更大的正向隧穿電流。

圖6 主控柵正偏置時浮柵電荷對電場的影響

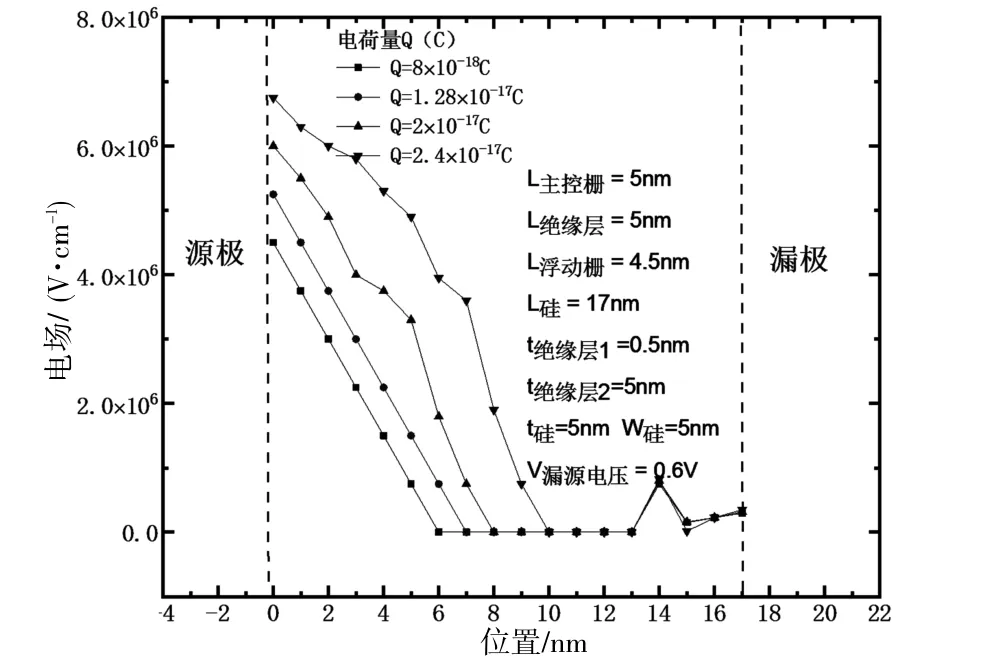

當主控柵電極處于零偏電壓下,FPG-RFET浮柵中不同電荷量引起電場強度變化如圖7所示。同樣,可以看出,隨著電荷量的增加,FPG-RFET的主控柵和浮動控制門之間靠近漏極的本征區域的電場強度也是增強的,出于與正偏條件完全相同的原因,最終也形成了較大的隧穿電流,由此提高了靜態工作點,改變了亞閾值擺幅。

圖7 主控柵零偏置時浮柵電荷對電場的影響

至此,針對上述兩種情況,綜合來看,可得到一個理想的電荷值。在此實例中,此數值大約為2.4×10-17C。

5 結束語

所提出的這一新穎的FPG-RFET,是通過向非易失性電荷存儲層寫入電荷及改變柵電極電壓來實現對肖特基勢壘隧道效應強弱的控制的;改變半導體隧穿層與電極內嵌區之間的阻值,便可控制開關電流的大小。與傳統的RFET相比,該設計具有低靜態功耗和低反向泄露電流,對器件導通、關斷和導電類型重置的控制也極為簡便。本設計延伸了集成電路設計單元的邏輯功能,提供了更好的工作特性,有一定的推廣應用價值。