基于BIT 設(shè)計的電子設(shè)備驗證平臺

靳為東,趙杰,申雙榮

(中電科思儀科技股份有限公司,山東青島,266555)

0 引言

隨著電子設(shè)備信息化與數(shù)字化的快速發(fā)展,結(jié)構(gòu)也變得高度集成化和復(fù)雜化,電子設(shè)備的BIT 設(shè)計與其功能設(shè)計存在脫節(jié)和缺乏規(guī)范性,使得BIT 功能電路本身成為了電子設(shè)備中的一個不可控風(fēng)險。在BIT 設(shè)計時電子設(shè)備的設(shè)計已經(jīng)定型,無法對電子設(shè)備功能、結(jié)構(gòu)、體積等相關(guān)設(shè)計進行更改,盡管在電子設(shè)備BIT 設(shè)計時有考慮可測性設(shè)計,但是由于設(shè)備本身的設(shè)計已經(jīng)定型,無法進行根本的更改,使得電子設(shè)備的BIT 的引入和電子設(shè)備本身功能及指標(biāo)的保證之間形成了一種不可調(diào)和的矛盾。電子設(shè)備內(nèi)部的高度集成和測算總線資源的有限都給電子設(shè)備的性能測試、綜合診斷、健康管理和現(xiàn)場維修檢測都帶來了挑戰(zhàn),因此針對電子設(shè)備系統(tǒng)進行基于BIT 和功能一體化設(shè)計的電子設(shè)備驗證平臺的設(shè)計和實現(xiàn)非常重要。

1 基于BIT 設(shè)計的電子設(shè)備驗證平臺的總體設(shè)計

本文介紹了基于BIT 設(shè)計的電子設(shè)備驗證平臺的總體設(shè)計方案和相應(yīng)的設(shè)計步驟,并結(jié)合典型研究案例實物完成了電子設(shè)備驗證平臺的設(shè)計和實現(xiàn)。首先針對典型研究案例進行了故障模式分析和基于多信號測試性建模的測試點優(yōu)選;然后基于測試性建模測點優(yōu)選基礎(chǔ)上完成原電子設(shè)備BIT 設(shè)計的整改,來完成BIT 采集單元設(shè)計;接著通過設(shè)計的故障注入系統(tǒng)完成對典型案例實物的故障模擬和故障注入;最后驗證平臺配套的數(shù)據(jù)監(jiān)測與診斷軟件基于多總線傳輸來獲取BIT 采集單元上傳的狀態(tài)監(jiān)測數(shù)據(jù),基于統(tǒng)計分析對典型研究案例實物的測點來完成對應(yīng)的數(shù)據(jù)監(jiān)測與綜合診斷。

基于BIT 設(shè)計的電子設(shè)備驗證平臺的設(shè)計流程,主要包括測性分析建模、BIT 設(shè)計、故障注入系統(tǒng)和數(shù)據(jù)監(jiān)測與診斷軟件四個功能單元。本論文基于BIT 設(shè)計的電子設(shè)備驗證平臺總體實現(xiàn)方案如圖1 所示,主要包括兩方面內(nèi)容:第一是基于測試性分析的電子設(shè)備的BIT 設(shè)計,第二是基于BIT 設(shè)計的電子設(shè)備的性能驗證。基于測試性分析的電子設(shè)備的BIT 設(shè)計,從設(shè)計之初就開始對整個電子設(shè)備進行測試性分析,并且設(shè)計標(biāo)準(zhǔn)化的BIT 采集單元和配套的BIT 設(shè)計軟件。基于BIT 設(shè)計的電子設(shè)備的性能驗證,開發(fā)了相應(yīng)的驗證平臺,配合相應(yīng)的故障注入系統(tǒng),基于故障檢測率和故障隔離率等指標(biāo),來對電子設(shè)備進行BIT 設(shè)計后的性能驗證。

圖1 基于BIT 設(shè)計的電子設(shè)備驗證平臺總體設(shè)計

由圖1 可知,基于BIT 設(shè)計的電子設(shè)備驗證平臺總體的設(shè)計步驟如下:

(1)測試性分析:首先對電子設(shè)備硬件單元的各子功能框圖進行分析,選擇出提供能表征各個功能單元的的故障模式和測試點,然后在故障檢測率和隔離率等指標(biāo)約束下,通過可視化測試性建模與分析軟件對電子設(shè)備進行多信號建模來完成測試性分析來完成測點優(yōu)選。

(2)BIT 設(shè)計:以電子設(shè)備功能單元進行測試性分析優(yōu)選的測點的基礎(chǔ)上,在電子設(shè)備的硬件實物在設(shè)計之初預(yù)留對應(yīng)的測試點和對應(yīng)數(shù)據(jù)傳輸?shù)目偩€資源,并把電子設(shè)備對應(yīng)的測點與設(shè)計的BIT 采集單元進行連接,結(jié)合多信號測試性分析和BIT 采集單元進行電子BIT 設(shè)備的一體化設(shè)計,來完成基于BIT 設(shè)計的電子設(shè)備。

(3)故障注入系統(tǒng)設(shè)計:包括軟故障注入和硬故障注入兩種工作模式。軟故障注入首先通過基于BIT 設(shè)計的電子設(shè)備的多故障模式來建立對應(yīng)的故障知識庫,然后設(shè)計的故障注入軟件基于總線層對電子設(shè)備的原數(shù)據(jù)傳輸通信接口進行故障模擬和注入,最終來實現(xiàn)模擬電子設(shè)備實際發(fā)生的對應(yīng)故障模式;硬故障注入模式是基于通過專用的硬件注入單元對電子設(shè)備的物理層進行故障注入,來完成對底層硬件的短路或者強制引腳變化等故障操作。

(4)性能驗證:通過BIT 采集單元對基于BIT 設(shè)計的電子設(shè)備的測點進行多維數(shù)據(jù)的實時監(jiān)測和采集,并把相應(yīng)的監(jiān)測數(shù)據(jù)通過預(yù)留的多總線資源將數(shù)據(jù)上傳到監(jiān)測與診斷軟件完成數(shù)據(jù)監(jiān)測和綜合診斷,基于統(tǒng)計分析算法等來完成電子設(shè)備對應(yīng)的綜合診斷結(jié)果,結(jié)合故障檢測率和故障隔離率等指標(biāo),完成基于BIT 設(shè)計后的電子設(shè)備驗證平臺性能驗證。

2 基于BIT 設(shè)計的典型案例的電子設(shè)備驗證平臺構(gòu)建

本文電子設(shè)備的典型研究案例實物選擇VPX 高速數(shù)字收發(fā)模塊為例,主要由高速A/D 采集單元、D/A 信號生成單元、FPGA 單元、DSP 單元、高速時鐘單元、DDR3 內(nèi)存單元和PCIE 橋等組成。基于測試性分析建模和BIT 設(shè)計,來實現(xiàn)對VPX 高速數(shù)字收發(fā)模塊典型應(yīng)用案例來搭建基于BIT設(shè)計的電子設(shè)備驗證平臺,結(jié)合配套的故障注入系統(tǒng)、監(jiān)測與診斷軟件,來完成后續(xù)對電子設(shè)備驗證平臺的性能驗證。

■2.1 測試性建模與分析

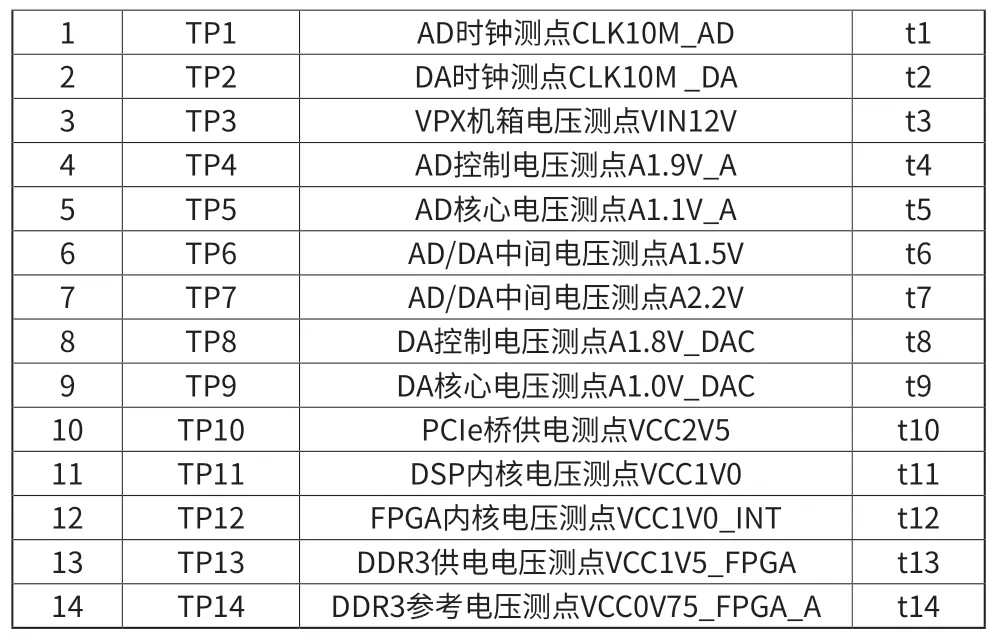

本文首先對VPX 高速數(shù)據(jù)收發(fā)模塊相應(yīng)的功能單元進行故障類型分析整理,然后通過可視化測試性建模與分析軟件對被測對象進行測試性建模,測試性建模優(yōu)選后的測點如表1 所示。在表1 中,通過選擇采用VPX 高速數(shù)據(jù)收發(fā)模塊兩路時鐘信號10 MHz_1 和10MHz_2 作為頻率信號的監(jiān)測點,來檢測AD 和DA 時鐘的是否正常工作;其余為VPX高速數(shù)據(jù)收發(fā)模塊各功能單元的供電電壓為監(jiān)測點,如果電壓不正常說明相應(yīng)的供電電壓有問題,或者相應(yīng)的功能單元出現(xiàn)故障。

表1 VPX高速數(shù)據(jù)收發(fā)模塊的測點優(yōu)選

■2.2 BIT 設(shè)計

基于BIT 設(shè)計的VPX 高速數(shù)字收發(fā)模塊的結(jié)構(gòu)框圖如圖2 所示,包括兩部分:其中一部分為對VPX 高速數(shù)字收發(fā)模塊進行電路整改來引出對應(yīng)的測點到連接器單元;另外一部分為BIT 采集單元的設(shè)計,支持電壓、頻率、波形等多維測試數(shù)據(jù)的采集,以及支持以太網(wǎng)、串口等多總線數(shù)據(jù)傳輸。

圖2 基于BIT 設(shè)計的高速數(shù)字收發(fā)模塊結(jié)構(gòu)框

基于BIT 設(shè)計的VPX 高速數(shù)字收發(fā)模塊流程包括:在對VPX 高速數(shù)字收發(fā)模塊功能單元進行測試性分析獲取優(yōu)選測點的基礎(chǔ)上,來進行基于BIT 設(shè)計的高速數(shù)字收發(fā)模塊。在不改變高速數(shù)字收發(fā)模塊功能電路的內(nèi)部電路結(jié)構(gòu)前提下,把表1 中優(yōu)選的測點引出到連接器單元;通過設(shè)計的BIT 采集單元對應(yīng)的連接器對高速數(shù)字收發(fā)模塊功能單元中預(yù)留的連接器進行相應(yīng)測點連接,來完成VPX 高速數(shù)字收發(fā)模塊功能電路中的電壓、頻率等多維數(shù)據(jù)的狀態(tài)監(jiān)測與采集,然后BIT 采集單元通過總線資源把監(jiān)測的數(shù)據(jù)傳輸?shù)狡脚_配套的監(jiān)測與診斷軟件,來完成后續(xù)電子設(shè)備驗證平臺的綜合診斷和性能驗證。

■2.3 故障注入系統(tǒng)設(shè)計

(1)軟故障注入

軟故障注入基于總線層的方式實現(xiàn)對被測對象的故障注入與模擬。首先根據(jù)表1 的VPX 高速數(shù)字收發(fā)模塊的測試點和故障類型進行相關(guān)“故障類型編碼”,通過模擬其實際的故障模式來完成故障知識庫的建立;然后故障注入軟件通過總線與基于BIT 設(shè)計的高速數(shù)字收發(fā)模塊的BIT 采集單元建立通信連接;最后故障注入軟件導(dǎo)入故障模式列表,分別設(shè)置選擇不同故障的故障注入次數(shù)和故障模式,開展對高速數(shù)字收發(fā)模塊進行故障注入試驗來模擬實際測試通道的故障。

(2)硬故障注入

硬故障注入主要是在VPX 高速數(shù)字收發(fā)模塊的物理層進行故障注入。首先通過對模塊各功能單元電路的實際工作原理進行分析,確定模塊物理層進行硬件故障注入所需的故障應(yīng)力類型、故障應(yīng)力量值和施加方式;然后通過專用的硬件注入模塊和輔助測試儀器來完成對底層硬件的短路、開路或者強制引腳變化,來完成對高速數(shù)字收發(fā)模塊實際的電源類或短路類等故障類型的注入。

■2.4 電子設(shè)備驗證平臺的搭建

在前面對VPX 高速數(shù)字收發(fā)模塊完成測試性分析、BIT設(shè)計和故障注入系統(tǒng)的設(shè)計基礎(chǔ)上,本文基于BIT 設(shè)計的高速數(shù)字收發(fā)模塊來搭建的驗證平臺實物如圖3 所示。圖3左側(cè)為裝配在VPX 機箱的基于BIT 設(shè)計的高速數(shù)字收發(fā)模塊,圖3 右側(cè)為嵌入式測試監(jiān)測與診斷軟件界面,來完成對模塊的數(shù)據(jù)監(jiān)測、綜合診斷和性能驗證。

圖3 基于BIT 設(shè)計的高速數(shù)字收發(fā)模塊電子設(shè)備驗證平臺

為了實現(xiàn)VPX 高速數(shù)據(jù)收發(fā)模塊的綜合診斷和性能驗證,首先嵌入式測試監(jiān)測與診斷軟件作為TCP 服務(wù)器與BIT 采集單元的TCP 客戶端建立以太網(wǎng)通信,上位機通過發(fā)送指令來控制BIT 采集單元的加電BIT、啟動BIT 和周期BIT 的工作模式切換,來完成電壓、頻率等多維數(shù)據(jù)采集和上傳;然后對高速數(shù)據(jù)收發(fā)模塊進行基于總線層的軟故障注入和基于物理層的硬故障注入,來模擬高速數(shù)據(jù)收發(fā)模塊實際發(fā)生該故障模式產(chǎn)生的故障現(xiàn)象和故障數(shù)據(jù);最后嵌入式測試監(jiān)測與診斷軟件基于統(tǒng)計分析算法對BIT 采集單元上傳的相關(guān)監(jiān)測數(shù)據(jù)的分析與綜合診斷,來完成構(gòu)建的基于BIT 設(shè)計的電子設(shè)備驗證平臺的故障診斷率、故障隔離率、評估指標(biāo)數(shù)值等相關(guān)性能驗證。

3 結(jié)束語

本文簡要陳述了基于BIT 設(shè)計的電子設(shè)備驗證平臺總體方案和相關(guān)設(shè)計步驟,著重描述了基于BIT 設(shè)計的典型案例的電子設(shè)備驗證平臺構(gòu)建。本文以VPX 高速數(shù)字收發(fā)模塊作為典型案例進行基于BIT 設(shè)計的電子設(shè)備驗證平臺的搭建,完成了對該模塊的測試性分析的測點優(yōu)選、BIT 設(shè)計、基于軟件和硬件的故障注入系統(tǒng)的設(shè)計、平臺配套軟件的綜合診斷和性能驗證。本文通過搭建基于BIT 設(shè)計典型案例電子設(shè)備驗證平臺,解決電子設(shè)備實物進行嵌入式設(shè)計和驗證難的問題,實現(xiàn)嵌入式測試能力與標(biāo)準(zhǔn)化的提升,能夠為有效的為電子設(shè)備的嵌入式測試與健康管理提供驗證支撐。