64G PCIe6.0產品設計挑戰及實現

李 明

(立訊技術有限公司,廣東東莞,523808)

1 引言

PCI Express技術經過二十多年的發展,已經成為一種普及的I/O技術。PCI Express?(PCIe?)6.0利用PAM-4編碼技術,包括低延遲前向糾錯(FEC)和其他機制,將使數據速率加倍,達到64 GT/s,同時保持與前幾代產品的向后兼容性,并提供能效和經濟高效的性能,PCIe 6.0將在2021年發布。PCIe 6.0主要應用于滿足人工智能、機器學習、網絡、通信系統、存儲、高性能計算等熱門市場的需求。

2 PCIe協議介紹

在過去的幾十年里,系統性能的增長與半導體技術的發展密切相關。隨著半導體制造特征尺寸接近其極限,封裝級集成對于未來系統擴展變得越來越重要,而系統擴展又高度依賴于I/O帶寬的擴展。

圖1 PCIe協議發展歷程及行業帶寬需求

自2003年首次推出以來,PCI Express(PCIe)經歷了五代發展,從2.5Gbps/通道發展到5Gbps(v2.0)和8Gbps(v3.0),再到16Gbps(v4.0),以及2019年發布的32Gbps(v5.0)。最近,業界一直在尋求解決方案,以進一步將PCIe I/O標準擴展到64Gbps(v6.0)的第六代,以滿足不斷增長的系統帶寬需求。而在32Gbps及以上時,信號完整性成為一個主要障礙,尤其是PCIe連接器是為前幾代較低的運行速度而設計的,標準PCIe連接器沿信號路徑會產生阻抗變化,而且由于連接器結構內的阻抗不連續性也會產生諧振;隨著信號數據速率的提高,這些問題變得非常重要。因此,業界正在探索替代性的連接器設計解決方案,但是這些替代解決方案與現有的封裝外形和子卡設計不能向后兼容,往往會提高PCIe連接器的成本,因此我司將致力于在原基礎結構上進一步探索,把CEM連接器平滑升級到PCIe6.0。

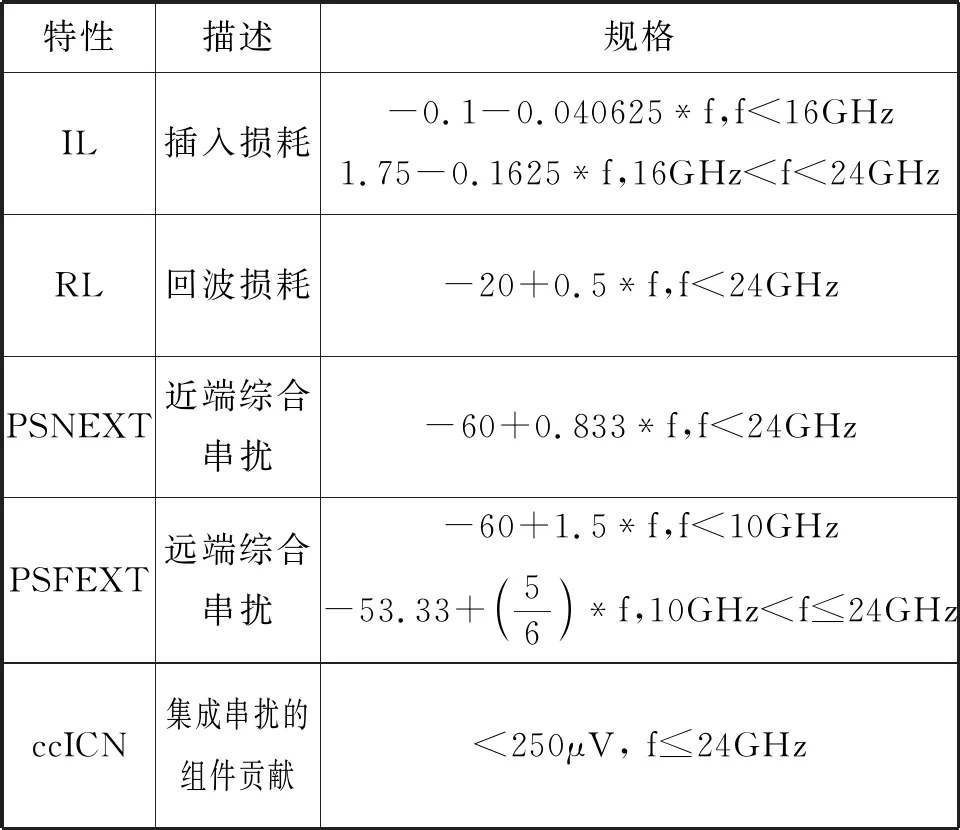

現階段PCIe6.0完整版規范尚未編寫完成,此處簡要解析于2021年8月發布的0.5版草案,對應的CEM規格線如下:

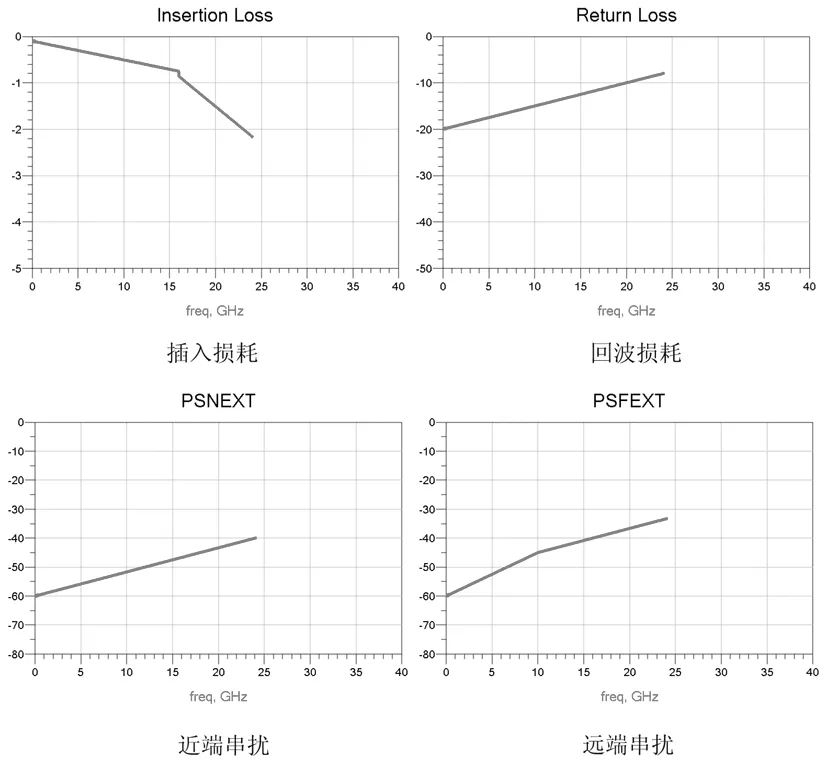

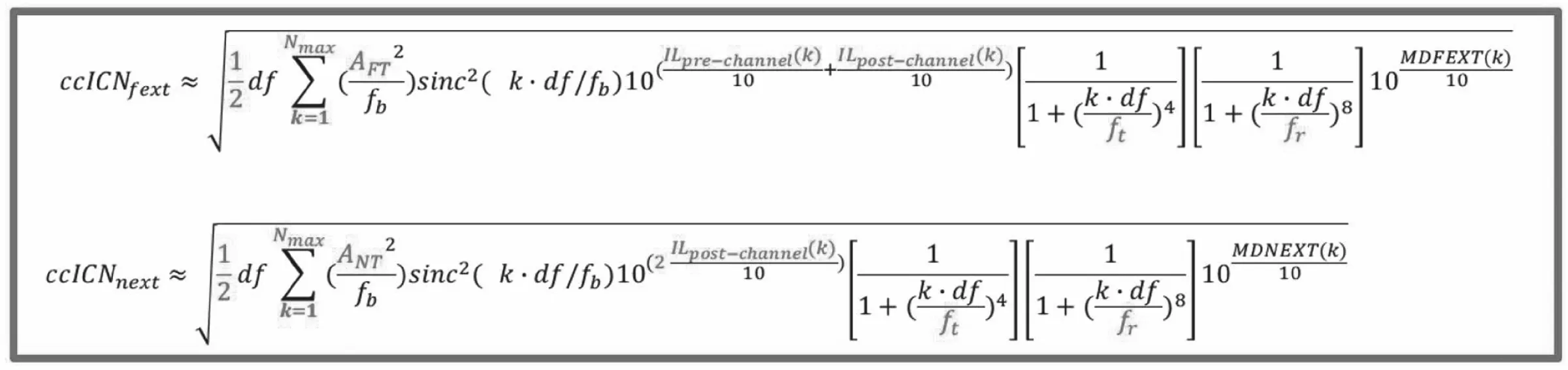

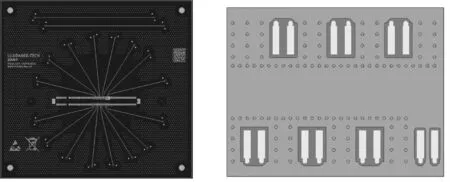

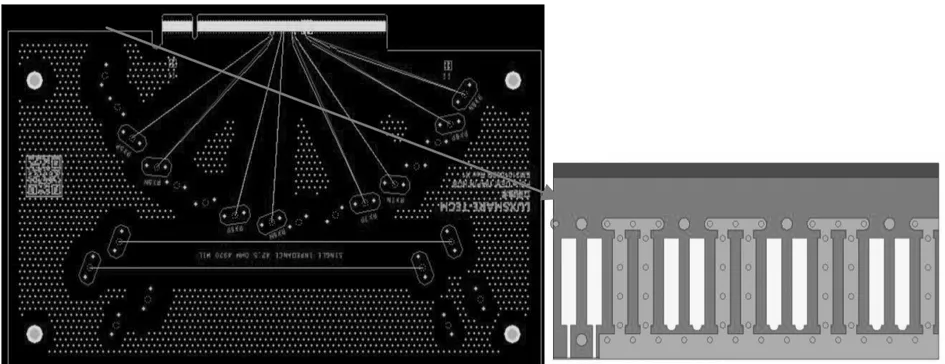

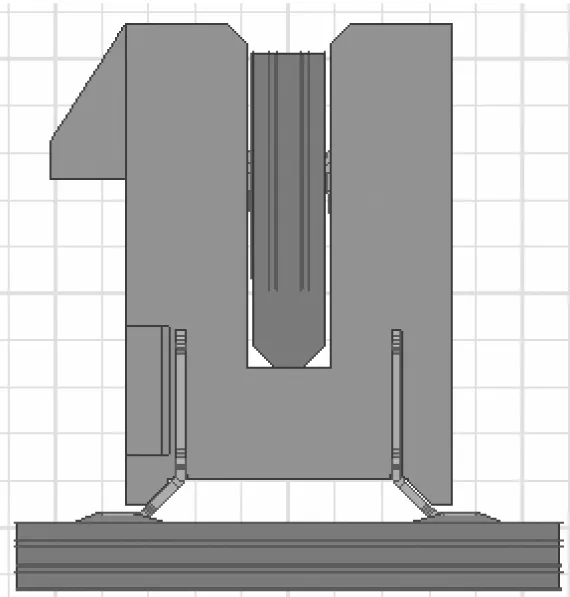

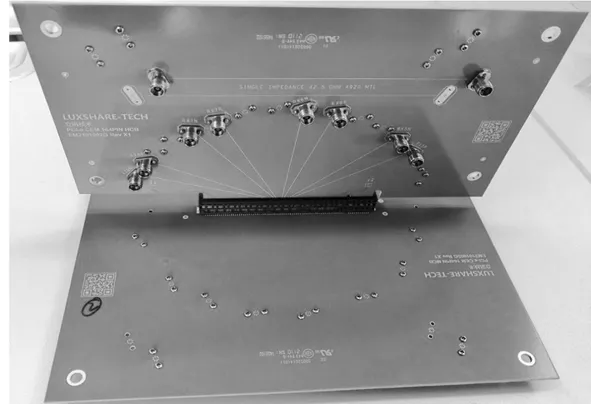

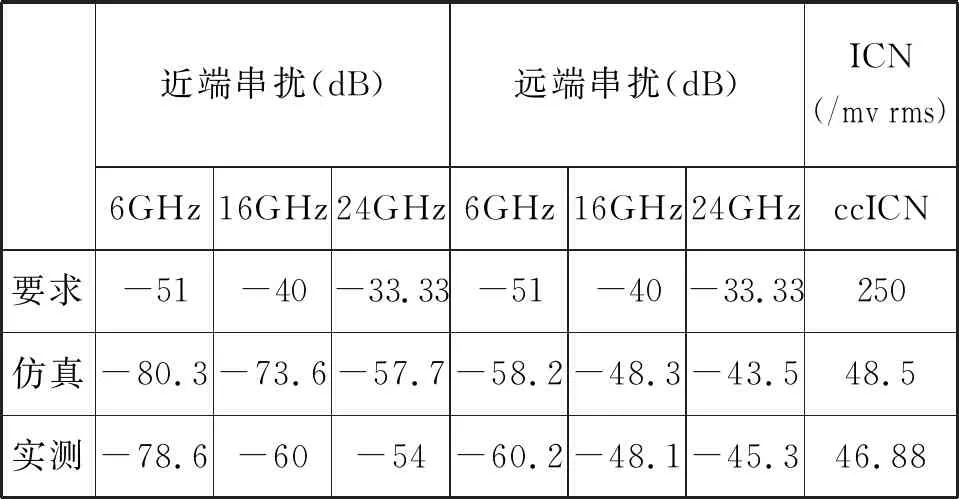

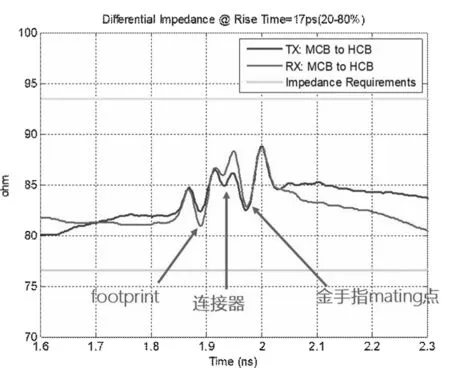

特性描述規格IL插入損耗-0.1-0.040625*f,f<16GHz1.75-0.1625*f,16GHz 圖2 PCIe 6.0 V0.5草案規范 ccICN計算公式: 條件設置如下: 其中,ccICN是新的指標規范。ccICN全稱是Component Contribution with Integrated Crosstalk Noise,通常單獨用頻域指標來定義元件的串擾是不夠的,在元器件不能完全滿足頻域指標的情況下,引入ccICN指標可以更好地在系統全鏈路中評估元器件的影響。 連接器作為鏈路中的關鍵部件,它的好壞往往直接決定了無源通道的性能,連接器的結構決定了它處于一個相對開放的空間,要想在芯片到芯片通道上實現一個阻抗受控、串擾較小的通道,連接器無論是設計還是驗證都非常復雜。 連接器的開發與驗證需處于整個產品開發過程的前期階段,確保在源端就解決掉潛在的風險:1.插損要求在16GHz前小于0.75dB,24GHz前小于2.16dB;2.CEM連接器的阻抗設計目標為85+/-5ohm,其重點在于控制力臂和端子在housing里面的尺寸;3.串擾方面的要求也很高,需要使用橋接抑制諧振。最終經過使用電磁仿真軟件HFSS進行仿真設計優化,使所有電性能滿足PCIe6.0規范推薦的mated連接器測試要求。 PCIe6.0對于插損和串擾的要求都更高,對連接器的阻抗一致性和串擾性能提出了更高的要求,隨著速率的提高,高速鏈路的前仿真變得尤為必要,通過前仿真得到電路設計的約束規則,在約束的驅動下進行PCB的布局布線,同步進行的后仿真驗證設計的可行性,可大大降低產品設計失效的風險,節約產品開發時間。 首先,需確定PCB板材的選用和層疊的設計,根據自身設計能力和經驗選擇性能最高的設計方案,進一步對測試板進行SI性能的仿真優化。連接器與測試板直接接觸的地方存在兩個最大的阻抗不匹配點,一是連接器footprint點,二是金手指同連接器端子mated點。由于系統阻抗按85ohm設計,通過仿真將footprint點和mated點的阻抗都優化到80ohm以上(上升沿17ps)。 首先,PCB材料采用穩定的松下Megtron7G,銅箔類型選用HVLP,8層板設計,層疊如下: 圖3 層疊設計 其次,在玻璃布選擇類型上,選用1078和3313等類型扁平玻璃布,避免產生玻纖效應,造成skew不良,進而影響測試出來的結果,下面是玻璃布的示意圖: 1078扁平玻璃布 1080非扁平玻璃布 接下來是板子的具體設計部分,主板差分阻抗設計為85ohm,走線2.5inch。在設計方面,需要在footprint的GND pad部分打孔,以減小板子引入的串擾。如下是主板的整體設計圖和footprint細部仿真放大圖: 圖5 主板設計 子卡差分阻抗設計為85ohm,走線2.5inch。在設計上,需要在金手指頭部打孔,減少金手指引入的串擾。如下是子卡整體設計圖和金手指部分細部仿真放大圖: 圖6 子卡設計 最后通過電磁場協同仿真,將各單點仿真參數和線材實測參數級聯成完整的鏈路進行仿真驗證。 圖7 立訊 PCIe6.0 CEM連接器仿真示意圖 下面是仿真出來的插損、回損和串擾的結果。 圖8 立訊 PCIe6.0 CEM連接器仿真性能 圖9 立訊 PCIe6.0 CEM連接器測試夾具 插入損耗 在PCB回板后,焊上連接器進行配對測試(見下圖)。在測試方面,PCIe6.0需要采用4端口的高帶寬網分進行測試,我司采用是德的4端口67G帶寬網絡分析儀N5247B進行測試,結果顯示立訊技術設計的CEM連接器滿足PCIe6.0的草案規范要求。 ccICN計算結果,滿足250μV的指標要求: 圖11 立訊 PCIe6.0 CEM連接器測試性能 仿真和測試對比結果: 表1 立訊連接器仿真和實測1 表2 立訊連接器仿真和實測2 阻抗測試圖,整體滿足85+/-5ohm的設計要求: 圖12 阻抗測試圖 本文通過介紹PCIe6.0最新的發展路標和草案規范,了解業界的最新發展方向,并通過介紹CEM連接器的產品仿真設計和驗證過程,對于如何優化連接器進行了可行性探討。在64Gbps的速率下,插損和串擾都比PCIe5.0連接器有一個很大的提升,希望能給設計工程師提供參考和優化的方向。

3 64G PCIe6.0產品設計挑戰及實現

3.1 CEM連接器設計

3.2 測試板仿真設計

3.3 連接器+測試板仿真設計

3.4 測試驗證

4 結語