基于PUF的JTAG安全認證架構

王 凱,李校南,劉燕江,陳 韜,李 偉

(1.信息工程大學 信息安全重點實驗室,河南 鄭州 450001;2.96901部隊,北京 100094)

0 引 言

隨著半導體和集成電路技術的發展,SoC(system on chip)通過將通用處理器、系統總線、接口和存儲等模塊集成到單顆芯片中,能夠獨立搭建一個完整的片上系統,滿足用戶多樣化的應用需求,已經成為了當前信息系統的核心部件[1]。JTAG(joint test action group)作為一種國際標準調試協議(IEEE1149.1)在芯片測試和系統調試中受到了廣泛應用。如果對所有用戶開放SoC的JTAG調試權限,必然造成嚴重安全隱患[2]。因此,必須對JTAG調試增加安全防護措施,以保證SoC安全。

近年來,國內外學者針對JTAG接口保護的研究主要從以下幾個方面展開。文獻[3]采用了兩層機器學習的JTAG安全防護方案,通過支持向量機(support vector machines,SVM)監測用戶操作的合法性來抵御JTAG非法攻擊。文獻[4]通過基于機器學習的三級監測器和陰影寄存器,實現了JTAG調試的可控性和可觀測性,實現了保護JTAG接口的目的。文獻[5]提出了一種對JTAG內部TAP控制器數據加密,進而保護JTAG內部敏感信息泄露的安全防護方式。而文獻[6]則采取了一種對整個掃描鏈數據進行加密的方式,實現了對JTAG接口的安全防護。

上述文獻主要從JTAG接口安全認證、機器學習監測和JTAG數據加密等方式完成對JTAG接口的保護,其中現有的JTAG方式大多基于公鑰密碼算法實現,雖然安全性較高,但是硬件開銷大,且認證效率低。而通過機器學習監測用戶操作,也很難抵御所有的JTAG攻擊方式,安全性不足。而JTAG數據加密雖然能夠防止敏感信息泄露,但也帶來了硬件開銷大,降低調試效率的嚴重問題。

針對SoC在資源受限條件下的JTAG接口安全認證的問題,結合SoC電路基本結構,本文深入分析了JTAG安全防護需求、HMAC身份認證協議和SRAM-PUF密鑰生成,提出了一種基于SRAM-PUF的低成本JTAG接口安全認證架構,在保證合法用戶正常調試需求的同時,有效抵御攻擊者非法入侵系統,保護SoC中敏感信息的安全性。

1 SRAM-PUF密鑰生成模型

HMAC協議由H.Krawezyk、M.Bellare、R.Canetti提出,是一種基于哈希運算消息認證碼的身份認證協議,近年來HMAC協議廣泛應用在多種安全認證服務中,其安全性能夠抵御多種形式的攻擊,并經受了多個安全應用的考驗[7]。HMAC協議的安全性基礎在于合法用戶與JTAG接口間的共享密鑰。如何確保密鑰的可靠生成與安全存儲是保證HMAC認證協議安全性的關鍵。而密鑰的可靠生成與安全存儲通常需要滿足以下3個基本條件:

(1)生成隨機性。隨機性是衡量密鑰質量的重要指標。安全性強的密鑰應當具有良好的隨機性和密碼特性,進而保證其唯一性和不可預測性,確保整個HMAC協議的安全性。

(2)存儲安全性。密鑰在應用過程中必須有一段獨立的受保護的存儲空間,防止非法用戶通過各種攻擊手段獲取到密鑰的正確內容。

(3)應用可靠性。在HMAC協議中,密鑰作為合法用戶的身份標識,一旦密鑰存在誤碼,則將導致HMAC消息認證碼與實際不符,進而導致認證失敗。

要正確實現基于HMAC身份認證的安全JTAG調試協議,合法用戶與安全JTAG接口間的共享密鑰可靠性是關鍵。而傳統的密鑰生成器大多借助于某種噪聲源產生具有較好統計分布特性的序列,再對這些序列進行復雜的隨機性檢驗過程以確保其具有較好的密碼特性。這種方式一方面需要經過復雜的隨機性檢驗過程,另一方面也難以重復產生相同的密鑰,可靠性較差[8]。基于此,國內外科研工作者提出了基于PUF(physical unclonable function)的密鑰生成方法。該方法能夠很好滿足以上3個基本條件,其基本原理是利用芯片在制造過程中,由于工藝限制,使得每顆芯片都擁有其獨特的“物理指紋”[9]。PUF的主要特點在于針對每一個激勵(challenge),不同的PUF電路會產生不同的響應(response),即每顆芯片都具有其獨特的激勵響應對(challenge-response pairs,CRPs),因而具有較強的隨機性、魯棒性、不可預測性和不可克隆性,近年來在密鑰生成和用戶身份認證得到了廣泛應用。

1.1 SRAM-PUF基本原理

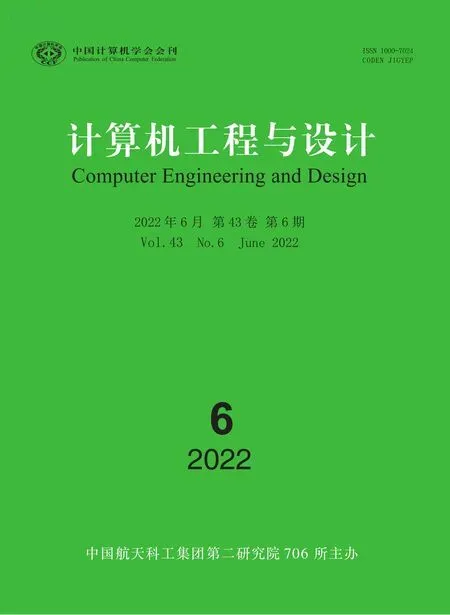

SRAM-PUF的基本原理就是,不同的SRAM單元受工藝限制,導致兩個反相器中MOS管的“強度不同”,進而使其在流片后表現出不同的上電特性,如圖1所示[10]。因此,SRAM存儲單元的上電初始值即可作為SRAM-PUF。

圖1 SRAM-PUF基本原理

定義SRAM中的一對MOS管的晶體管參數分別為I1和I2,此時SRAM某個響應位的上電初始值r可以表示為式(1)

(1)

從理論上來講,對于特定的SRAM-PUF電路結構,在每次上電時,每個存儲單元出現“0”和“1”的概率各占50%。而實際工作過程中,I1和I2均受到閾值電壓、溫度和老化程度影響,假設二者的差值為ΔI,標準偏差為σ,則此時SRAM某個響應位的上電初始值r′可以表示為式(2)

(2)

假設芯片在兩次上電過程中,某一SRAM單元初始值不同的概率Pe,則其值可表示為式(3)

(3)

對一般SRAM而言,其中某一存儲單元兩次上電初始值不同的概率Pe通常不大于15%[11]。

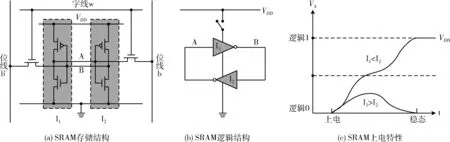

以一個16×16的SRAM存儲單元為例,其上電初始值的分布模型如圖2所示[12]。在每次上電時,某些存儲單元的上電初始值固定為“0”,某些單元的上電初始值固定為“1”。還有一小部分單元的上電初始值受到溫度、電路老化和噪聲等因素的影響,其上電初始值可能為“0”也可能為“1”。這些上電初值不穩定的存儲單元,是影響SRAM-PUF響應可靠性的主要原因。

圖2 16×16-SRAM上電初始值分布模型

1.2 SRAM-PUF密鑰生成模型

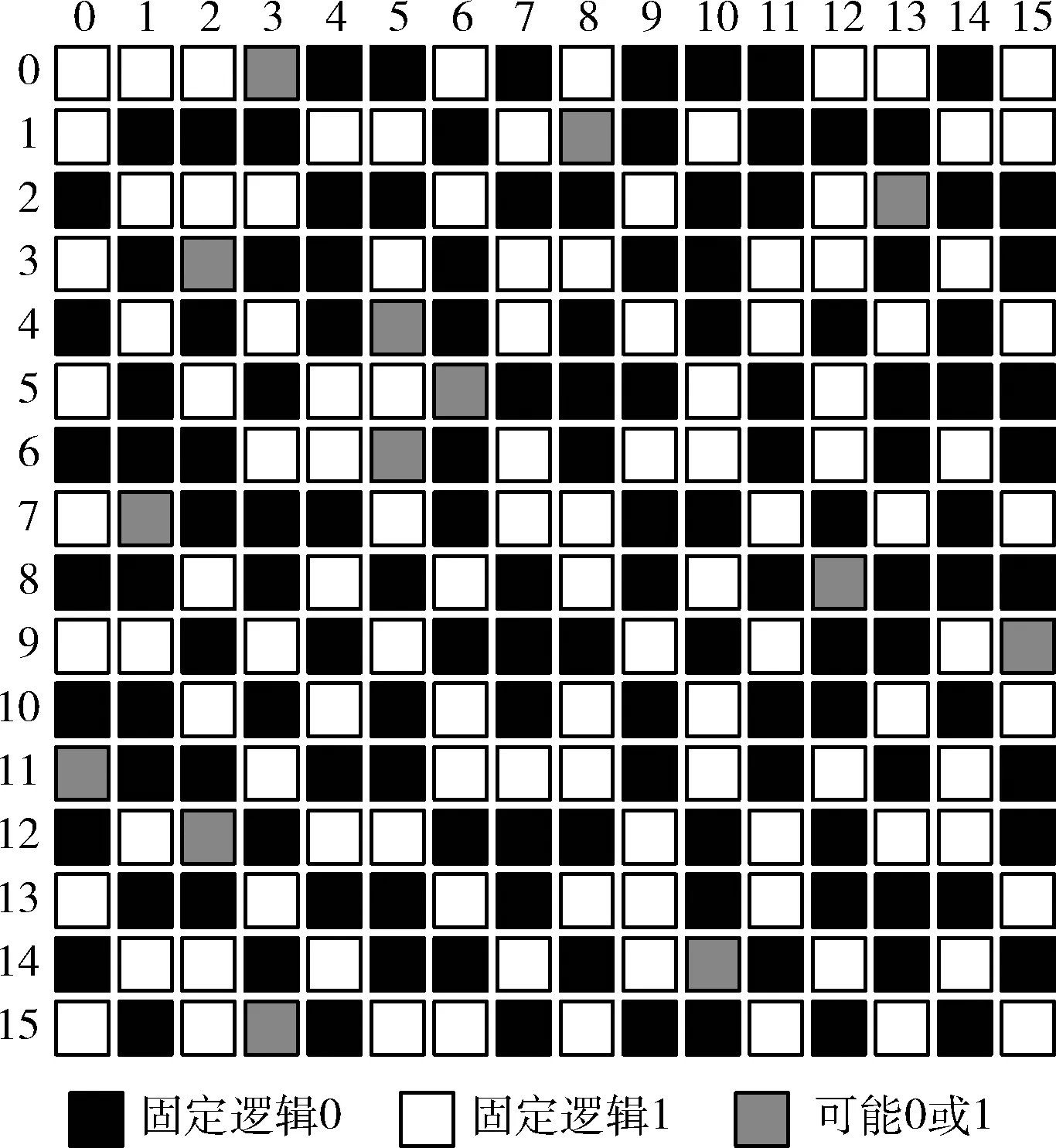

為了從SRAM-PUF這種帶噪聲的芯片“物理指紋”中,提取出能夠精確再生且隨機分布的密鑰,本文采取了一種基于模糊提取器(fuzzy extractor)的可靠密鑰生成模型。該模型由Dodis等提出,近年來在指紋識別、虹膜識別和量子信息等領域得到了廣泛應用[13]。基于模糊提取器的可靠密鑰生成模型,按照其實現過程,大體可以分為密鑰注冊和密鑰重構兩個階段。密鑰注冊模塊電路結構如圖3所示[14]。

圖3 密鑰注冊模塊電路結構

c=α⊕p

(4)

b=ENC(β)

(5)

s=b⊕p

(6)

(7)

(8)

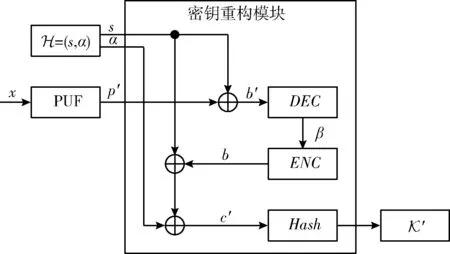

密鑰重構模塊電路結構如圖4所示。

圖4 密鑰重構模塊電路結構

b′=p′⊕s

(9)

β=DEC(b′)

(10)

b=ENC(β)

(11)

c′=α⊕b⊕s

(12)

(13)

根據式(3),假設在任意k位SRAM存儲單元中,上電以后出現i位錯誤的概率為Pi,則其值可以表示為式(14)

(14)

設t為所選糾錯算法的最大糾錯能力,那么若要從k位SRAM-PUF中成功完成密鑰重構,則SRAM-PUF的最大錯誤位數不能超過t。因此,從k位SRAM-PUF從成功完成密鑰重構的概率Psuccess可以表示為式(15)

(15)

在實際應用過程中,要完成可靠密鑰生成,通常要求糾錯的失敗率小于10-6[15],即

Psuccess≥0.999 999

為了實現對PUF的糾錯,近年來國內外學者提出了大量的糾錯算法,如重復碼、格雷碼、循環碼和BCH碼等。在眾多的糾錯算法中,BCH碼具有糾錯能力強,糾錯能力可控等特點,非常適合應用于SRAM-PUF糾錯中。現有BCH碼糾錯的主要缺陷在于譯碼相對復雜且硬件開銷大[16]。

在SoC安全JTAG調試中,HMAC認證所需共享密鑰只需在上電初始化時生成即可,因此其生成速度不會影響系統運算性能。而面積開銷則是衡量SRAM-PUF密鑰生成的關鍵指標。為了解決現有SRAM-PUF可靠密鑰生成硬件開銷大的問題,本文設計了一種基于模糊提取器和小位寬BCH碼的密鑰生成模型,能夠滿足資源受限條件下的可靠密鑰生成。

SRAM-PUF低成本安全可靠密鑰生成過程如算法1所示。

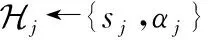

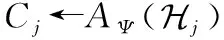

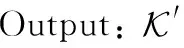

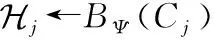

Algorithm 1: 基于模糊提取器的注冊密鑰生成算法

Input:x,α,β,Ψ

Output:K,C

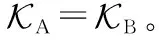

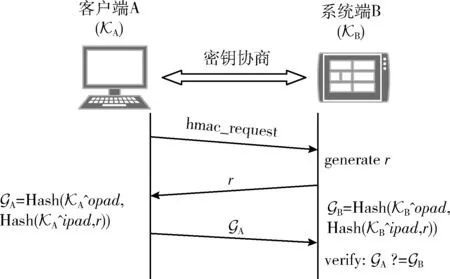

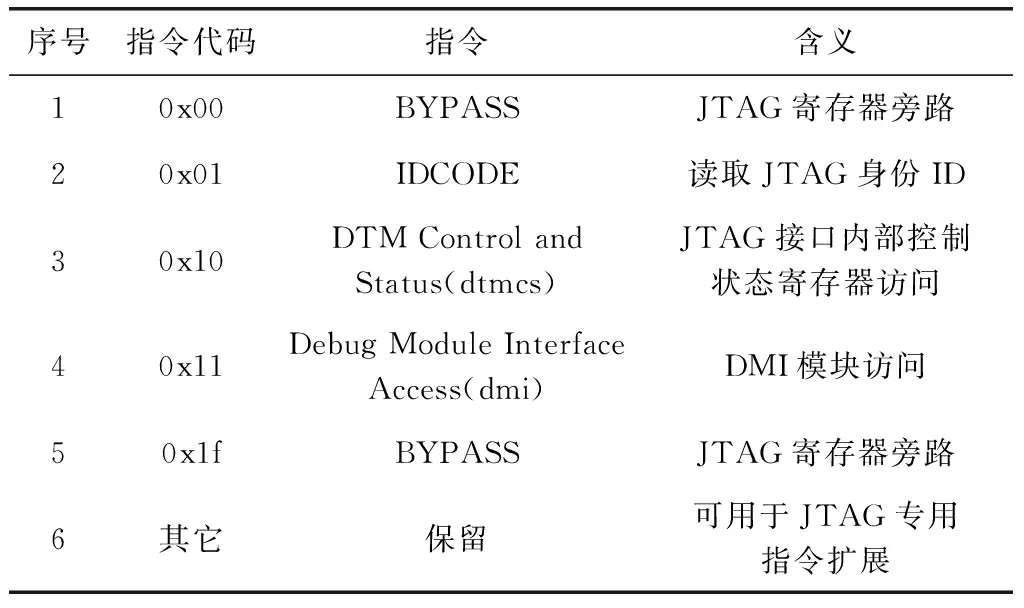

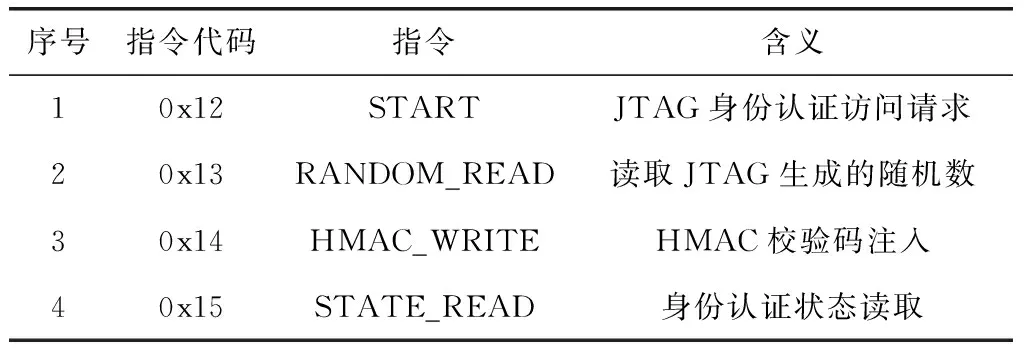

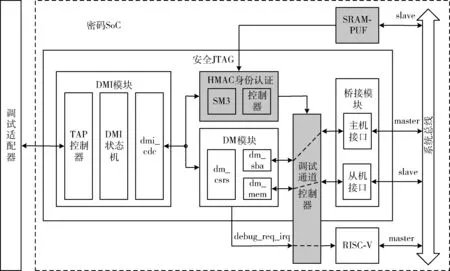

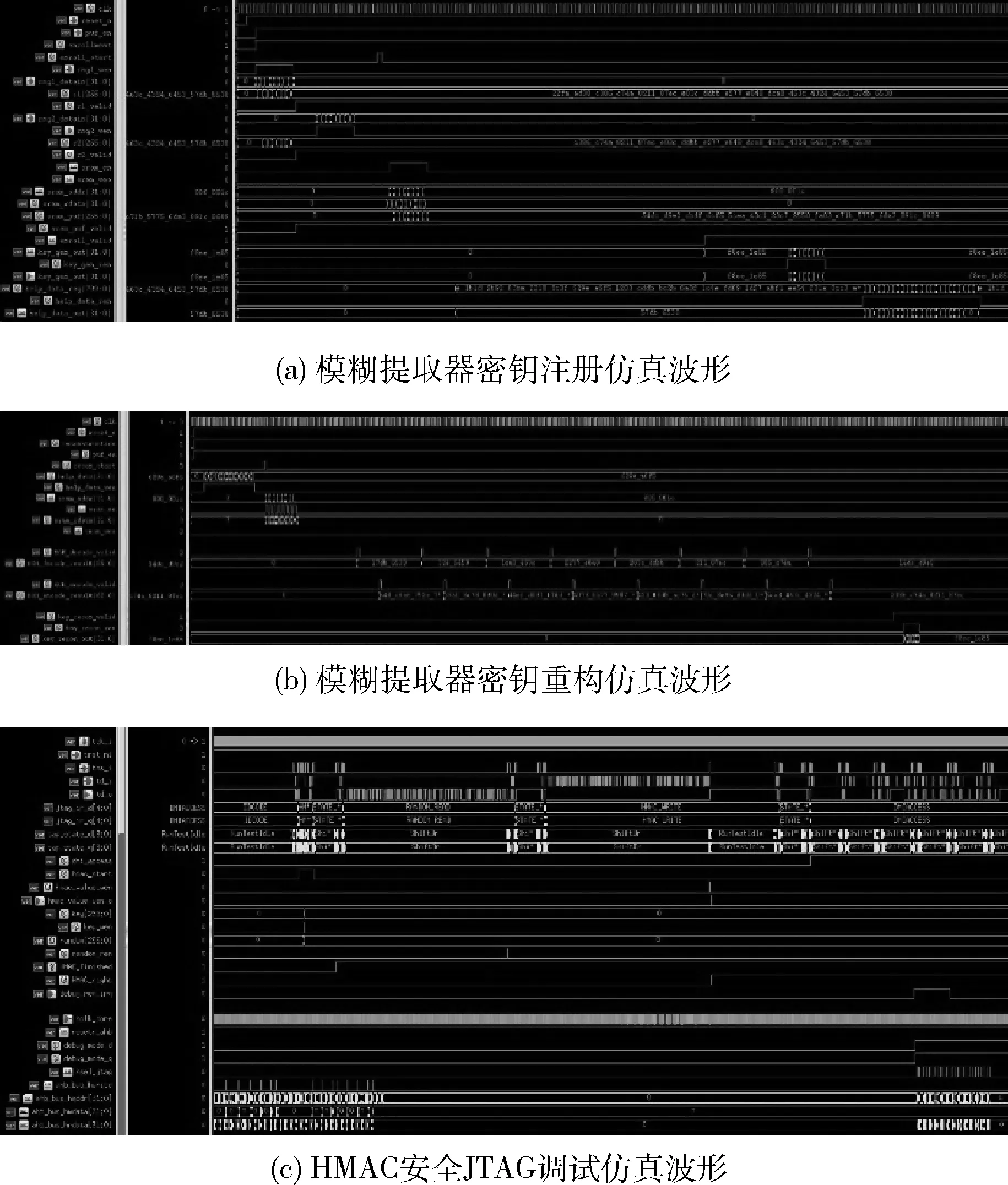

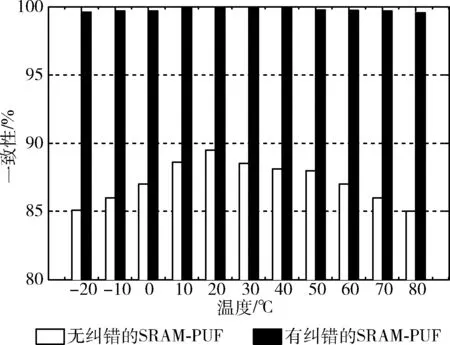

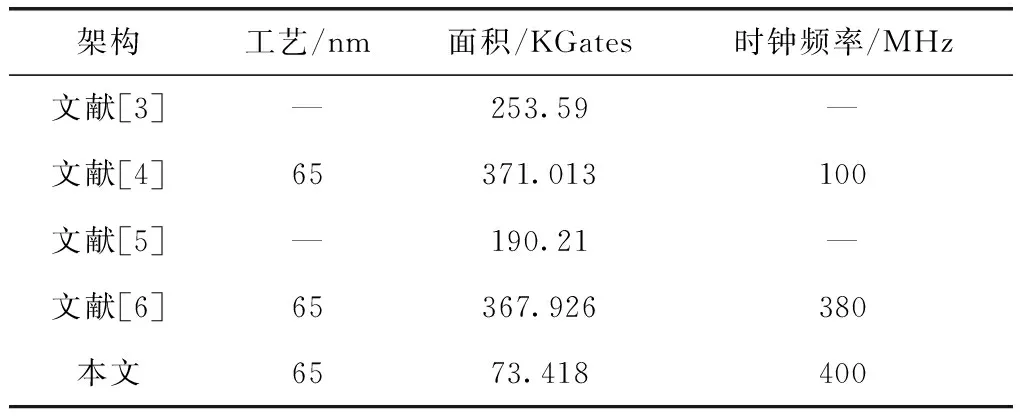

(1) For j (2)pj←P(xj); (3)cj←αj⊕pj; (4)bj←E(βj); (5)sj←bj⊕pj; (8)P(xj)←11…1; (10) End for (11)C←{C1,C2,…,CN}; SRAM-PUF的重構過程如算法2所示。 Algorithm 2: 基于模糊提取器的密鑰重構算法 Input:x,C,Ψ (1) For j (3)p′j←P(xj); (4)b′j←p′j⊕sj; (5)βj←D(b′j); (6)bj←E(βj); (7)c′j←αj⊕(bj⊕sj); (9)P(xj)←11…1; (10) End for 圖5 HMAC身份認證流程 由圖5可得,HMAC身份認證協議的安全性基礎在于合法用戶與網絡信息系統間的密鑰共享。因此,要安全可靠實現SoC的JTAG調試,必須確保SRAM-PUF密鑰生成的可靠性,以及HMAC協議實現過程的安全性,二者缺一不可。 如何保證JTAG調試用戶的安全性,是防止非法用戶入侵系統造成敏感信息泄露的關鍵。基于HMAC安全認證的JTAG安全防護思想,就是在標準JTAG協議的基礎上增加身份認證過程。擴展接口安全認證后的JTAG連接初始化過程如圖6所示。 圖6 JTAG安全調試流程 根據圖6,整個JTAG安全調試過程可以分為JTAG認證過程和JTAG調試過程兩部分。其中JTAG認證過程主要用于SoC通過HMAC協議判別調試用戶的合法性,進而阻止非法用戶入侵系統。合法用戶經過HMAC身份認證以后,JTAG模塊將開啟JTAG調試通道,允許用戶進入JTAG調試過程,進而實現調試程序的編譯和執行,完成對整個SoC的調試和控制。 本文以RISC-V處理器的JTAG調試為例,開展安全JTAG調試協議設計與實現。作為整個JTAG調試的核心,用戶能夠通過TAP控制器完成調試指令和數據的注入,進而實現完整的JTAG調試操作。為了在標準JTAG基礎上融入安全身份認證協議,需要完成JTAG調試指令擴展和JTAG接口集成HMAC身份認證電路兩部分工作。 JTAG調試指令按照其具體的功能可以分為通用指令和專用指令兩種。其中通用指令主要完成一些基本的JTAG調試操作,見表1。 表1 通用JTAG調試指令 針對JTAG協議融合HMAC身份認證協議,需要對JTAG調試指令做以下幾條用戶身份認證指令擴展,見表2。 表2 JTAG擴展用戶身份認證指令 為了使標準JTAG接口能夠支持JTAG擴展用戶身份認證指令,進而實現安全JAG調試,需要進一步修改TAP控制器中IR寄存器,并在JTAG接口內部集成HMAC身份認證模塊和調試通道控制器。完整的安全JTAG調試接口,其整體架構如圖7所示。 圖7 安全JTAG接口電路整體架構 整個安全JTAG接口按照其功能,可以劃分為DMI模塊、HMAC身份認證模塊、DM模塊、調試通道控制器、主機接口和從機接口6個部分。其中DMI模塊主要接收來自調試適配器的JTAG調試信號并通過協議轉換,進而完成調試指令和調試數據的讀寫訪問。HMAC身份認證模塊則完成執行調試認證過程,并控制調試通道控制器的開啟和關閉。DM模塊則負責根據外部注入的調試指令和數據,完成相應的調試操作,并在調試通道控制器開啟時,實現對RISC-V處理器的調試控制,以及對片上存儲資源的讀寫訪問。 為了驗證本文設計架構的合理性、安全性和可靠性,本文基于RISC-V處理器、安全JTAG接口、AMBA總線、SRAM-PUF和UART等單元,搭建了一套SoC驗證平臺,并通過了功能仿真,其結果如圖8所示。 圖8 基于SRAM-PUF的安全JTAG調試仿真波形 根據圖8,本文中基于SRAM-PUF的安全JTAG調試能夠從帶噪聲的SRAM-PUF響應中生成可靠密鑰,并基于該密鑰實現基于HMAC協議的JTAG安全認證。 SoC中JTAG調試的安全性,直接決定了整個系統的安全性。而在本文設計的安全架構下,HMAC協議的安全性,以及用戶與SoC間共享密鑰的安全性,是整個系統的安全性基礎。下面針對典型的JTAG攻擊方式,對整個調試協議進行安全性分析。 (1)重放攻擊 對安全JTAG認證進行重放攻擊,是指攻擊者向JTAG接口發送一個合法用戶已經發送過的數據包,進而達到欺騙JTAG接口的目的。而每次HMAC身份認證時,SoC都會生成一組新的隨機數r,保證了認證的實時性。因此即使攻擊者能夠捕獲到上一次的身份認證通信內容,也無法在下一次身份認證時使用。 (2)克隆攻擊 相比于重放攻擊,克隆攻擊對攻擊者有著更高的要求,即:①攻擊者必須了解整個身份認證協議的運算過程和通信內容;②攻擊者必須要有和合法用戶相同的計算能力;③攻擊者必須掌握合法用戶的私密信息(即HMAC協議中的共享密鑰K)。HMAC協議采用的是單向雜湊函數,且共享密鑰長度大于雜湊算法分組長度(SM3為512 bit),使現有的計算平臺無法實現克隆攻擊。 (3)猜想攻擊 猜想攻擊是指攻擊者在已知合法用戶與JTAG接口間通信內容的基礎上,從中分析提取出共享密鑰。這種攻擊方式對于攻擊者的運算能力要求比克隆攻擊更高,必須采用高強度的密碼破解算法。而用戶要想對認證密鑰進行猜想或窮舉,在實現上也是不可行的。 (4)中間人攻擊 中間人攻擊需要攻擊者能夠通過各種技術手段讓自己能夠作為一個虛擬用戶,控制合法用戶與SoC之間的數據通信過程。這要求攻擊者必須控制信道,且同時欺騙合法用戶和JTAG接口。而實際上,合法用戶與JTAG接口在認證啟動之前,早已完成了密鑰共享,由此保證了攻擊者無法實現中間人攻擊。 (5)監聽攻擊 監聽攻擊是一種攻擊者通過監聽合法用戶與安全JTAG接口之間的通信內容,進而從中分析和計算得到系統敏感信息的方式。在安全JTAG認證過程中,通信內容只有該次認證的認證請求、隨機數和HMAC值,而并不包含任何與合法用戶及安全JTAG身份相關的信息。因而本文中的安全架構能夠抵抗監聽攻擊,從而保護合法用戶身份信息。 經過以上分析,本文提出的JTAG接口認證架構,能夠抵御典型的JTAG攻擊方式,在保證合法用戶正常完成JTAG調試的基礎上,防止攻擊者非法入侵系統并造成敏感信息泄露。 SRAM-PUF生成密鑰的安全性和可靠性,是決定整個JTAG認證架構安全性和可靠性的關鍵。一般來說,按照FPGA芯片實現原理,絕大多數FPGA內部并不存在真實的SRAM存儲單元,僅僅依靠FPGA板級驗證平臺無法完成SRAM-PUF密鑰生成可靠性驗證。因此本文在實驗過程中,采取“SoC芯片+FPGA”方式完成SRAM-PUF密鑰生成可靠性驗證。其中SoC芯片采用的是實驗室已經流片驗證成功的某型SoC芯片,其內部集成了存儲空間大小為8192×32的SRAM,用作SRAM-PUF單元。而FPGA則選取Xilinx Zynq-7000 FPGA,其中運行模糊提取器實現密鑰的注冊與重構。SoC芯片與FPGA之間通過UART接口進行通信。系統運行時,SoC芯片內部通用處理器執行匯編程序,讀取SRAM-PUF上電初始值并通過UART接口發送給FPGA芯片。而FPGA芯片收到后則通過模糊提取器完成密鑰注冊/重構,并將其反饋給SoC芯片。 BCH編解碼作為模糊提取器實現SRAM-PUF密鑰生成的關鍵模塊,不僅其糾錯能力決定了密鑰生成的可靠性,而且也占據了模糊提取器面積開銷的大部分。本文為了尋求SRAM-PUF密鑰生成需求、模糊提取器面積開銷之間的平衡,基于BCH(63,30,6) 編解碼方式完成了模糊提取器設計。即從每組32 bit的SRAM-PUF單元中選取30 bit作為信息位進行糾錯編碼,此時BCH編碼的實際糾錯能力為6 bit,糾錯率為20%,能夠很好滿足SRAM-PUF錯誤率為15%的糾錯需求。 另一方面,為了滿足PUF生成密鑰的安全性需求,本文選取國家密碼管理局發布的SM3算法作為模糊提取器中的Hash函數。每當BCH完成對256 bit的SRAM存儲進行編解碼以后,可以啟動SM3算法生成密鑰。 為了評估本文提出SRAM-PUF密鑰生成架構的密鑰生成質量,本文通過一致性指標λ來衡量相同SRAM-PUF生成密鑰的可靠性[18],如式(16)所示。其中,X表示SRAM-PUF的存儲位數,Y表示實驗次數,而ζi,j則表示SRAM-PUF響應值中,第i位在第j次實驗中的糾錯輸出結果 (16) 基于ThermoJet Environment Simulator、Xilinx Zynq-7000 FPGA和SoC芯片搭建了SRAM-PUF一致性測試平臺,其中SoC芯片和FPGA開發板放在ThermoJet Environment Simulator的氣罩下,測試系統如圖9所示。ThermoJet Environment Simulator是一種通過氣流為SoC芯片測試提供-80 ℃~+225 ℃溫度環境,溫度精度±1 ℃,可為芯片溫度測試提供長時間穩定的測試環境。 圖9 SRAM-PUF一致性測試平臺 本文在-20 ℃到80 ℃對SoC芯片內的SRAM-PUF進行溫度測試,其中溫度間隔為10 ℃,分別對SRAM-PUF進行了300次一致性測試,得到一個300×11的PUF輸出響應矩陣。利用式(16)的一致性計算方法計算在11個溫度區間下的一致性值,并對比了糾錯前后的一致性,具體結果如圖10所示。 圖10 不同糾錯狀態下SRAM-PUF一致性統計結果 根據圖10可得,在沒有BCH編解碼糾錯的情況下,SRAM-PUF響應的一致性率僅為85%~90%。而經過BCH編解碼之后,SRAM-PUF的可靠性可得到大幅度提升,尤其是在溫度條件為10~40 ℃時,SRAM-PUF響應的糾錯成功率最高可達99.98%,有效提高了SRAM-PUF的魯棒性,非常適合應用于SoC可靠密鑰生成和JTAG接口認證。 為了對本文提出的JTAG架構進行面積和性能評估,將其在CMOS 65 nm工藝下完成了仿真綜合,實驗結果見表3。 表3 安全JTAG架構 根據表3可得,相比文獻[3-6],本文中的JTAG架構在保證用戶身份認證安全性的前提下,在面積開銷方面具有較大優勢,非常適合應用于資源受限條件下的網絡信息安全系統下的JTAG。此外,本文中的安全架構硬件開銷主要包括JTAG接口擴展HMAC身份認證單元和模糊提取器兩部分。該架構雖然整體面積與文獻[2]較為接近,但是模糊提取器單元卻有更廣泛的應用,其生成的密鑰不僅可以用作JTAG接口安全認證,還能應用于其它領域,如數據加密和消息簽名驗證等。 而在實現性能方面,由于文獻[3]和文獻[4]是通過機器學習檢測JTAG調試用戶的合法性,而文獻[5]和文獻[6]是通過JTAG數據加密保護系統敏感信息安全,與本文采取的實現思想差異較大,因而彼此間的比較沒有意義。因此,同樣是JTAG接口身份認證,本文中的安全架構具有更高的認證效率。 針對SoC中的JTAG接口認證,本文深入分析了SRAM-PUF實現原理、SoC密鑰生成需求和HMAC身份認證協議,提出了一種基于SRAM-PUF的低成本可靠JTAG接口認證架構,并完成了實驗驗證和安全性分析。實現結果表明,該架構能夠通過增加少量的硬件資源,實現可靠密鑰生成和JTAG接口認證,有效抵御典型的JTAG攻擊方式,保證網絡信息系統的數據安全性,非常適合應用于各類資源受限條件下的網絡信息系統。此外,基于SRAM-PUF生成的密鑰也可以應用于其它方面,比如用作會話密鑰加密系統敏感信息,或者用作用戶私鑰完成消息簽名等。下一步,本文將繼續深入展開研究,進一步提升SoC和信息系統的安全性。

2 基于SRAM-PUF的JTAG調試認證

2.1 HMAC身份認證協議概述

2.2 安全JTAG調試協議

3 實驗驗證與評估

3.1 JTAG認證安全性分析

3.2 密鑰生成可靠性分析

3.3 架構性能評估

4 結束語