探地雷達采集系統時間展寬電路校正方法研究

任以晨,鄭隆浩,張志剛,賓 峰,唐立軍

(1.長沙理工大學物理與電子科學學院,湖南長沙 410114;2.近地空間電磁環境監測與建模湖南省普通高校重點實驗室,湖南 長沙 410114)

探地雷達技術用于探測地下物質,具有無損性、便攜性和分辨率高等特點,廣泛應用于地質勘測、文物勘探等工程中。隨機等效采樣技術是探地雷達采集系統中的關鍵技術,其難點是精確測量觸發點和參考點之間的時間差[1-2]。由于時間脈沖較窄,直接測量的難度和成本較高,一般采用時間展寬電路間接測量該時間差。國內外研究表明,當采集系統工作在高溫、低溫、高濕度、高氣壓等惡劣環境中,展寬電路中核心元件如積分電容、晶體管的性能參數會發生變化,導致采集系統工作精度降低[3-4]。由于系統一般在井下工作,時間展寬電路受井下環境溫度和元器件參數變化的影響大,只能在固定的環境下進行測量,目前主要使用恒溫瓶,但是該方法調試復雜且精度受到較大影響[5-6]。

為更好地解決時間展寬電路在井下的工作性能不穩定的問題,文中通過改進電路來探索一種時間展寬電路校正方法,研究采集系統中隨機等效采樣的時間展寬電路改進方法[7],降低環境溫度變化對時間測量精度的影響。

1 探地雷達采樣原理

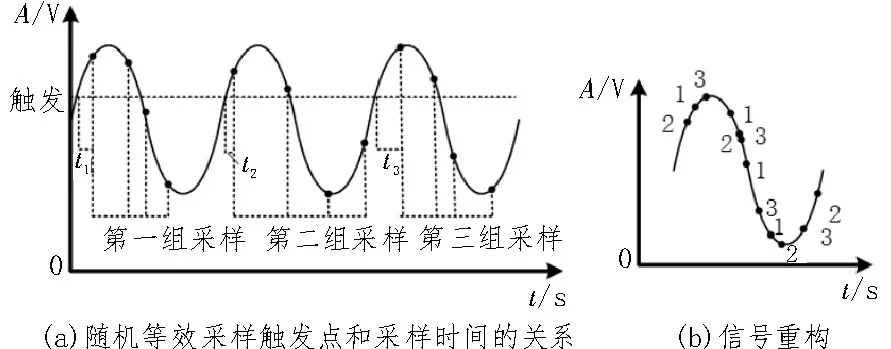

探地脈沖雷達信號一般處于短波段和超短波段,以100 MHz 的探地雷達為例,每個周期采樣20 個點,需要2 GSPS 以上的采樣率,如果使用實時采樣方式進行采樣,則存在成本過高、電路體積大、數據吞吐量大的問題,不適合在井下使用,因此一般采用等效采樣方式[8]。等效采樣分為順序等效采樣和隨機等效采樣,順序等效采樣信號在井下難以同步,隨機等效采樣的采樣點是隨機分布的,只要測量出每個信號周期觸發點和采樣點之間的時間差T1,就可以確定采樣序列在信號波形中的位置,重構采樣信號的完整波形,無需對發射機、接收機進行同步[9]。因此,探地雷達一般采用隨機等效采樣方式。

探地雷達數據恢復過程如圖1 所示,隨機等效采樣觸發點和采樣時間的關系如圖1(a)所示,信號重構過程如圖1(b)所示,信號重構的關鍵是精確測量每個采樣點與觸發點之間的時間間隔[10]。

圖1 數據恢復過程

2 時間展寬電路原理

根據隨機等效采樣原理可知,信號重構的關鍵是精確測量每個采樣點和觸發點的時間間隔T1,這個時間間隔很短,難以直接測量,需要設計時間展寬電路對時間間隔進行拓寬[11]。根據探地雷達的環境和測量條件,該文采用雙斜率電容充放電方法來設計時間展寬電路。

雙斜率電容充放電脈沖展寬原理如圖2 所示,通過較大恒流源I1對電容C進行快速放電,再使用比I1等比例小的恒流源I2對電容進行慢速充電,時間展寬倍數K為恒流源I1與I2的比值[12]。

圖2 電容充放電脈沖展寬原理

將時間間隔TX分成t1、t2和t3,將難以直接測量的t1和t2展寬為Kt1和Kt2,然后對Kt1、Kt2和t3分別進行測量,可以得到時間間隔TX的值[13]。

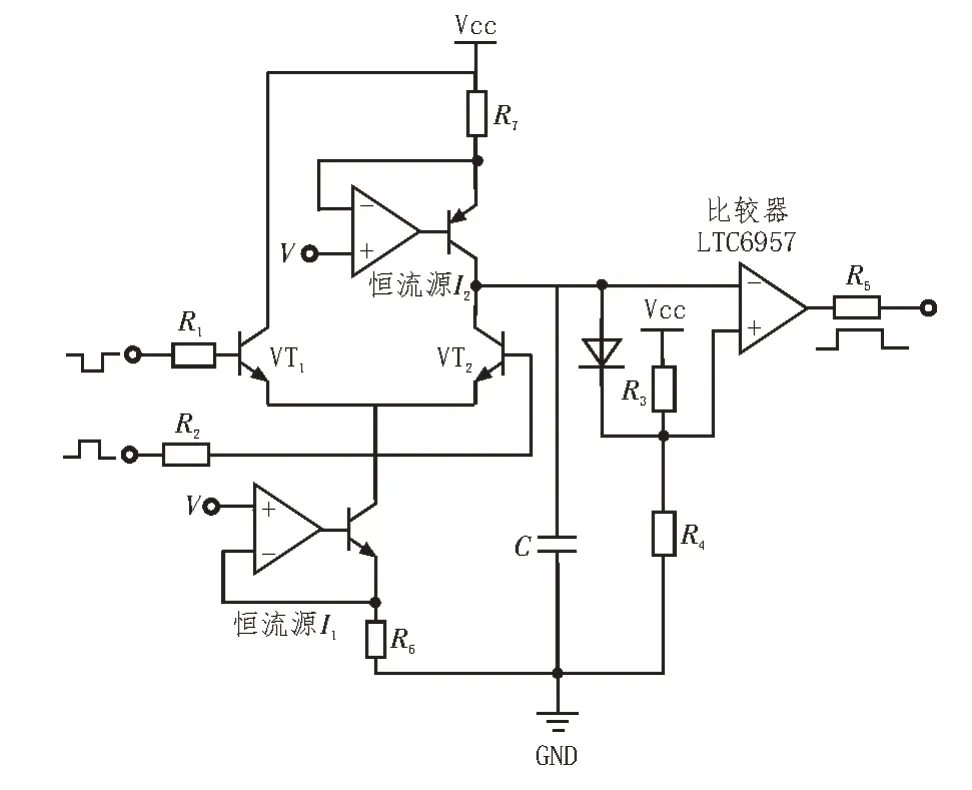

根據雙斜率電容充放電原理,設計的時間展寬電路原理圖如圖3 所示。

圖3 時間展寬電路原理圖

由圖3 可知,I1和I2是兩個單極性恒流源,根據雙斜率電容充放電原理可知I1=KI2,K為時間展寬倍數。用兩個NPN 型三級管VT1和VT2組成高速電流開關,控制電容C的充放電,電阻R3和R4分壓來產生比較器的參考電壓。當信號觸發之前,電路處于靜止狀態,VT1管導通,VT2管截止,恒流源I2對電容C充電至穩定狀態,此時電容C兩端的電壓為參考電壓。當脈沖信號到來后,高速開關VT1截止,VT2導通,此時電容C通過恒流源I1快速放電,雖然此時恒流源I2仍然會用小電流對電容C進行緩慢充電,但是恒流源I1遠大于I2,因此I2對電容C的充電行為基本可以忽略不計。當脈沖信號消失后,VT1管導通,VT2管截止,恒流源I2對電容C緩慢充電,直到電容C兩端的電壓等于參考電壓,也就是與靜止狀態時電容C兩端的電壓相等,此時電路再次達到靜止狀態并且等待下一個觸發信號的到來[14]。電容快速放電時,電容C兩端電壓小于參考電壓,比較器輸出為高;電容慢速充電時,電容C兩端的電壓大于參考電壓,比較器輸出為低。時間展寬過程完成后比較器輸出一個微秒級的脈沖信號,以T2來表示,實現了對納秒級時鐘信號T1的展寬。

由電荷守恒定理可得,電流I1、I2和時間T1、T2之間的對應關系為:

將I1=KI2代入式(1),得:

由式(2)可知,電容C的充電時間是放電時間的K倍。將展寬后的脈沖T2送入FPGA 進行時間測量。FPGA 通過系統時鐘脈沖計數以實現時間測量,設FPGA 的系統時鐘頻率為fs,T1時間內的系統時鐘的脈沖計數為M,得到,代入式(2)計算得到待擴展時間間隔T1為:

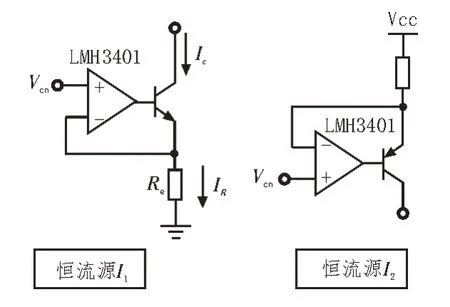

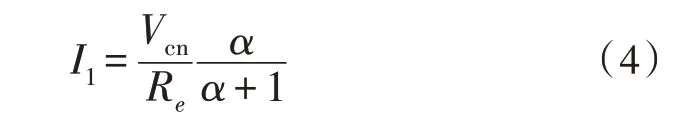

圖3 中的恒流源電路如圖4 所示,可得其電流大小為:

圖4 恒流源電路

其中,α為三極管電流放大系數,Vcn為運算放大器同相端參考電壓,已知電容公式為:

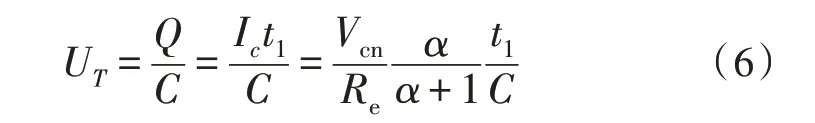

將式(1)、(4)代入電容公式(5)可得;

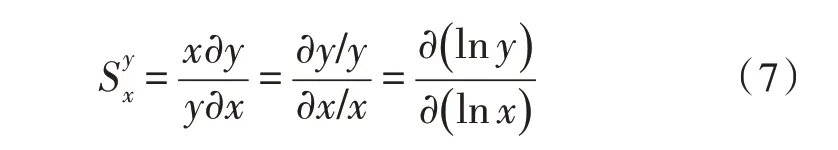

電路性能參數y對元件相關參數x的靈敏度定義為:

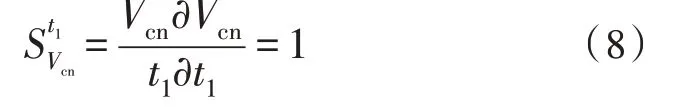

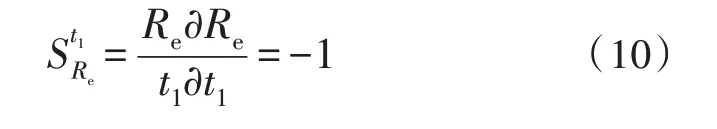

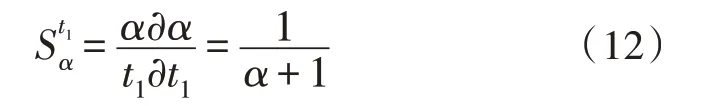

式(7)反映了元件參數的相對變化量對電路性能參數相對變化量的影響,元件參數x可以是元件本身參數或影響元件參數的環境溫度、濕度、壓力等[15]。由圖3 可知,門閥電壓VT、電壓Vcn、電阻Re、電容C、三極管電流放大系數α都會對電路性能產生影響,分別求得展寬時間T1與上述影響電路性能參數的靈敏度。

電壓Vcn的靈敏度為:

門閥電壓VT的靈敏度為:

電阻Re的靈敏度為:

電容C的靈敏度為:

三極管電流放大系數α的靈敏度為:

由式(8)~(12)可知,此電路展寬電路中電壓Vcn、門閥電壓VT、電阻Re,電容C、三極管電流放大系數α對時間展寬電路測量精度影響大,即元件參數變化將會使電路性能發生較大改變。

3 時間展寬電路校正方法

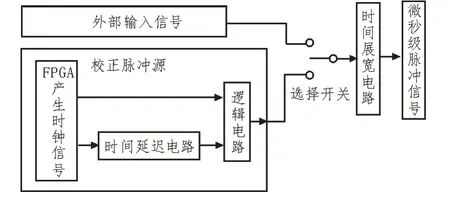

該文通過設計一個校正脈沖源對時間展寬電路進行校正[16],原理框圖如圖5 所示。

圖5 時間展寬電路校正原理框圖

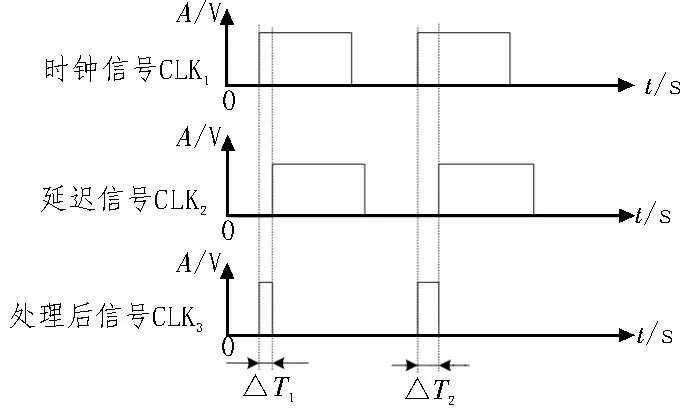

圖5 工作原理:在對外部信號進行采樣之前,使用一個時間寬度可變的納秒級脈沖源作為標準輸入對時間展寬電路進行校正,該脈沖源采用時間延遲原理設計,首先由FPGA 產生時鐘脈沖CLK1,再使用可編程延遲芯片MC100EP195 對時鐘脈沖CLK1進行時間延遲得到CLK2,然后采用高速可編程邏輯芯片HMC722LP3E 對兩種時鐘脈沖進行邏輯運算,最終得到一個納秒級脈沖CLK3,校正脈沖源時序圖如圖6 所示。

圖6 校正脈沖源時序圖

圖6中ΔT1、ΔT2為可編程延遲芯片MC100EP195的延遲時間,延遲時間寬度可以通過編程進行控制,從而得到不同時間寬度的納秒級窄脈沖,將該時鐘源產生的不同時間寬度的窄脈沖作為時間展寬電路輸入,使用FPGA 對時間展寬電路輸出的微秒級時間脈沖進行計數,得到時間寬度T1與FPGA 系統脈沖計數M數據表。完成校正后,時間展寬電路輸入端切換至外部輸入,外部脈沖經過時間展寬電路展寬為微秒級脈沖T2,通過FPGA 對T2進行測量,最后查詢T1與計數M數據表得到時間展寬前的時間間隔T1。其中FPGA系統頻率為200 MHz,時間展寬系數K為50。

4 時間展寬電路的校正方法驗證

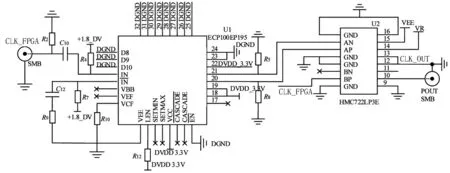

圖5中的校正脈沖源電路圖如圖7 所示。為了驗證溫度變化對電路參數的影響,采用更改積分電容容值的方式,來模擬時間展寬電路元件受溫度變化的影響,溫度升高,積分電容容值上升;溫度下降,積分電容容值下降。分別選用820 pF、1 nF、1.2 nF的積分電容來模擬3 種不同的環境溫度對電路的影響,對3 種不同電容容值的時間展寬電路進行測試,同時與未校正的時間展寬電路性能進行對比測試。

圖7 校正脈沖源電路圖

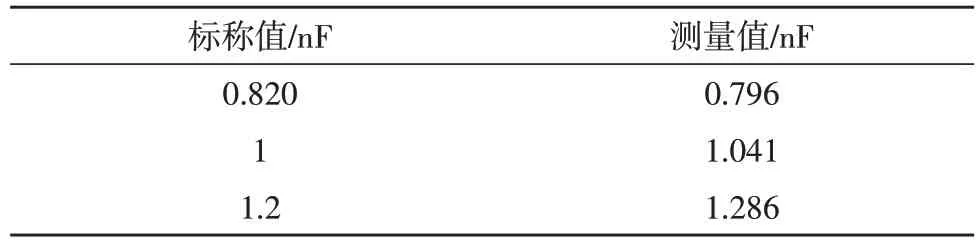

為得到電路中積分電容的實際容值,使用同惠TH2838 數字電橋測量時間展寬電路中的積分電容,3 個電容的測量值如表1 所示。

表1 積分電容測量值

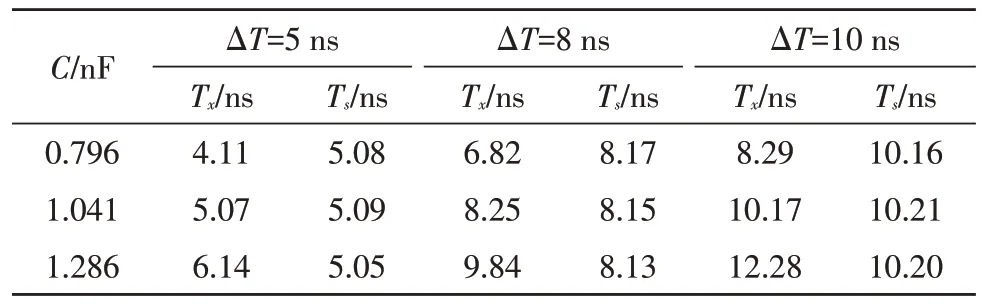

使用Tektronix AFG31152 任意波函數發生器產生寬度為5 ns、8 ns、10 ns 的時鐘脈沖作為時間展寬電路脈沖輸入,分別使用時間展寬電路和DSO90404示波器測量輸出脈沖的時間寬度,將圖5 時間展寬電路連接至外部輸入端,更改積分電容容值,測量并記錄未校正時間寬度數據,實驗結果如表2 所示,表中Tx是使用展寬電路測量的時間寬度數據,Ts是使用示波器測量的標準時間寬度數據。

表2 未校正時間展寬電路時間寬度

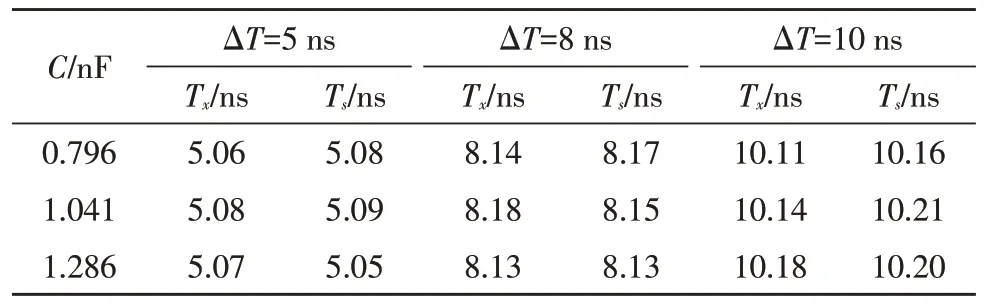

將圖5 時間展寬電路連接至校正脈沖源端,重復上述測試步驟,分別使用上述3 種電容積分電容容值,測量并記錄加入校正電路的時間展寬電路時間寬度,實驗結果如表3 所示。

表3 加入校正電路時間展寬電路時間寬度

對比表2、表3可知,未校正的時間展寬電路測量結果存在較大誤差,誤差大小與電容容值變化量基本一致,而經過校正電路的時間展寬電路中容值變化對時間測量精度基本沒有影響。由表3 的結果可知,經校正后,時間展寬電路所測量的時間差的誤差小于0.1 ns。

5 結束語

該文通過分析探地雷達時間展寬電路,研究了一種時間展寬電路校正方法。該方法在時間展寬電路中加入數值可調的納秒級時鐘脈沖的校正脈沖源,實現對時間展寬電路的校正。采用更改積分電容容值的方式,來驗證時間展寬電路元件參數隨溫度的變化關系,在元件參數發生變化的情況下測量誤差小于0.1 ns,適合于井下探測。