無人機(jī)地空高速調(diào)制解調(diào)器設(shè)計

王利平

(中國電子科技集團(tuán)公司第五十四研究所,河北 石家莊 050081)

0 引言

無人機(jī)(Unmanned Aerial Vehicle,UAV)具有體積小、質(zhì)量輕和使用便捷等特性,作為一種遠(yuǎn)程可操控的航空器,隨著軍事裝備和航空技術(shù)的發(fā)展,在各種方面都發(fā)揮著越來越重要的作用[1]。

隨著UAV平臺搭載傳感器種類和數(shù)量的不斷增多[2]以及聯(lián)合作戰(zhàn)的需要,大容量偵察信息需要及時傳回地面進(jìn)行處理,比如美軍通用戰(zhàn)術(shù)數(shù)據(jù)鏈CDL數(shù)據(jù)傳輸速率達(dá)到了274 Mb/s[3],美軍DirecNet系統(tǒng)最高傳輸速率達(dá)到了1 Gb/s。因此,為了滿足不斷增長的數(shù)據(jù)傳輸需求,迫切需要UAV寬帶數(shù)據(jù)鏈不斷提高數(shù)據(jù)傳輸能力。

高速調(diào)制解調(diào)器在UAV寬帶數(shù)據(jù)鏈中的設(shè)計尤為重要,直接關(guān)系到數(shù)據(jù)傳輸?shù)哪芰Αa槍AV數(shù)據(jù)鏈功率和頻譜資源受限的問題,本文基于軟件無線電技術(shù),設(shè)計了一型高速調(diào)制解調(diào)器,采用幅度與相位相結(jié)合的高階調(diào)制體制,通過并行定時同步、并行載波同步等信號處理方法實(shí)現(xiàn)2.0 Gb/s的高速數(shù)據(jù)傳輸。

1 總體設(shè)計

1.1 系統(tǒng)參數(shù)設(shè)計

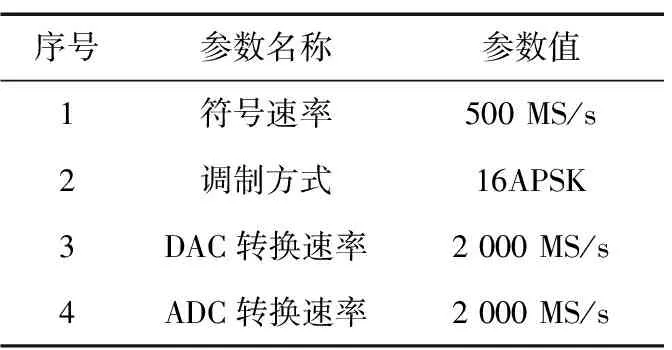

UAV地空高速調(diào)制解調(diào)器主要完成機(jī)載下行高速中頻信號調(diào)制以及地面下行高速中頻信號解調(diào)[4],調(diào)制解調(diào)器主要系統(tǒng)參數(shù)設(shè)計如表1所示,其中,為了提高帶寬利用率,采用16APSK高階調(diào)制,星座圖映射采用DVB-S2建議星座圖[5]。

表1 系統(tǒng)參數(shù)設(shè)計

1.2 信道傳輸幀結(jié)構(gòu)設(shè)計

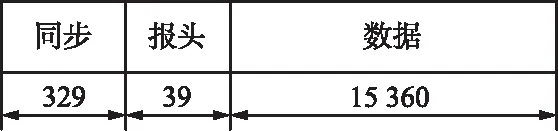

高速調(diào)制解調(diào)器信道傳輸幀結(jié)構(gòu)設(shè)計如圖1所示,同步包含329個符號,其中,幀同步169個符號,由13位Barker碼組成,可用于幀同步;訓(xùn)練序列160個符號,由Frank zadoff序列組成,可用于信道估計;報頭包含39個符號,主要由測距值、空滿標(biāo)識和校驗(yàn)位等組成;數(shù)據(jù)包含15 360個符號,其中有效數(shù)據(jù)12 288個符號。按以上設(shè)計,傳輸幀效率為78.12%。

圖1 信道幀結(jié)構(gòu)Fig.1 Structure of channel frame

2 硬件平臺設(shè)計

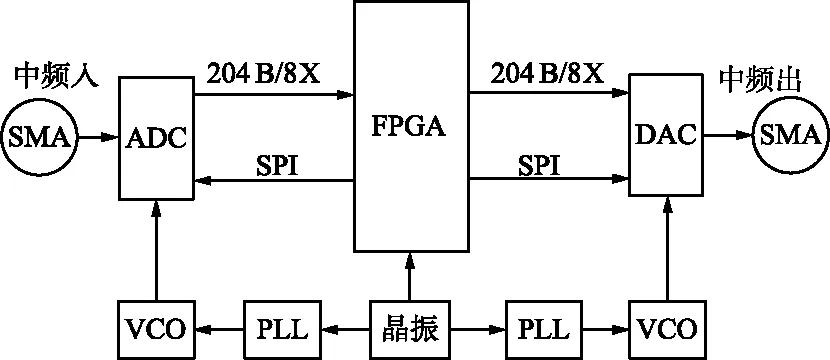

基于軟件無線電思想[6-7],設(shè)計實(shí)現(xiàn)了一種中頻數(shù)字化調(diào)制解調(diào)硬件平臺[8],相比于傳統(tǒng)的零中頻硬件方案,其具有以下優(yōu)點(diǎn)[9]:① 有效降低模擬電路對高速信號的傳輸影響;② 具有理想的I、Q支路平衡特性;③ 直流偏置、本振泄露徹底避免;④ 全數(shù)字化基帶信號處理,軟件升級改進(jìn)便捷。

硬件平臺主要由FPGA,ADC,DAC,時鐘芯片和晶振等組成,硬件原理框圖如圖2所示。

圖2 硬件原理Fig.2 Principle block diagram of hardware

FPGA選用XILINX公司的XC7VX690T-2FFG1927I,該芯片具有專用的JESD204B接口,可以與ADC,DAC無縫銜接;ADC選用TI公司的射頻采樣ADC:ADC12J4000NKE,可直接轉(zhuǎn)換射頻信號,采樣率達(dá)到4 GS/s;DAC選擇ADI公司的AD9164BBCAZ,這是一款高性能16位數(shù)模轉(zhuǎn)換器和直接數(shù)字頻率合成器,支持高達(dá)6 GS/s的更新速率;PLL選擇ADI公司的LMK04828,可完美支持JESD204B協(xié)議;VCO選擇ADI公司的LMX2594,這是一款高性能寬帶合成器,可在不使用內(nèi)部加倍器的情況下生成10 MHz~15 GHz的任何頻率,并且具備非常低的帶內(nèi)噪聲和集成抖動,硬件平臺實(shí)物如圖3所示,尺寸為3U。

經(jīng)實(shí)測,對于2.0 GS/s采樣,本文高速調(diào)制解調(diào)器ADC SFDR指標(biāo)優(yōu)于55 dBFS,DAC SFDR指標(biāo)優(yōu)于58 dBc。

圖3 硬件平臺實(shí)物Fig.3 Physical picture of hardware platform

3 FPGA軟件設(shè)計

3.1 頂層軟件設(shè)計

高速調(diào)制解調(diào)器FPGA軟件包括調(diào)制軟件和解調(diào)軟件兩部分,受FPGA最高處理時鐘的限制,傳統(tǒng)的串行實(shí)現(xiàn)方式無法實(shí)現(xiàn)2 Gb/s的調(diào)制解調(diào),因此必須采用并行處理方案,如并行濾波、并行同步等。本文采用VHDL語言[10]對FPGA調(diào)制解調(diào)軟件進(jìn)行設(shè)計。

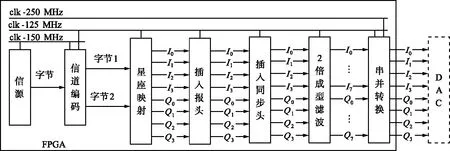

調(diào)制軟件設(shè)計框圖如圖4所示。

信源信息經(jīng)過信道編碼、16APSK相位映射后生成4路并行I、Q信號,插入報頭、同步頭后經(jīng)2倍8路并行匹配濾波輸出8路并行I、Q基帶信號,最后經(jīng)串并轉(zhuǎn)換后輸出至DAC,由DAC完成上變頻和數(shù)模轉(zhuǎn)換。

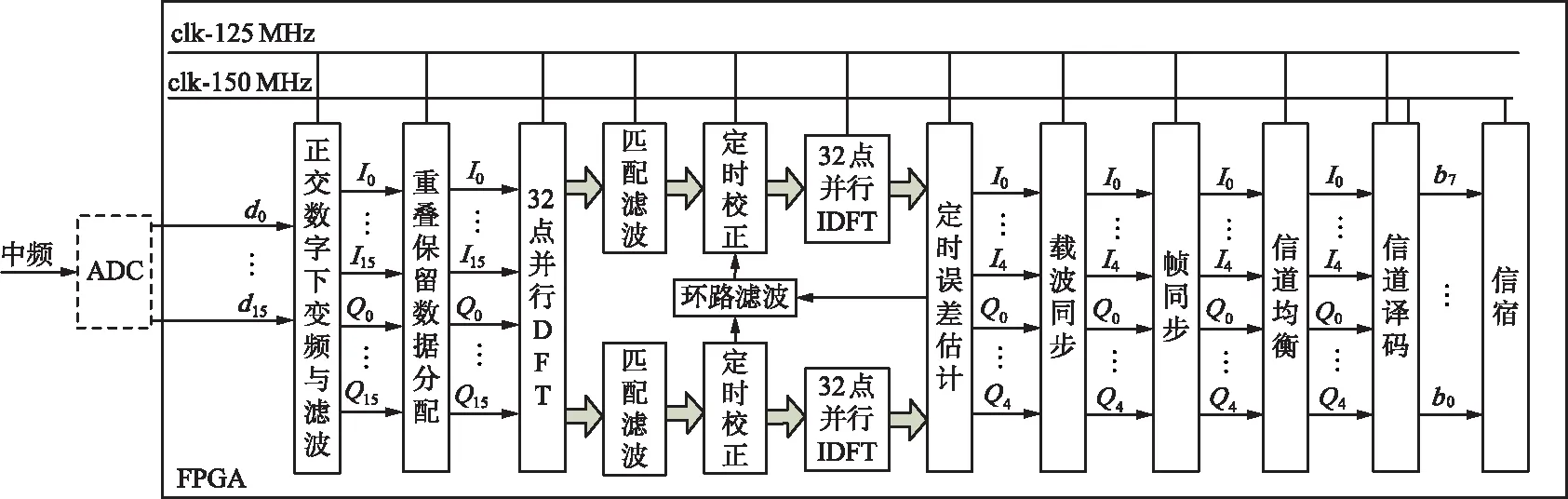

解調(diào)軟件設(shè)計框圖如圖5所示。

圖4 調(diào)制軟件設(shè)計Fig.4 Design block diagram of modulation software

圖5 解調(diào)軟件設(shè)計Fig.5 Design block diagram of demodulation software

具體描述如下:

① 高速ADC以固定2 GS/s采樣率對輸入中頻信號進(jìn)行采樣,并輸出8路并行采樣數(shù)據(jù)給FPGA;

② 在FPGA將8路數(shù)據(jù)進(jìn)行1∶2串并轉(zhuǎn)換輸出16路并行數(shù)據(jù);

③ 對這16路并行數(shù)據(jù)按免混頻結(jié)構(gòu)進(jìn)行奇偶抽取、插零和取反操作,從而實(shí)現(xiàn)正交數(shù)字下變頻;

④ 對步驟③得到的基帶I/Q路數(shù)據(jù)聯(lián)合進(jìn)行32點(diǎn)并行DFT運(yùn)算,然后分別乘以匹配濾波器經(jīng)DFT后的系數(shù)以實(shí)現(xiàn)匹配濾波,再乘以相位旋轉(zhuǎn)因子以實(shí)現(xiàn)定時相位誤差校正,最后分別做32點(diǎn)IDFT,取無混疊數(shù)據(jù)輸出給下一級模塊;

3.2 軟件關(guān)鍵技術(shù)

3.2.1 并行濾波技術(shù)

針對速度需求與現(xiàn)有硬件最高運(yùn)行時鐘有限的矛盾,本文的成型濾波、低通濾波和匹配濾波均采用了并行濾波技術(shù)[11],其中成型濾波、低通濾波采用時域并行FIR濾波,匹配濾波采用頻域并行FIR濾波。

① 時域并行FIR濾波

時域并行FIR濾波主要利用了FIR濾波器抽頭系數(shù)的對稱性,設(shè)輸入序列為x(n),抽頭系數(shù)為h(n),濾波輸出為y(n),則:

(1)

若將輸入信號進(jìn)行L路并行處理,并進(jìn)行相應(yīng)的時延,根據(jù)式(1),可以同時獲得并行L路輸出:

(2)

由此可見,按式(2)進(jìn)行并行處理,可以使濾波處理工作在較低的時鐘速率上,這種方法的本質(zhì)是以資源換取速度。

本文中,成型濾波軟件模塊中L=8,低通濾波軟件模塊中L=16。

會議還邀請了河北省蛋肉雞產(chǎn)業(yè)技術(shù)體系崗位專家、河北省畜牧站污染防治科科長劉雙,河北省獸藥監(jiān)察所研究員王萍,中國農(nóng)業(yè)大學(xué)教授、博士、博士生導(dǎo)師張國中,河北省發(fā)酵工程技術(shù)研究中心副主任、河北科技大學(xué)生物科學(xué)與工程學(xué)院博士劉金龍,伊莎公司中國區(qū)總裁、資深家禽技術(shù)專家尚磊作了精彩的學(xué)術(shù)報告。

② 頻域并行FIR濾波

本文中的匹配濾波采用頻域并行FIR濾波,未采用前文的時域并行方案是由于本文中的定時誤差校正是在頻域完成的,繼而采用頻域?yàn)V波,可以進(jìn)一步降低FPGA乘法器資源使用率。

頻域并行FIR濾波利用了基于傅里葉變換的卷積定理,采用DFT實(shí)現(xiàn)輸入信號與FIR濾波器的卷積運(yùn)算,實(shí)現(xiàn)原理框圖如圖6所示。

圖6 頻域并行FIR濾波軟件設(shè)計框圖Fig.6 Design block diagram of frequency domain parallel FIR filtering software

3.2.2 并行定時同步技術(shù)

在高速傳輸中,收發(fā)參考時鐘的不一致性將導(dǎo)致系統(tǒng)不能正常工作,必須對接收端解調(diào)器匹配濾波器輸出進(jìn)行同步抽樣,即定時同步或時間同步[12-13]。

本文中,定時誤差估計采用文獻(xiàn)[14-15]提出的O&M算法,這是一種無偏估計,相比于經(jīng)典Gardner算法[16-17],其至少需要4倍采樣。O&M算法可以描述為:

假設(shè)匹配濾波后的基帶信號為rk,表示為:

rk=Ik+jQk。

(3)

對rk取包絡(luò)平方得到:

(4)

將xk按每L個符號周期分為一段,則通過DFT變換可得到其第m段數(shù)據(jù)頻譜上的符號速率譜線的譜分量為:

(5)

則此譜分量的歸一化相角就是定時誤差的無偏估計,即:

(6)

取N=4,則式(5)可以表示為:

(7)

顯然,Xm的實(shí)部對應(yīng)偶數(shù)采樣點(diǎn)包絡(luò)平方,虛部對應(yīng)奇數(shù)采樣點(diǎn)包絡(luò)平方,將式(7)按Xm的實(shí)部、虛部分解為:

(8)

(9)

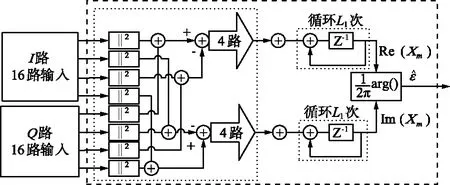

由于在本文中IDFT輸出為16路并行數(shù)據(jù),對應(yīng)4個符號,因此對于L1個符號的累積運(yùn)算,式(8)和式(9)可繼續(xù)分解為:

(10)

(11)

由式(10)和式(11)分解可以得到O&M算法的并行實(shí)現(xiàn)結(jié)構(gòu),如圖7所示。在具體FPGA實(shí)現(xiàn)時,其中的平方運(yùn)算采用硬件乘法器DSP48E1,求相位角采用Xilinx提供的基于Cordic算法的IP核實(shí)現(xiàn)。

圖7 定時誤差估計實(shí)現(xiàn)框圖Fig.7 Implementation block diagram of timing error estimation

3.2.3 并行載波同步技術(shù)

限于FPGA的最高時鐘運(yùn)行速度,傳統(tǒng)的串行載波同步算法難以實(shí)現(xiàn),因此本文采用如圖8所示的并行載波同步結(jié)構(gòu)。

對于定時同步后的符號數(shù)據(jù),首先通過Cordic算法將其由直角坐標(biāo)轉(zhuǎn)換為極坐標(biāo),然后在相位域進(jìn)行頻偏的相偏估計,得到的平均誤差信號經(jīng)過二階環(huán)路濾波和NCO后,再反饋回去做減法,以完成頻偏校正,校正后的信號再通過Cordic算法將其由極坐標(biāo)轉(zhuǎn)換為直角坐標(biāo)得到載波同步后的基帶信號,Cordic利用FPGA自帶IP核實(shí)現(xiàn)。

相偏估計誤差可以表示為[18-19]:

(12)

式中,ek為誤差輸出;ck為定時同步后的復(fù)信號;Θ為環(huán)形區(qū)域內(nèi)的星座點(diǎn)集合;φk為鑒相輸出;λ為誤差閾值,取值為0.1π。

4 性能測試

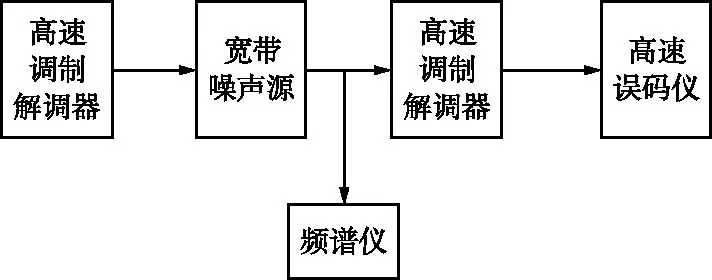

為了充分驗(yàn)證設(shè)計方案的可行性,在實(shí)驗(yàn)室環(huán)境高斯白噪聲信道下對高速調(diào)制解調(diào)器進(jìn)行誤碼性能測試,測試框圖如圖9所示,通過調(diào)節(jié)寬帶噪聲源輸出噪聲強(qiáng)度,獲得不同信噪比下的誤碼性能。解調(diào)性能測試結(jié)果如圖10所示,可以看出,在誤碼率為1×10-5時,解調(diào)損失優(yōu)于2 dB。

圖9 測試框圖Fig.9 Diagram of test

圖10 解調(diào)性能測試曲線Fig.10 Test curve of demodulation performance

5 結(jié)束語

本文基于軟件無線電思想,設(shè)計實(shí)現(xiàn)了一種UAV地空高速調(diào)制解調(diào)器,通過采用JESD204B接口協(xié)議,解決了ADC/DAC與FPGA間的高速數(shù)據(jù)傳輸問題;通過并行信號處理,解決了速度需求與現(xiàn)有FPGA最高運(yùn)行時鐘有限的矛盾。經(jīng)過測試,設(shè)計實(shí)現(xiàn)的高速調(diào)制解調(diào)器可以實(shí)現(xiàn)2.0 GS/s數(shù)據(jù)傳輸速率的16APSK信號的調(diào)制解調(diào),在誤碼率為1×10-5時,解調(diào)損失優(yōu)于2 dB,滿足工程實(shí)際需求。