基于高精度電流源的10 bit電流舵DAC

潘 誠,雷倩倩,高宇飛,于 鵬,馮 松

(1.西安工程大學理學院,陜西西安 710000;2.深圳市紐瑞芯科技有限公司,廣東深圳 518000)

數模轉換器(Digital to Analog Converter,DAC)可以將數字信號轉換為模擬信號,廣泛應用于音視頻信號處理以及網絡通信等領域[1-2]。不同的應用領域對DAC 的性能要求也不同,但由于DAC 的精度決定了所能接收到模擬信號的準確程度,因此,精度成為了研究的重點。目前,高精度DAC 的主流架構有Sigma-Delta 型和電流舵型兩種,Sigma-Delta 型DAC擁有很高的精度,但所處理的信號頻率較低,適用于低頻率的音頻處理[3];電流舵型DAC 擁有速度快、對寄生參數不敏感等優點,被廣泛應用于通信領域[4]。在傳統的電流舵DAC 中,電流源單元使用共源共柵電流源來實現,為了達到高精度,所用MOS 管的尺寸都很大,從而導致版圖面積過大[5]。文中采用阻抗增強型共源共柵電流源,在確保性能的前提下,極大地減小了電流源陣列的面積。

1 電路設計與分析

1.1 DAC整體架構

所設計的DAC 整體電路結構如圖1 所示,包括譯碼器、同步時鐘、開關陣列、電流源陣列4 部分。DAC 使用分段式電流舵結構[4],高6 位采用溫度計碼控制電流源單元,低4 位采用二進制碼控制電流源單元,這樣既可以避免DAC 最高位(Most Significant Bit,MSB)和最低位(Least Significant Bit,LSB)分別控制的輸出電流值相差較大,導致DAC 的線性度變差,又可以避免引入過多的電流源單元,導致版圖面積變大[6-7]。譯碼器將輸入的高6 位二進制碼轉換為63 位溫度計碼,同步時鐘控制高63 位溫度計碼和低4 位二進制碼同時到達開關陣列,以避免輸入碼的不同步導致開關提前導通,對DAC的整體性能造成影響。根據不同的控制字輸入來控制差分開關管Kia、Kib(i=1,2,…,67)的導通和關斷,以此分配差分輸出支路的總電流,并通過負載電阻R將電流轉換為電壓輸出,實現數字信號到模擬信號的轉換。

圖1 DAC系統框圖

1.2 電流源單元的分析與設計

電流源單元是電流舵型DAC 的核心電路,其性能的好壞對DAC 電路的靜態性能有著重要的影響。電流舵型DAC 的積分非線性(Idaho National Laboratory,INL)和無雜散動態范圍(Spurious-Free Dynamic Range,SFDR)的表達式分別為式(1)和式(2)[8],RL為負載電阻,R0為電流源單元的輸出阻抗,N為電流源單元個數。從式(1)、(2)可以看出,INL和SFDR都與R0有關,R0越大,DAC的INL越小,SFDR越大。

因此,DAC 中常采用共源共柵結構以實現大的輸出阻抗,如圖2(a)所示,當兩個NMOS 管都處于飽和區時,輸出阻抗表達式為:

圖2 電流源單元結構

其中,gm1為NMOS1 管的跨導,gmb1為襯偏跨導,ro1、ro2是NMOS1 和NMOS2 的體電阻,共源共柵結構輸出阻抗提升至共源極結構的(gm1+gmb1)ro1倍[9],提升了DAC 的線性度。但根據式(3)可知,電流源的Rout1和管子的柵長成正比,要想增大Rout1,需要增大管子的柵長,從而使版圖面積增加。為了減小版圖面積并保持大的輸出阻抗,文中在電流舵DAC 中引入了阻抗增強型共源共柵結構,如圖2(b)所示。式(4)給出了阻抗增強型共源共柵結構的輸出阻抗,其中,體電阻ro1、ro2較小,因此可以近似認為Rout2比Rout1增大了1+AV倍。文中所設計的阻抗增強型共源共柵電流源陣列電路如圖3 所示,通過在電流源陣列中引入運放,從而提高整體的輸出阻抗。

圖3 阻抗增強型電流源陣列

運放的輸入B 端連接電流源陣列中共源管的漏端,輸出端連接電流源陣列中共柵管的柵端。通過改變偏置電壓Vbias,可以調節B 端和A 端電壓,合理分配Mai、Mbi(1,2,…,67)的過驅動電壓,以得到使所有MOS 管穩定工作在飽和區的最小電壓。

1.3 DAC誤差來源及電流源尺寸設計

所設計的DAC 誤差主要來源于系統誤差和隨機誤差。系統性誤差可以通過調整電流源陣列的版圖布局來減小,而隨機性誤差與MOS 管的尺寸和面積相關。式(5)~(7)分別給出了隨機性失配誤差、微分非線性誤差(Differential Nonlinearity,DNL)和單位電流源面積的關系[10-14]。

2 仿真結果及分析

采用SMIC 28 nm CMOS 工藝,利用Cadence Virtuoso 軟件對DAC進行了仿真,DAC的輸入信號由理想ADC 的輸出替代,將仿真數據導入Verilog A描述的Bench 中處理,得到結果如圖4 所示。

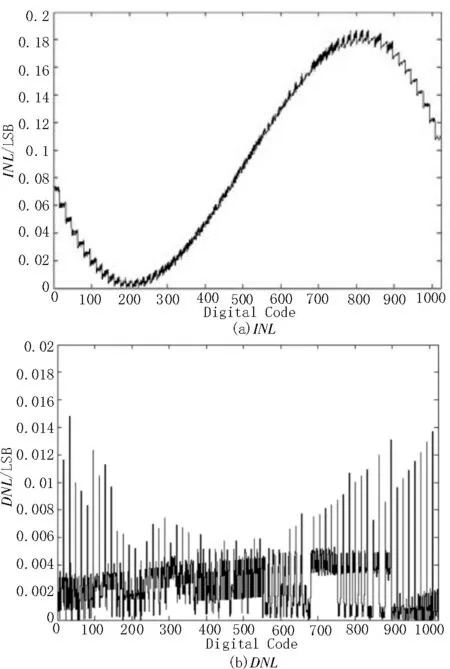

圖4 共源共柵結構仿真結果

采用共源共柵結構作電流源時,電路的DNL最大值為0.016 LSB,INL最大值不超過0.200 LSB。如圖5 所示,當引入阻抗增強型共源共柵結構時,DNL最大值為0.01 LSB,INL最大值不超過0.06 LSB。由式(1)可知,傳統共源共柵電流源結構面積至少需增加3 倍才能達到文中所實現的精度。

圖5 阻抗增強型共源共柵結構仿真結果

如圖6所示,當輸入信號頻率為1.087 5 MHz,采樣速率為38.4 MS/s時,DAC的無雜散動態范圍是65.3 dB。表1 是文中設計與其他電流舵型DAC 的性能對比,與傳統較大工藝尺寸下的電流舵DAC 相比,文中設計在較小的功耗下,可以實現更好的精度;在相同工藝尺寸下,面積減小為傳統工藝尺寸的。

表1 性能指標對比

圖6 SFDR

3 結論

文中基于SMIC 28 nm CMOS 工藝,設計了一個10 bit 250 MS/s 的DAC。電源電壓0.9 V,滿偏電流1.03 mA,使用Candence Virtuoso 軟件進行設計和仿真,仿真結果顯示,DAC 的INL最大值不超過0.06 LSB,DNL最大值不超過0.01 LSB,當輸入信號為1.087 5 MHz,采樣速率為38.4 MS/s 時,無雜散動態范圍為65.3 dB。