GaN-LED倒裝芯片的金屬保護層設計與研究

吳瀅瀅

(廈門三安光電科技有限公司,福建 廈門 361009)

0 引言

GaN-LED 倒裝芯片(Flip Chip)因無須通過藍寶石散熱,散熱性能好,壽命較長,同時因不像常規正裝芯片需要考慮P 層上導電層(目前主要采用氧化銦錫材料)透光性問題,所以可以設計采用電阻率更低、反射率更高的金屬材料為反光層Mirror,以使芯片得到更低的電壓,亮度也可得到更大提升,并使封裝采用更大電流驅動,光效更好。因其需要打線封裝,所以可減少因金線損壞導致的死燈概率,且便于封裝集成化。綜上所述,車燈、mini 顯示屏等更高端市場更愿意使用倒裝芯片。但其采用的金屬材料為電阻率更低、反射率更高的銀,銀因自身的金屬特性,在一定條件下容易發生金屬遷移[1-2]而導致電性出現異常,進而死燈,所以在一般情況下,是通過在銀表面加一層金屬保護層Barrier 來阻隔,可是這種辦法仍然無法解決Ag 從保護層側面析出,通過各種介質從P 電極向N 電極遷移,形成導電通道,進而導致漏電的問題。該文研究設計了不同保護層,提出了雙層夾層的金屬保護層,結構更穩定,致密性更佳,可以有效減少側面Ag 析出,降低漏電異常率,并同時增加光萃取率以提亮。

1 試驗

利用金屬有機氣相外延(MOCVD)機臺K456I,在4寸藍寶石襯底上生長藍光LED 外延結構(分別生長GaN 緩沖層、N 型層n-GaN、多對量子阱InGaN/GaN、電子阻擋層p-AlGaN 和P 型層p-GaN),并進行發光二極管的倒裝芯片前期基礎工序(在長完的外延片上,先用有機清洗液和酸洗對外延表面進行清潔處理,去除外延表面的臟污、顆粒,然后通過黃光上膠曝光顯影硬化等工序,光刻膠保護住不需要被ICP 刻蝕的區域,在發光區按照一定的陣列均勻地刻蝕出N 電極溝槽以形成mesa 平臺,使后續通電時電流擴展得更均勻,減少電流擁擠。再通過黃光上膠曝光顯影硬化等工序和ICP 刻蝕方式,將每顆芯粒走道的外延層的P 型層和N 型層完全去除,用有機清洗液和酸洗對外延表面進行清潔處理,通過磁控濺射的方式鍍上氧化銦錫ITO 并快速ITO 退火,形成P 歐姆接觸層。最后通過黃光上膠曝光顯影硬化等工序,光刻膠保護住不需要被ITO 蝕刻掉的區域,用ITO 蝕刻液蝕刻掉N 電極區域的氧化銦錫ITO,將已經做好前期基礎工藝的試驗片分成2 組,分別做A 設計方案和B 設計方案。

A 保護層設計方案:工序1,在已經做過一段基礎工序的外延片上長一層絕緣層,長前用有機清洗液和酸洗對外延表面進行清潔處理;工序2,通過黃光上膠曝光顯影硬化等工序,光刻膠保護不需要鍍上反光層銀的絕緣層;工序3,用BOE 溶液蝕刻掉未被光刻膠保護的絕緣層區域,需要注意待蝕刻區域表面是否有光刻膠殘留,避免蝕刻不干凈;工序4,以磁控濺射的方式鍍上反光層銀層,銀較活潑,在本次鍍膜中,除鍍上銀層外,還要鍍上薄薄的金屬保護層;工序5,將鍍完反光層銀片源吸真空固定在剝離機上,用白膜黏除光刻膠上的反光層銀后,去除黃光光刻膠;工序6,通過黃光上膠曝光顯影硬化等工序,光刻膠保護不需要鍍上金屬保護層的絕緣層;工序7,用BOE 溶液蝕刻掉未被光刻膠保護的絕緣層區域,需要注意待蝕刻區域是否表面有光刻膠殘留,避免蝕刻不干凈;工序8,以電子束真空蒸鍍方式鍍上金屬保護層;工序9,將鍍完金屬保護層的片源吸真空固定在剝離機上,用白膜黏除光刻膠上的金屬保護層,去除黃光光刻膠。A 設計方案示意圖如圖1 所示。

圖1 A 設計方案

B 保護層設計方案:工序1,在已經做過一段基礎工序的外延片上長一層絕緣層,長前用有機清洗液和酸洗對外延表面進行清潔處理;工序2,通過黃光上膠曝光顯影硬化等工序,光刻膠保護不需要鍍上反光層銀的絕緣層;工序3,用BOE 溶液蝕刻掉未被光刻膠保護的絕緣層區域,需要注意待蝕刻區域表面是否有光刻膠殘留,避免蝕刻不干凈;工序4,以磁控濺射的方式鍍上反光層銀層,銀較活潑,在本次鍍膜中,除鍍上銀層外,還要鍍上薄薄的金屬保護層;工序5,將鍍完反光層銀片源吸真空固定在剝離機上,用白膜黏除光刻膠上的反光層銀后,去除黃光光刻膠;工序6,通過黃光上膠曝光顯影硬化等工序,光刻膠保護不需要鍍上金屬保護層的絕緣層;工序7,以電子束真空蒸鍍方式鍍上金屬保護層;工序8,將鍍完金屬保護層的片源吸真空固定在剝離機上,用白膜黏除光刻膠上的金屬保護層,去除黃光光刻膠。B 設計方案示意圖如圖2 所示。

圖2 B 設計方案

將發光二極管器件繼續制作完成(在A、B 設計方案均完成的工序上,采用等離子增強化學氣相沉積PECVD 方式沉積絕緣層;通過黃光上膠曝光顯影硬化等工序,光刻膠保護不需要被去除的絕緣層的區域;用BOE 溶液蝕刻或者ICP 刻蝕掉未被光刻膠保護的絕緣層區域,絕緣層覆蓋各N電極溝槽、mesa 平臺、切割道、反光層的金屬保護層;通過黃光上膠曝光顯影硬化等工序和電子束真空蒸鍍方式,形成整面的N 金屬電極區域;再通過等離子增強化學氣相沉積PECVD 方式沉積一層絕緣層,通過黃光上膠曝光顯影硬化等工序和BOE 溶液蝕刻或者ICP 刻蝕,分別隔離出P 導電通道和N 導電通道;制作分別覆蓋各P 導電通道和各N 導電通道的P 焊墊和N 焊墊),以進一步對比2 種不同保護層設計對發光二極管的結構形貌、芯片漏電良率、芯片亮度、封裝亮度的影響差異。

2 結構形貌

從上述2 種不同保護層設計方案流程差異可以看出,A設計方案中,反光層銀完全由金屬保護層覆蓋保護,該金屬保護層采用電子束真空蒸鍍原理鍍膜,用一束電子轟擊金屬材料,產生高能量,使金屬材料沸騰后蒸發并沉積到片源表面,生長機理簡單,但是形成的薄膜黏附能力較差,無法形成致密的阻隔膜,再加上金屬保護層側面比較薄,包覆性不夠。A 設計方案的結構形貌如圖3 所示。

圖3 A 設計方案的結構形貌

在后期使用過程中,側面容易被水汽或者空氣中的有害小分子等滲入,造成銀遷移過程中銀離子的大面積形成。當芯片設計中其他應力較大的絕緣層出現斷裂時,會發生銀遷移,進而使LED 芯片的正、負電極導通,引起漏電。B 設計方案中,反光層銀由側壁的絕緣層和金屬保護層雙層夾層保護,絕緣層采用等離子增強化學氣相沉積(PECVD)方式鍍膜,借助微波或射頻等使含有薄膜組成原子的氣體電離,在局部形成等離子體。氣體經一系列化學反應和等離子體反應,在片源表面形成固態薄膜。此方式形成的膜層純度和致密性較高,且該材料具有超強的黏附力。B 設計方案的結構形貌如圖4 所示。

圖4 B 設計方案的結構形貌

這種絕緣層和金屬保護層雙層夾層保護方式因絕緣本身穩定性更高、致密性較好、黏附力超強且不導電,能使銀遷移路徑在經過側壁絕緣層時發生變化,可以有效阻擋金屬銀的遷移,減少漏電的發生。

3 LED 光電參數測試

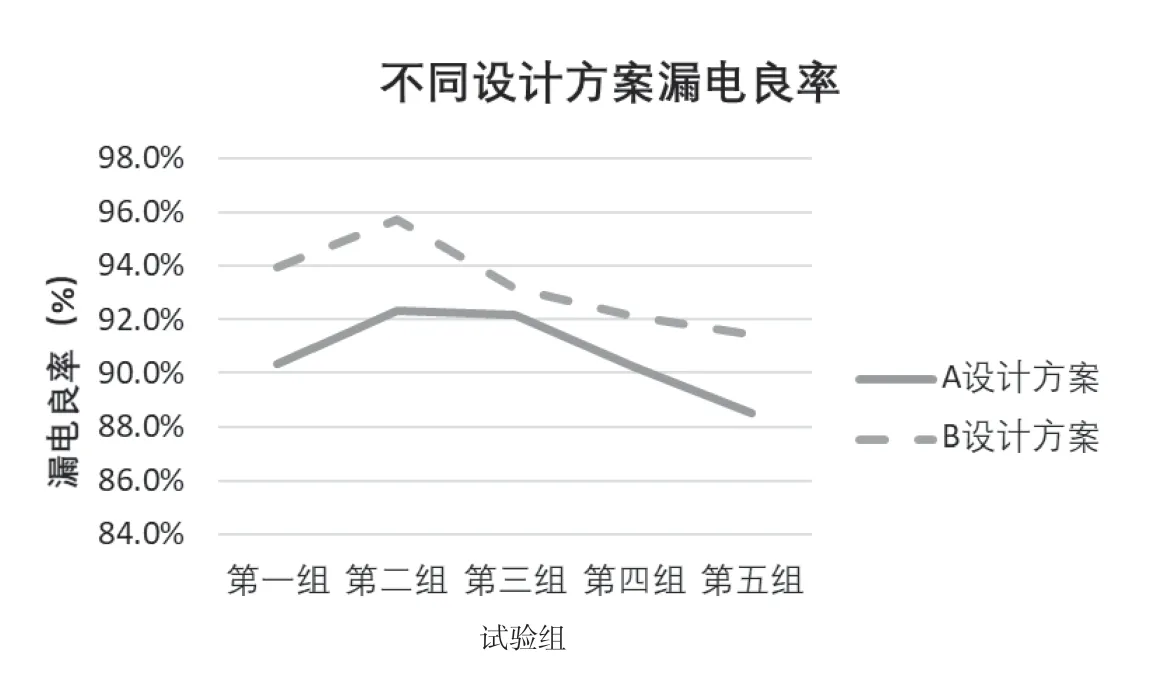

GaN 外延片分別按照A、B 設計方案,制成完整的發光二極管,刻蝕按照一定的陣列均勻地刻蝕出N 電極溝槽以形成mesa 平臺,鍍上氧化銦錫ITO 并快速ITO 退火形成P歐姆接觸層,鍍上反光層銀、金屬保護層,制作覆蓋各N電極溝槽、mesa 平臺、切割道、反光層銀的絕緣層,圖形化隔離層以形成P 導電通道和N 導電通道,制作分別覆蓋各P 導電通道和各N 導電通道的P 焊墊和N 焊墊,并制作成3 000 μm×3 000 μm 的發光二極管,芯片是倒裝結構的芯片。在矽電LED 倒裝探針臺搭載維明測試機上,點測電流350 mA,反向電壓5V,進一步分別測試A、B 設計方案的芯片漏電良率和亮度的光電參數差異。從芯片的漏電良率結果上看,B 設計方案的漏電良率比A 設計方案高出2.6%,說明B 設計方案因絕緣層鍍膜方式為等離子增強化學氣相沉積(PECVD),而比金屬的電子束真空蒸鍍原理穩定性更高、致密性較好、黏附力超強,而且絕緣層和金屬保護層雙層夾層的復合保護結構設計可以使銀遷移路徑在經過側壁絕緣層時發生變化,減少水汽或者空氣中有害小分子等滲入造成銀遷移過程中銀離子的大面積形成,并減少反光層銀的金屬遷移。2 種不同設計的漏電良率比對差異如圖5所示。

圖5 2 種不同設計漏電良率差異

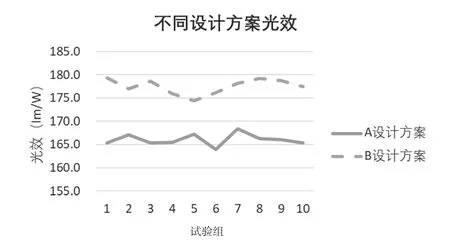

可以觀察到B 設計方案的亮度比A 設計方案高出4.5%,這是因為光線的全反射損失大大降低,增加的絕緣層材料折射率介于外延氮化鎵和復合折射率的金屬保護層之間,進而行成了具有更高反射率的全方向反射鏡[3],使本來會被局限在發光二極管內部的光更容易被萃取出來,亮度得以提升,器件的過載驅動能力愛更強。2 種不同設計亮度比對如圖6所示。

圖6 2 種不同設計亮度差異

將2 種不同設計方案的芯片分別封裝到C3535 基板上,進一步確認封裝成成品的提亮效果,封裝后的光效差異如圖7 所示。從結果上看,在點測電流350 mA 下,B 設計方案的光效比A 設計方案高出10 lm/W,光效提升5%,與芯片在探針臺上點測比對結果提亮4.5%基本一致。在提升漏電良率2.6%的同時,因為絕緣層和金屬保護層雙層夾層的復合保護結構設計,B 設計方案形成了高反射率的反射鏡,亮度得到提升,可以用更低的電流驅動得到同樣的光效,減少了散熱,提升了芯片壽命。

圖7 封裝后測試光效差異

4 結論

為解決反光層銀析出的問題,提升芯片制程中的漏電良率,該研究設計了不同金屬保護層結構,通過對比結構形貌、芯片漏電良率、芯片亮度和封裝亮度,證明了雙層夾層的復合結構的金屬保護層設計結構更穩定,致密性更佳,可以有效阻擋金屬銀的遷移,減少PN 結的導電通道,降低漏電的風險。從探針臺點測結果看,雙層夾層的金屬保護層漏電良率提升了2.6%,進而提升了倒裝芯片設計的良率,減少了成本損失,提升了產品競爭力。同時雙層夾層的復合金屬保護層結構設計因形成了全方向反射鏡,使本來會被局限在發光二極管內部的光更容易被萃取出來,在點測電流350 mA下,亮度提升了4.5%。雙層夾層金屬保護層結構的引入使用,可以用更低的電流驅動得到同樣的亮度,可減少散熱,提升芯片壽命。