基于國產化通用VPX的信號處理板設計

王錫志

摘要:針對當前國家信息化設備的快速發展和國產化的不斷推進,結合當前國產芯片發展現狀。結合VPX總線架構發展現狀,通過開展高速總線互聯技術的研究,將二者結合。以國產芯片為基礎,完成了基于國產化通用VPX信號處理板的設計。對各功能電路進行了詳細闡述,并對主要國產芯片系統進行了介紹。通過硬件平臺的開發,在自主化硬件設計、軟件適配及VPX總線架構等方面積累經驗,為裝備實現國產化國產化提供技術支撐。

關鍵詞:國產化;VPX;DSP;FPGA

中圖分類號:TN919.3文獻標志碼:A文章編號:1008-1739(2022)01-52-4

0引言

在我國信息設備建設國產化持續推進下,在提倡創新和自主發展的大背景下,為了行業長遠和健康發展,必須在芯片領域堅持自主研發和應用[1]。

隨著通信對抗專業領域的技術發展,作戰目標多樣化、應用場景多元化。對多信號、多功能并行處理能力的設備需求逐步增多,對寬帶高速處理與窄帶高精度處理的需求在逐步增多,傳統的并行總線已不能滿足設備需求。VPX總線作為新一代的高速串行總線,采用了高速串行Rapid IO、PCIe等高性能接口,更加適應現代通信對抗領域對功能繁多、運算復雜、數據量大及高速實時處理的要求[2]。

本文結合目前國產化元器件現狀和技術發展需求,對國產化元器件和VPX架構的應用進行研究和探索,設計了一款基于國產芯片的VPX架構信號處理板,詳細說明各個功能模塊的設計與實現,在自主化硬件設計及VPX總線架構等方面積累經驗,為國產化國產化提供技術支撐。

1設計原理

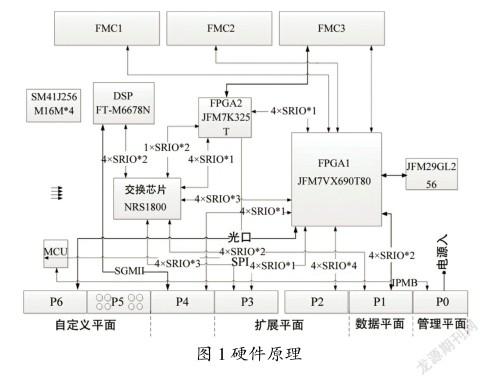

信號處理板采用VPX總線標準的6U尺寸設計,符合Vita46/Vita48規范,采用DSP+FPGA+FMC架構。按照功能設計將接口劃分為管理平面、數據平面、擴展平面、控制平面和自定義平面。板卡融合了IPMC管理、SIRO交換、高速串行總線、通用多核DSP和FPGA等。管理平面用于板卡硬件信息的管理和監控,采用雙I2C的IPMB總線實現。數據平面支持模塊間高速數據傳輸,采用4x SRIO接口作為數據總線,支持主/備模塊間互連。擴展平面為相鄰2個處理模塊提供收發雙向8個通道端口互連。控制平面要求高可靠性,采用SGMII接口作為控制總線,支持1000Base-T。自定義平面用于外部物理接口,可接射頻電纜和光纖等。硬件原理如圖1所示。

2硬件實現

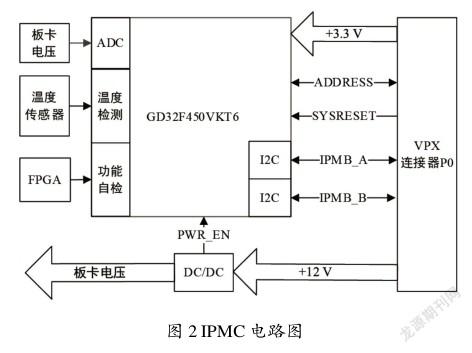

2.1 IPMC設計

IPMC電路圖如圖2所示[3]。IPMC主控芯片由兆易創新的GD32F450VKT6來實現。該芯片是一款國產MCU處理器,時鐘主頻200 MHz,芯片內集成了3 072 Kbytes的片上閃存和512 Kbytes的SRAM內存,同時提供12通道ADC。通過兩路I2C總線與背板的IPMB_A,IPMB_B連接。IPMC電路采用獨立的+3.3 V_AUX供電。MCU可以實現板卡上電、重啟、電壓檢測、功能自檢及故障信息上報等功能。

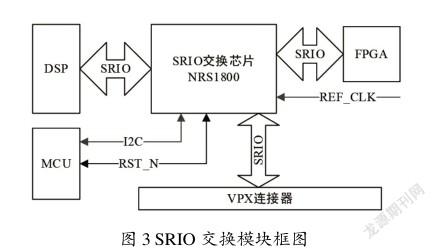

2.2 SRIO交換模塊設計

SRIO交換芯片選用的NRS1800,該芯片具有48個雙向的數據差分對(Lane),可以配置成1x,2x,4x三種端口模式,最多可以配置成18個1x或12個4x端口,每個lane的速率可選擇1.25 Gbit/s,2.5 Gbit/s,3.125Gbit/s,5 Gbit/s,6.25 Gbit/s。NRS1800還有一個標準I2C接口,該接口可以用來完成對芯片的初始化配置,也可以通過I2C讀取NRS1800內部寄存器來獲取芯片的工作狀態。NRS1800可應用于大型處理器集群或背板,支持多種SRIO網絡拓撲結構,可以采用靈活的方式進行配置,可選的配置方案也非常豐富。SRIO交換模塊如圖3所示。

NRS1800的復位引腳RST_N用于全局復位,使所有寄存器恢復到上電默認狀態,該引腳接入MCU芯片。RST_N信號需要低電平持續最少5個REF_CLK周期,復位完成后可通過I2C/JTAG對芯片進行配置。

NRS1800的I2C接口符合I2C協議規范,芯片可以作為從設備和臨時主設備。MM_N引腳決定上電復位后I2C接口是主模式還是從模式。連接到GND為臨時主模式,上拉至3.3 V為從模式。ADS引腳決定從模式下I2C設備地址寬度,連接到3.3 V為10 bit地址,連接到GND為7 bit地址。ID9~ID0引腳為I2C從模式下地址信號。

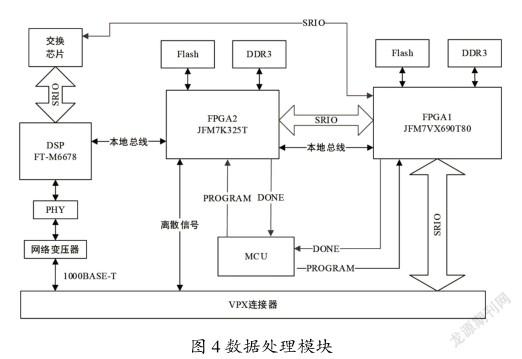

2.3數據處理模塊設計

數據處理模塊主要由FPGA和DSP組成,組成如圖4所示。

FPGA選取復旦微電子7系列JFM7K325T和JFM7VX690T80。2款FPGA沿襲了Xilinx發展路線,如配置方法、時鐘接口、電源的接法與Xilinx對應產品完全一致。JFM7K325T主要用來完成本地總線轉換、離散信號控制以系統中各模塊間I/O時序控制,可用于對另一片FPGA的程序在線更新,實現功能重構技術。JFM7VX690T80實現數據串并轉換以及對AD采集的中頻信號進行數字下變頻、FFT等處理功能。外接DDR3存儲器實現數據緩存。FPGA的控制引腳接入MCU芯片,可配置程序從Flash中重新加載。國產FPGA資源列表如表1所示。

DSP芯片選取FT-M6678,該款芯片是一款高性能浮點/定點數字信號處理器,可滿足多種實時信號處理的需要。含有8顆FT-M66x DSP內核,每個內核工作主頻為1 GHz。定點運算性能為32 GMACs,浮點運算性能為16 GMACs。有2組SIRO串行總線,每組可配置成1x,2x,4x模式,每Lane傳輸速率支持1.25 Gbit/s,2.5 Gbit/s,3.125 Gbit/s。除此之外,FT-M6678還有一個SGMII以太網接口,支持支持1000Mbps、100 Mbps,10 Mbps傳輸。可外接64位DDR3存儲器,最大尋址空間8 GB。FT-M6678總體結構如圖5所示。

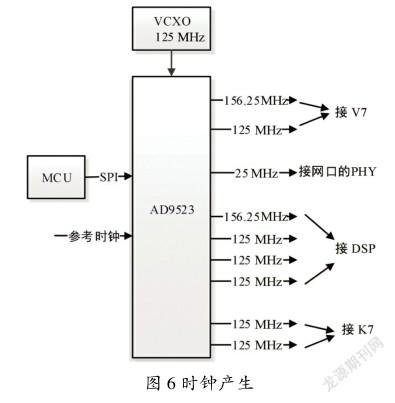

2.4時鐘模塊設計

信號處理板上用到的時鐘非常多,而且頻率各不相同,有差分時鐘和單端時鐘。時鐘設計的目標就是用最簡單的方案實現板卡上所有器件的時鐘需求,以減少電路面積,增加可靠性。本設計選取了1片AD9523時鐘芯片,該芯片可以通過編程,由MCU控制,產生信號處理板上所需要的時鐘。時鐘產生如圖6所示。

2.5電源模塊設計

由于信號處理板高速信號線多、系統較復雜,集成了大規模交換芯片、FPGA器件、DSP器件、DDR存儲器以及各種接口電路。對電源的輸出紋波、轉換效率、電壓精度、上電順序以及電源完整性提出更高的要求。VPX接口提供直流12 V和3.3 V。其中3.3 V直接供給MCU芯片,用來對電源模塊的上電時序控制。12 V經過電流保護芯片XC388QDC輸入DC/DC模塊,該芯片最大浪涌電壓可達到60 V,通過電阻可以調節輸入保護電壓。DC/DC電源模塊選取LTM4644,LTM4630,2款電源為BGA封裝,具有體積小、效率高、易于散熱等特點。電源管理如圖7所示。

3軟件設計

信號處理板的軟件包括DSP,FPGA,MCU嵌入式軟件。FT-M6678主要用來實現復雜的浮點信號處理,如信號分析與解調、信號側向、常規信號測量與信號截獲等功能。例如,用一片DSP芯片完成7路4 Msps的16QAM信號的解調,或者一路40 Msps的16QAM信號的解調等。在8個核的功能分配上,核0一般用于完成芯片的初始化,解析系統發過來的指令以及控制SRIO收發數據等,其他7個核協同完成信號處理的算法[4]。

模塊中的FPGA主要完成系統中各模塊間I/O時序控制、數據緩存、數據串并轉換以及對AD采集的中頻信號進行數字下變頻,FFT等預處理的功能。

MCU由VPX的專用電源供電,完成對交換芯片NRS1800的初始配置,完成上電后的系統自檢功能,利用其片內AD采集板子上的各種電壓值。MCU通過I2C總線與監控模塊進行數據交換,實現IPMC管理。

4關鍵技術

考慮到大部分的差分信號都工作在千兆赫茲,因此,需要采取必要的措施來保證信號的完整性和電磁性,使用MENTOR公司的Hyperlynx仿真軟件對關鍵信號線進行了仿真分析。對交換模塊PCB上的高速信號線進行了仿真分析,使每對差分線阻抗保持100Ω,同一個端口內的各差分線之間的信號傳輸偏移時間小于11 ns,差分線之間沒有大的串擾,從而保證了信號的高質量要求[5]。

時鐘是整個板卡的工作中樞神經,各個功能單元的有機協調工作都由其來驅動激發[6]。本板采用高性能時鐘芯片AD9523,配以高精度的VCXO來輸出所需的各種時鐘。整個處理板內的所有模塊時鐘同源,可以改善信號的完整性,使整個板卡工作的性能更高更穩定。

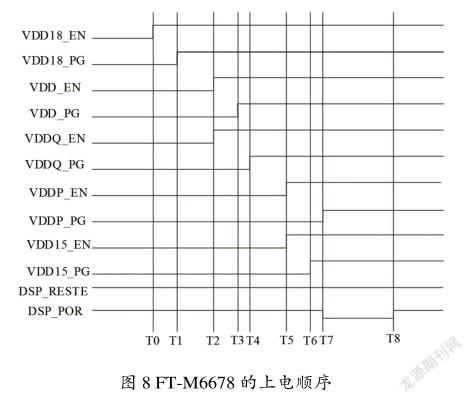

電源是給電子電路提供能量的重要電路組成部分,其電參數的精度和效率直接影響電路的正常工作[7]。本設計中主要以SM4644和SM4630大功率多路輸出電源為主,SM74401和SM51200底紋波線性電源為輔的設計方法。芯片的上電時序由MCU控制。交換芯片NRS1800上電時序為3.3 V上電,然后1.2 V再上電,上電間隔要大于10 ms。FT-M6678除了有高速的處理單元,還集成了豐富的片上外設接口。這些接口,有些需要獨立的電源,有的接口之間要求特定的上電順序。FT-M6678的上電順序如圖8所示。

5結束語

在目前的國際形式下,芯片國產化勢在必行,且VPX總線架構作為行業內主流的平臺,具有模塊化、通用化、擴展性、開放性和高可靠等特點。本文設計國產化信號處理板,具有較強的通用性,非常適用在通信偵對抗等領域。通過該板的研制,為高速總線互聯設計及國產芯片設計提供非常好的技術借鑒。

參考文獻

[1]于東英,陳俊,康令州.基于國產FPGA的高速SRIO接口設計與實現[J].通信技術,2019,52(1):255-258.

[2]肖希,張雄林.基于VPX架構的高速信號板設計[J].兵工自動化,2017,36(12):34-38.

[3]朱紅育,李郁,付學斌.IPMI在VPX系統中的應用與設計[J].火控雷達技術,2013,42(4):65-69.

[4]馬友科,吳冰.基于多核DSP的通用信號處理板設計[J].無線電工程,2014,44(9):56-59.

[5]齊青茂,馮鶴,馬友科.基于Hyperlynx的高速數據傳輸板SI研究[J].計算機與網絡,2012,38(14):47-49.

[6]白月勝,曹淑玉.基于AD9517的高速采樣時鐘設計[J].工業技術創新,2014,1(4):460-464.

[7]屈召貴,周永強.高精度DC-DC電源設計[J].微型機與應用, 2017,36(17):34-37.