一種半導(dǎo)體芯片的設(shè)計(jì)方向研究

楊志偉

(吉林工業(yè)職業(yè)技術(shù)學(xué)院智能制造學(xué)院,吉林 吉林 132013)

1 引言

隨著半導(dǎo)體芯片的蓬勃發(fā)展,晶閘管芯片因其具備高阻斷電壓、大電流條件下工作、容量大和體積小等優(yōu)點(diǎn)而在功率半導(dǎo)體器件中有著不可或缺的地位。

筆者認(rèn)為,在這些優(yōu)勢(shì)的基礎(chǔ)上,進(jìn)一步提升晶閘管芯片觸發(fā)電流的能力及其動(dòng)態(tài)特性,將成為其未來的發(fā)展的方向[1]。由于根本的解決方案主要取決于其芯片結(jié)構(gòu)的設(shè)計(jì),因此中心門級(jí)和多層的P/N 型半導(dǎo)體是當(dāng)前最為有利的設(shè)計(jì)方案[2]。

2 晶閘管芯片的基本結(jié)構(gòu)

圖1為晶閘管芯片的基本結(jié)構(gòu),其結(jié)構(gòu)設(shè)計(jì)基礎(chǔ)主要為P/N/P/N。由于圖1主要為單向晶閘管芯片結(jié)構(gòu),因此其中A 代表陽極、K 代表陰極、G 代表門極;在雙向晶閘管芯片的情況下,G依然繼續(xù)代表門極,而與門極同一面的電極(包括陰極和陽極)則一般使用MT1 極來代表,另一面(也包括陰極和陽極)常使用MT2 極來代表。

圖1 晶閘管的基本結(jié)構(gòu)

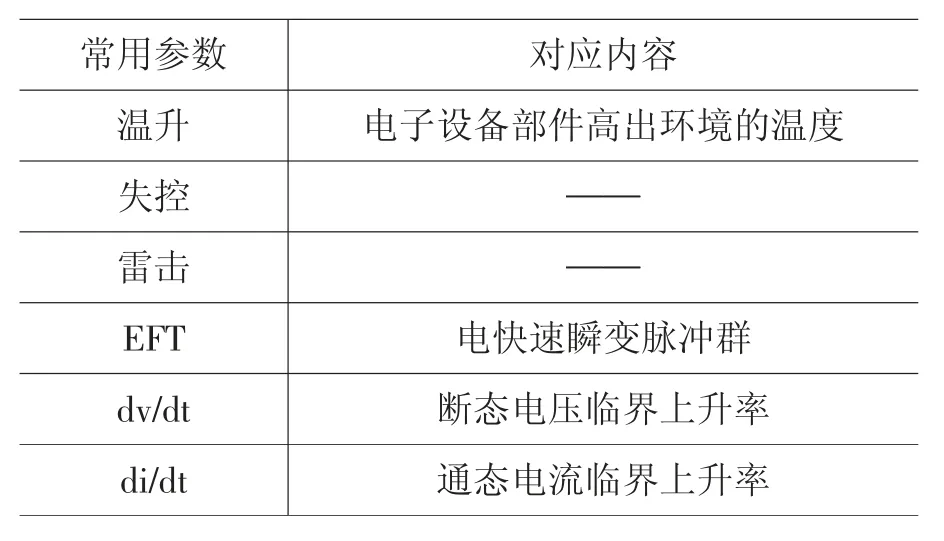

在了解晶閘管芯片相關(guān)參數(shù)的基礎(chǔ)上,能夠更加清晰地理解提升新型結(jié)構(gòu)晶閘管芯片性能的機(jī)理,尤其是是門極的影響。晶閘管芯片的常用參數(shù)如表1所示,晶閘管芯片的其他測(cè)試參數(shù)如表2所示[3]。

表1 晶閘管芯片的常用參數(shù)

表2 晶閘管芯片的其他測(cè)試參數(shù)

為更清晰地描述該半導(dǎo)體芯片的導(dǎo)通原理,可將圖1所示的芯片結(jié)構(gòu)看作是兩個(gè)互相作用的三級(jí)管的組合,由此衍生出如圖2所示的半導(dǎo)體導(dǎo)通原理。

假設(shè)電路處于穩(wěn)定的阻斷狀態(tài),電壓UA 實(shí)際上是降于集電極的勢(shì)壘區(qū)上。在外電路中,電流IA=IA0,在數(shù)量級(jí)上與集電極漏電流IC2 或門極電流IG0相當(dāng),并由其中較大值的來決定。

當(dāng)t=0 時(shí),合上開關(guān)S,門極電流以增量δIG突然增加。這樣晶體管T2 的基極電流就由起始值IB20=I*B20+IG(t﹤0)增加至IB20=I*B20+IG0+δIG(t=0)。此時(shí),發(fā)射極J3 更正向偏置,更多的電子由此注入基區(qū),并向集電極擴(kuò)散,其中只有一部分在途中被復(fù)合掉,因此集電極電流增加。

受到電子渡越時(shí)間的限制,經(jīng)過延遲時(shí)間tv2 后,陽極電流才開始增加。為了簡化作出如下假設(shè),經(jīng)過延遲時(shí)間后,集電極電流能夠準(zhǔn)確地增加至新值,如此可得方程式(1):

式中,β2—晶體管2 在共發(fā)射極回路的小信號(hào)電流放大系數(shù)。

同時(shí),集電極電流IC2 即晶體管T1 的基極電流IB1 供給n 基區(qū)電子。當(dāng)t=tv2 時(shí),晶體管T1 的基極電流的增量為ΔIB1(tv2)=ΔIC2(tv2)=β2δIG。

類似于晶體管2,經(jīng)過延遲時(shí)間tv1 后,集電極電流增量如方程式(2)所示:

式中,t1=tv1+tv2;β1—晶體管1 的小信號(hào)電流放大系數(shù)。

另外,當(dāng)集電極電流IC1 流回晶體管2 的基區(qū)時(shí),IC1=I*B2,t1=tv1+tv2,該電流在晶體管T2中又使基極電流有了新的增加,具體如方程式(3)所示:

方程式(3)表明:原始信號(hào)δIG 在兩個(gè)晶體管中依次被放大β2 和β1 倍后,又反饋回原基極。因此,沿著反饋回路總的放大系數(shù)(該反饋回路已在圖2中用虛線表示)為β12=β1β2。

開通(門極觸發(fā))意味著陽極電流IA=IE1 趨于無限增加,這是以基極電流無限增加為前提的,一旦反饋信號(hào)稍大于或等于原始輸入信號(hào)ΔIG,基極電流就會(huì)無限增加。按照方程式(3),開通條件應(yīng)如方程式(4)所示:

方程式(4)中,兩個(gè)晶體管的共發(fā)射極回路的小信號(hào)電流放大系數(shù)的乘積至少等于1。

將β=α/(1-α)帶入方程式(4),可得等價(jià)的開通條件如方程式(5)所示:

根據(jù)方程式(5),兩個(gè)晶體管在共基極回路中的小信號(hào)電流放大系數(shù)之和至少等于1[3]。

3 門極結(jié)構(gòu)的設(shè)計(jì)方向

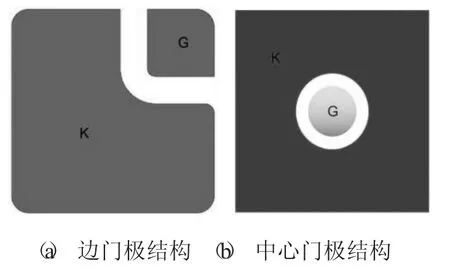

傳統(tǒng)晶閘管芯片主要使用條形門極和工字門極等[4],而且門極數(shù)量單一并位于芯片的邊緣位置,該門極的設(shè)置彌補(bǔ)了由于陰極不均勻而導(dǎo)致觸發(fā)速度慢等相關(guān)問題。通過調(diào)整門極的位置、形狀、大小、數(shù)量以及不同組合等方式,使門極的分布更加多樣化并更具可控性。門極的調(diào)整在一定程度上可優(yōu)化開關(guān)速度、通態(tài)壓降、擴(kuò)展速度、di/dt 和開關(guān)損耗等相關(guān)參數(shù),用以匹配不同產(chǎn)品的需求[3]。為進(jìn)一步驗(yàn)證中心門極的優(yōu)勢(shì),制備了如圖3的光刻版圖。

圖3 兩種不同結(jié)構(gòu)的門極

從圖3(a)和圖3(b)的對(duì)比可以看出,中心門極更利于其觸發(fā)。一方面中心門極與發(fā)射極之間的觸發(fā)點(diǎn)更多,觸發(fā)更敏感;另一方面,在實(shí)際工藝中,由于光刻的輕微偏差都會(huì)導(dǎo)致觸發(fā)電流的波動(dòng),而從圖3(b)中可以看出中心門極的觸發(fā)極位于中心位置,因此對(duì)于光刻誤差的影響會(huì)大幅度降低。

盡管中心門極在理論上具有優(yōu)勢(shì),但在實(shí)際生產(chǎn)中能否得到與理論對(duì)等的結(jié)果還需要進(jìn)一步試驗(yàn)驗(yàn)證的。為此,2021年吉林華微電子股份有限公司的研發(fā)團(tuán)隊(duì)就該設(shè)想進(jìn)行了驗(yàn)證,并發(fā)表相關(guān)專利進(jìn)行理論論證和技術(shù)保護(hù)[5]。根據(jù)相關(guān)專利可以獲取中心門級(jí)在使用上的明顯性能優(yōu)勢(shì)。

傳統(tǒng)的晶閘管芯片技術(shù)往往局限于單一門極和固定位置。為進(jìn)一步提升晶閘管性能,如圖4所示設(shè)計(jì)了不同的芯片結(jié)構(gòu)。

圖4 不同設(shè)計(jì)的芯片結(jié)構(gòu)

圖4中固定在邊緣位置的門極普遍觸發(fā)較為不均勻,固定在中心位置則會(huì)增加引線過程中的成本需求,而引入偏心和多重門極就可以同時(shí)解決邊緣門極的不均勻和中心門極的引線成本。引入環(huán)形門極利于提升雙向晶閘管芯片的開關(guān)速度,并與其他門極配合起到共同放大門極的效果。不同配合方式的門極不僅能夠起到提升性能和產(chǎn)品質(zhì)量的作用,還能夠匹配實(shí)際生產(chǎn)中的相關(guān)需求并彌補(bǔ)局限性。因此,未來門極的結(jié)構(gòu)將向著更廣泛的設(shè)計(jì)層面發(fā)展,并根據(jù)實(shí)際情況在不同應(yīng)用領(lǐng)域通過調(diào)整不同的觸發(fā)極狀態(tài)來實(shí)現(xiàn)其觸發(fā)效率的最大程度提升。

4 多層半導(dǎo)體結(jié)構(gòu)分析

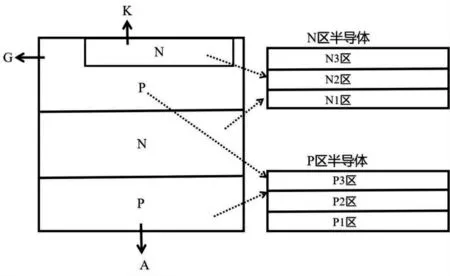

根據(jù)晶閘管芯片基礎(chǔ)原理可知,隨著PNN+結(jié)構(gòu)中電壓的不斷升高,空間電荷區(qū)的展寬在到達(dá)N+層后,由于N+層雜質(zhì)濃度較高,空間電荷區(qū)的展寬變得很小。當(dāng)結(jié)區(qū)最大電場(chǎng)強(qiáng)度持續(xù)增強(qiáng)后,待到達(dá)雪崩電場(chǎng)強(qiáng)度時(shí),反向電流將會(huì)急劇增加。據(jù)此可得,增加了N+層可在一定程度上提高晶閘管的耐壓能力[6]。同理,在晶閘管芯片的各摻雜硅區(qū)域形成一定的濃度差也會(huì)使芯片的耐壓和穩(wěn)定性得到一定程度地提升,而工藝上不同元素?fù)诫s硅的擴(kuò)散推結(jié)速率也是這樣。基于實(shí)際的工藝情況,不同結(jié)深同時(shí)配合不同元素也更加利于控制生產(chǎn)與整體工藝的穩(wěn)定性[7]。為更明確展示多層半導(dǎo)體結(jié)構(gòu)的設(shè)計(jì)方案,設(shè)計(jì)了如圖5所示的晶閘管芯片多層半導(dǎo)體結(jié)構(gòu)示意圖。

圖5 晶閘管芯片多層半導(dǎo)體結(jié)構(gòu)示意圖

從圖5中可以看出,多層半導(dǎo)體主要定義為某P/N 型半導(dǎo)體內(nèi)部結(jié)構(gòu)。該P(yáng)/N 型半導(dǎo)體內(nèi)部形成不同的半導(dǎo)體層,每個(gè)半導(dǎo)體層具備獨(dú)特的半導(dǎo)體摻雜濃度或者不同的摻雜元素。基于此,可在一定程度上提高晶閘管芯片的動(dòng)態(tài)參數(shù)[8]。具體工藝形式:首先,進(jìn)行低濃度深結(jié)擴(kuò)散,即注入低濃度P 或N 型摻雜物質(zhì);其次,進(jìn)行高溫長時(shí)間推結(jié);然后,進(jìn)行高一級(jí)濃度的注入后繼續(xù)推結(jié);最后,依次進(jìn)行相關(guān)工藝,以獲取多層次的半導(dǎo)體結(jié)構(gòu)。

為此,筆者所在研究團(tuán)隊(duì)先同時(shí)制備了常規(guī)的單層半導(dǎo)體結(jié)構(gòu)與優(yōu)化的多層半導(dǎo)體設(shè)計(jì)結(jié)構(gòu),再在調(diào)試出相同靜態(tài)參數(shù)的情況下,通過同一封裝公司、同樣的封裝外形,取回后進(jìn)行相應(yīng)的動(dòng)態(tài)參數(shù)測(cè)試。經(jīng)過測(cè)試發(fā)現(xiàn):單層結(jié)構(gòu)與多層結(jié)構(gòu)除溫升較為接近外,多層結(jié)構(gòu)的其他參數(shù)有著明顯的優(yōu)勢(shì)。特別是晶閘管中的重要?jiǎng)討B(tài)參數(shù),如多層結(jié)構(gòu)在斷態(tài)電壓臨界上升率(dv/dt)方面有著特別明顯的優(yōu)勢(shì),幾乎是接近單層結(jié)構(gòu)的二倍,這對(duì)于未來漏保產(chǎn)品的研究有著重要的參考價(jià)值[9-10]。

當(dāng)前的常規(guī)單層晶閘管芯片一般會(huì)增加一層高濃度P 型摻雜層,主要原因是當(dāng)半導(dǎo)體與金屬接觸時(shí),通常會(huì)形成勢(shì)壘層,但是當(dāng)半導(dǎo)體摻雜濃度很高時(shí),電子則可憑借隧道效應(yīng)穿過勢(shì)壘,從而形成低阻值的歐姆接觸[8,10]。歐姆接觸對(duì)于半導(dǎo)體器件非常重要,形成良好的歐姆接觸有利于電流的輸入和輸出。P 型摻雜硅的濃度如果較高會(huì)導(dǎo)致電壓低的問題,且P 型摻雜硅的導(dǎo)電性本身較差,因此需要在P 型摻雜區(qū)表面與引線孔接觸一側(cè)形成高濃度摻雜。在實(shí)際工藝中,高濃度P 型摻雜硅影響N 型摻雜硅濃度,同時(shí)高濃度P 型摻雜硅由于導(dǎo)電性較好,容易造成表面短路現(xiàn)象,就會(huì)影響晶閘管芯片的門極觸發(fā),從而造成觸發(fā)電流增加的現(xiàn)象,因而不利于小觸發(fā)晶閘管芯片的研發(fā)[11]。為此,需要有針對(duì)性地重新規(guī)劃表面高濃度P 型摻雜硅,在相同工藝情況下,針對(duì)P 型摻雜硅進(jìn)行有規(guī)律的光刻可以避免高濃度的P 型摻雜硅摻雜到陰極區(qū)、門極與發(fā)射極隔離區(qū)的區(qū)域,這也在最大程度上提升了晶閘管芯片的觸發(fā)性能[11]。

4 結(jié)語

目前,晶閘管芯片的設(shè)計(jì)方向更加多元化,具體表現(xiàn)在門極多樣化、多層半導(dǎo)體和P 型摻雜硅的圖形化,而且隨著人們對(duì)功率半導(dǎo)體的重視和投資加大,不僅相關(guān)科研水平穩(wěn)步提升,相關(guān)領(lǐng)域人才需求也在逐步增加,因此為了使晶閘管芯片研發(fā)步入世界前列,對(duì)于晶閘管芯片的相關(guān)設(shè)計(jì)與優(yōu)化仍然持續(xù)進(jìn)行。

- 技術(shù)與教育的其它文章

- 教育部等有關(guān)部門職業(yè)教育重要文件摘編(2022年下半年)

- 高職院校“互聯(lián)網(wǎng)+”大賽項(xiàng)目實(shí)施和思考

——以吉林省“互聯(lián)網(wǎng)+”大學(xué)生創(chuàng)新創(chuàng)業(yè)大賽銀獎(jiǎng)項(xiàng)目“工業(yè)水垢處理專家”為例 - 校內(nèi)生產(chǎn)性實(shí)訓(xùn)基地建設(shè)研究

- 鄉(xiāng)村振興戰(zhàn)略下發(fā)展農(nóng)村職業(yè)教育影響與實(shí)施路徑研究

- “一主多元”跨企業(yè)職工培訓(xùn)與管理模式探索研究

- 英語弱否定句子結(jié)構(gòu)探析