基于FPGA和ARM的音圈電機式振鏡驅動器設計

梁宇飛,石上瑤,張 棟,武 濤

(中北大學 機械工程學院,太原 030051)

0 引 言

音圈電機式振鏡具有高頻響、高加速、快響應等優勢,相較于掃描電機式振鏡可以提供更高的速度及響應[1-3],因此,音圈電機式振鏡在驅動控制方面具有更高的要求。

傳統的音圈電機大部分采用數字控制方法,其缺點是無法直接實現音圈電機的高精度要求,要達到高精度要求,需配備對應精度的ADC模塊及數字處理器等。模擬控制信號優勢體現在信號的高精度及無限分辨率,對于要高精度控制的音圈電機擁有較大的優勢,并且實際使用時音圈電機所需電流較小,音圈電機式振鏡采用模擬電路在保持不失真條件下,可以滿足高精度及高速控制。

現在工業用音圈電機驅動控制器大都采用單一處理器,再配合外圍相關電路以達到驅動目的。這種驅動方法存在諸多不足。單一使用DSP定點型處理器作為處理核心,無法保證復雜算法保持高速高精度,而且DSP外設模塊的固定化,無法滿足設計的靈活性;單一使用FPGA作為處理核心,雖然擁有并行計算及靈活性的優點,但無法完成浮點運算[4]。近幾年FPGA快速發展,將其與ARM芯片結合,可以更好地利用FPGA高速并行運算的特點,ARM芯片擁有的優良兼容性既提供更好的可行性,也彌補了FPGA無法完成浮點運算的缺點。但是現有的結合方式未充分發揮FPGA的并行計算等優勢,只是一些單純的時序處理,其性能沒有得到充分的發揮。

本文提出一種基于ARM和FPGA的異構處理器驅動控制方法,并設計軟硬件,以實現對音圈電機式振鏡的驅動控制。再依照ARM和FPGA的各自功能特點進行功能劃分和軟件設計[5]。

1 驅動器硬件結構及功能劃分

1.1 硬件結構

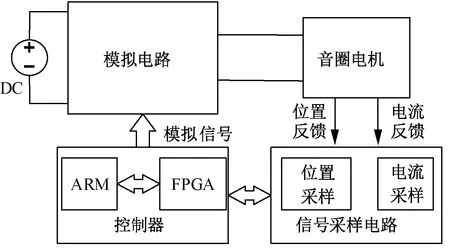

驅動控制器采用基于ARM和FPGA的結構,搭配上位機和外圍電路完成音圈電機式振鏡的驅動控制。驅動器硬件結構如圖1所示。其中ARM使用基于Cortex-M7內核的STM32H750芯片;FPGA使用Altera公司的10 M02SCU169芯片。ARM通過SPI通訊協議傳輸電壓信號到DAC芯片;音圈電機動子實時位置使用光柵尺傳感器采集并計算得到;電路電流由STM32內部傳感器采集并計算得到。

圖1 系統硬件設計

1.2 功能劃分

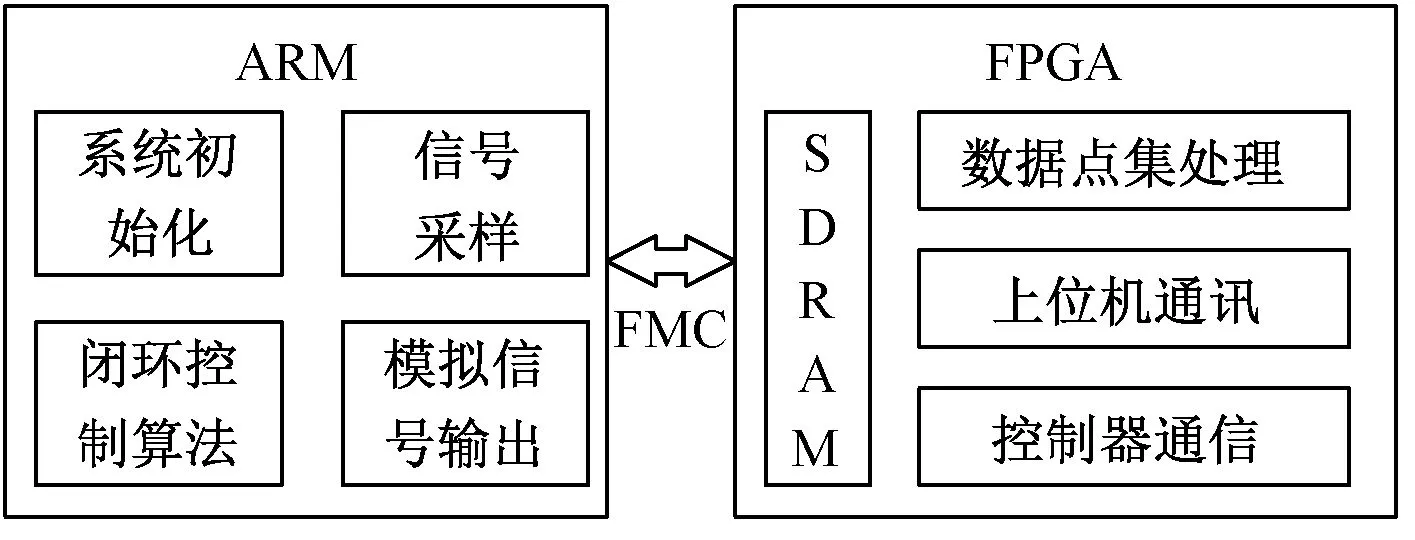

ARM屬于可編程軟件,擁有通用性、靈活性等特點。FPGA是硬件可編程類型,擁有高速并行計算能力,但在一些復雜運算的場合中會占用大量的邏輯單元,不適合高速且復雜的場合。綜合上述ARM和FPGA優缺點后,依照實際需求情況進行功能分配,其中ARM主要負責系統初始化、信號采樣、模擬信號輸出、閉環控制算法等功能,FPGA主要負責激光打標圖象點數據集處理、上位機通訊功能、與ARM之間數據交換等功能。驅動控制器中各部分功能劃分如圖2所示。

圖2 控制器功能劃分

2 FPGA功能設計

2.1 上位機通訊模塊設計

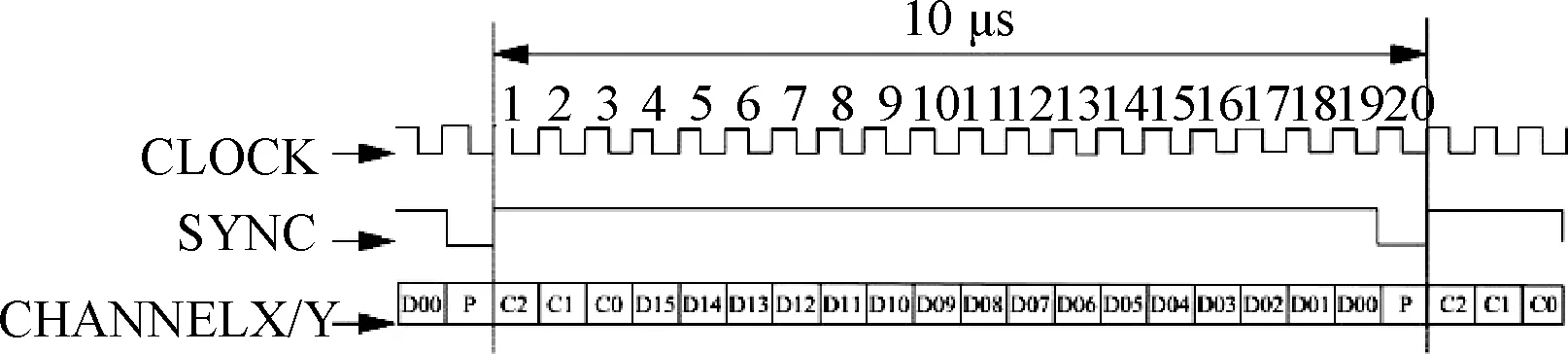

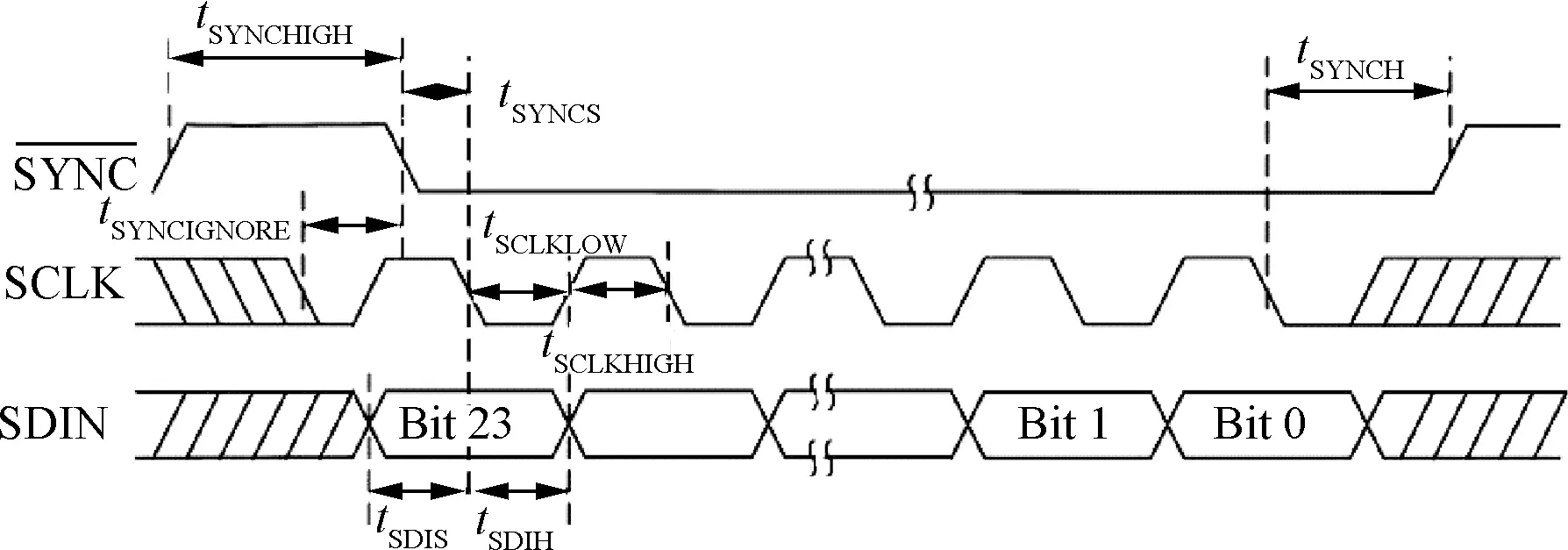

振鏡控制器與上位機通訊普遍采用XY2-100協議。此協議由時鐘信號、同步信號、X/Y坐標數據四路差分信號組成。XY2-100協議時序圖如圖3所示。

圖3 XY2-100 協議時序圖

數據通道共有20位數據位,其中第1~3位數據位為控制頭,在上升沿發送;第4~19位數據位為振鏡數據,在上升沿發送;第20位數據位為奇偶校驗位,在下降沿發送完畢[6]。

2.2 驅動器通信模塊

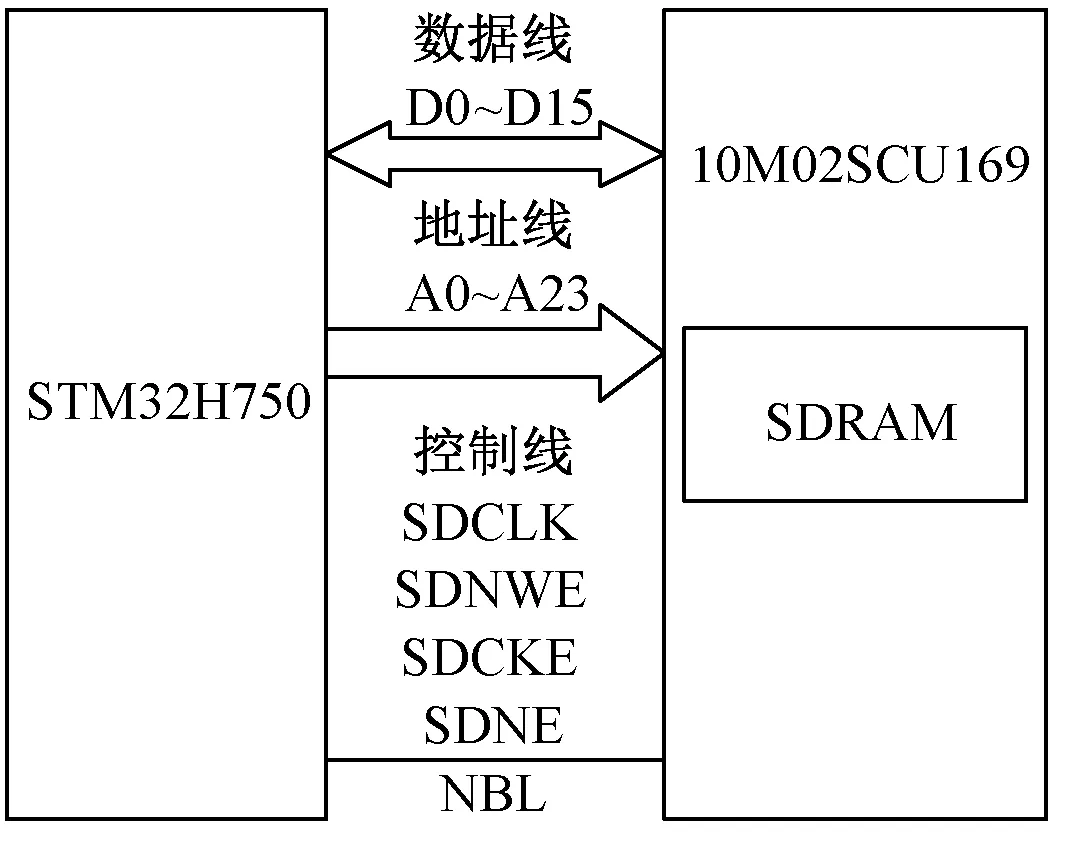

ARM和FPGA之間協同處理必須保持高速通信。它們的通信主要包括異步串行接口方式、DMA方式、總線方式和將FPGA作為存儲設備4種[6]。選用將FPGA作為存儲器的方式可以在簡化結構的同時保持高速通訊,ARM通過FMC接口訪問SDRAM存儲的信息,可以保持超高的讀寫速度,繼而滿足驅動控制所需的高速數據交換。ARM和FPGA通信原理圖如圖4所示。其中D0~D15是雙向數據總線,A0~A23是地址總線,SDCLK是SDRAM的時鐘線,SDNWE是寫入使能,SDCKE是存儲區域時鐘使能,SDNE是存儲區域芯片使能,NBL是寫訪問的輸出字節屏蔽。

圖4 ARM和FPGA通信原理圖

2.3 數據點集處理模塊

振鏡工作時,高密集數據傳輸引起上位機發送速率和振鏡速率不匹配而在某點停留時間過長,可導致激光燒蝕,但若數據點過少也會導致精度降低、質量下降[7]。使用FPGA對上位機下發圖象進行數據點提取操作,將原始數據點集經過稀疏化、曲線點集分段、最小二乘法非均勻有理B樣條曲線(以下簡稱NURBS)擬合數據處理,轉換成由少量直線和曲線構成的實體,這樣可以避免因為數據點密集或稀疏而出現問題。

NURBS曲線由控制點、權重、節點矢量和階數組成,數學定義如下:

(1)

其中Ni,k(u)滿足De-Boor遞推關系式:

式中:fi為控制點;ωi為權因子;u為節點矢量[8]。

在FPGA中對上位機下發數據點集進行再處理。對于包含節點矢量和數據坐標的值,使用最小二乘法擬合NURBS曲線,最終可以得到通過最小二乘法全局逼近的NURBS表達式。

3 ARM功能設計

3.1 ARM主程序

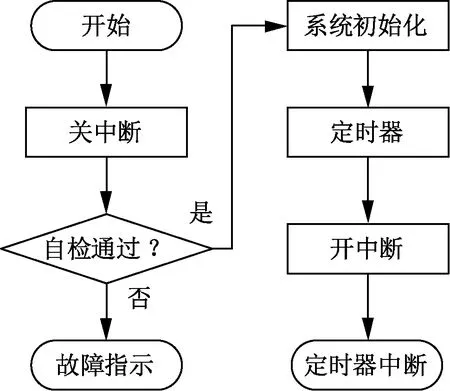

ARM主程序主要用于全局階段性控制,把握每一個階段,例如開關中斷、系統初始化以及系統定時器的駛入駛出等過程。其主程序流程圖如圖5所示。

圖5 ARM主程序流程圖

3.2 信號輸出模塊

驅動器采用模擬電路控制,通過STM32生成連續模擬信號,16位DAC80501使用SPI接口以DMA方式發送到驅動電路中。STM32H750使用SPI協議以DMA方式驅動DAC外設能夠得到比肩FPGA的速度。DAC的SPI接口通信協議如圖6所示。

圖6 DAC的SPI接口通信協議

3.3 信號采樣模塊

信號采樣包括電流采樣和位置采樣兩部分。電流采樣使用STM32H750內部的16位ADC1采樣,并且內部ADC采樣需在STM32上外接3.3 V的基準電壓。位置采樣使用1 μm增量式光柵尺,通過高速差分線路接收器將采集的A-,A+,B-,B+,Z-,Z+轉化為A,B,Z三相信號。其中A、B表示光柵尺的位置信號,Z表示光柵尺的原點信號。

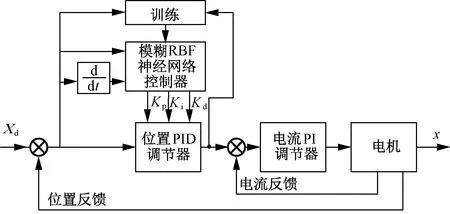

3.4 閉環控制算法模塊

電機控制算法采用模糊RBF神經網絡的位置控制和PI電流控制。位置環由模糊RBF神經網絡控制器實現PID參數的實時控制,根據位置輸出誤差及誤差率作為控制器的輸入,通過模糊RBF神經網絡控制器的模糊化及模糊推理,并且進行不間斷訓練,最終可動態修正PID控制參數Kp,Ki,Kd,使系統擁有更好的抗干擾能力和動態響應[9-13]。電流環采用傳統的PI控制即可達到目標穩定效果。

閉環控制算法示意圖如圖7所示。

圖7 閉環控制算法示意圖

4 模擬電路設計仿真及實驗

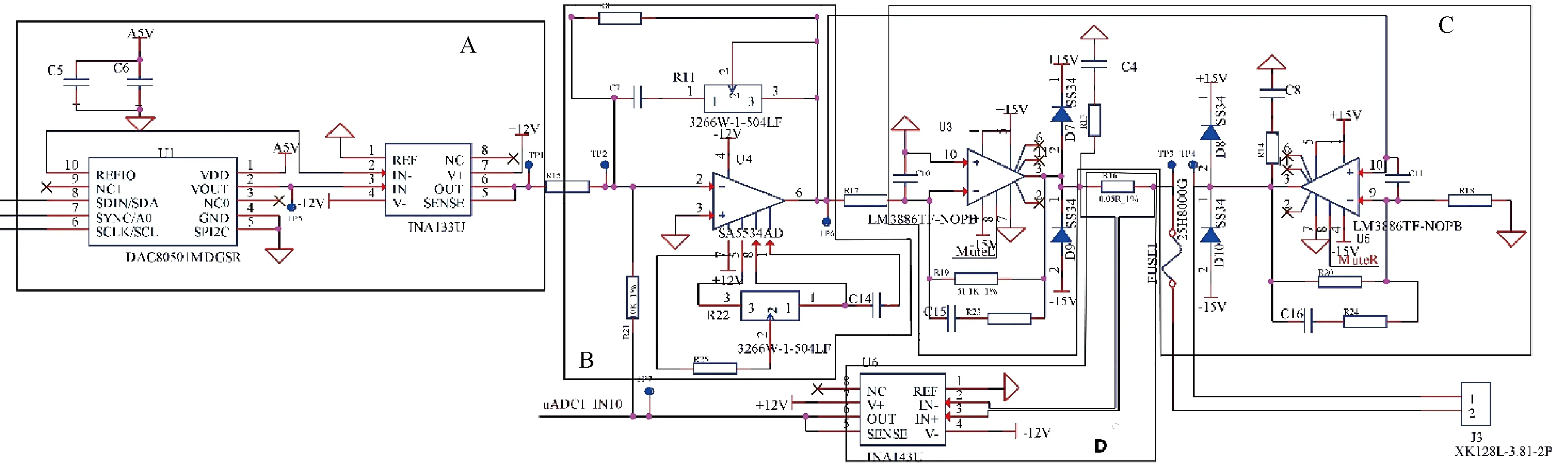

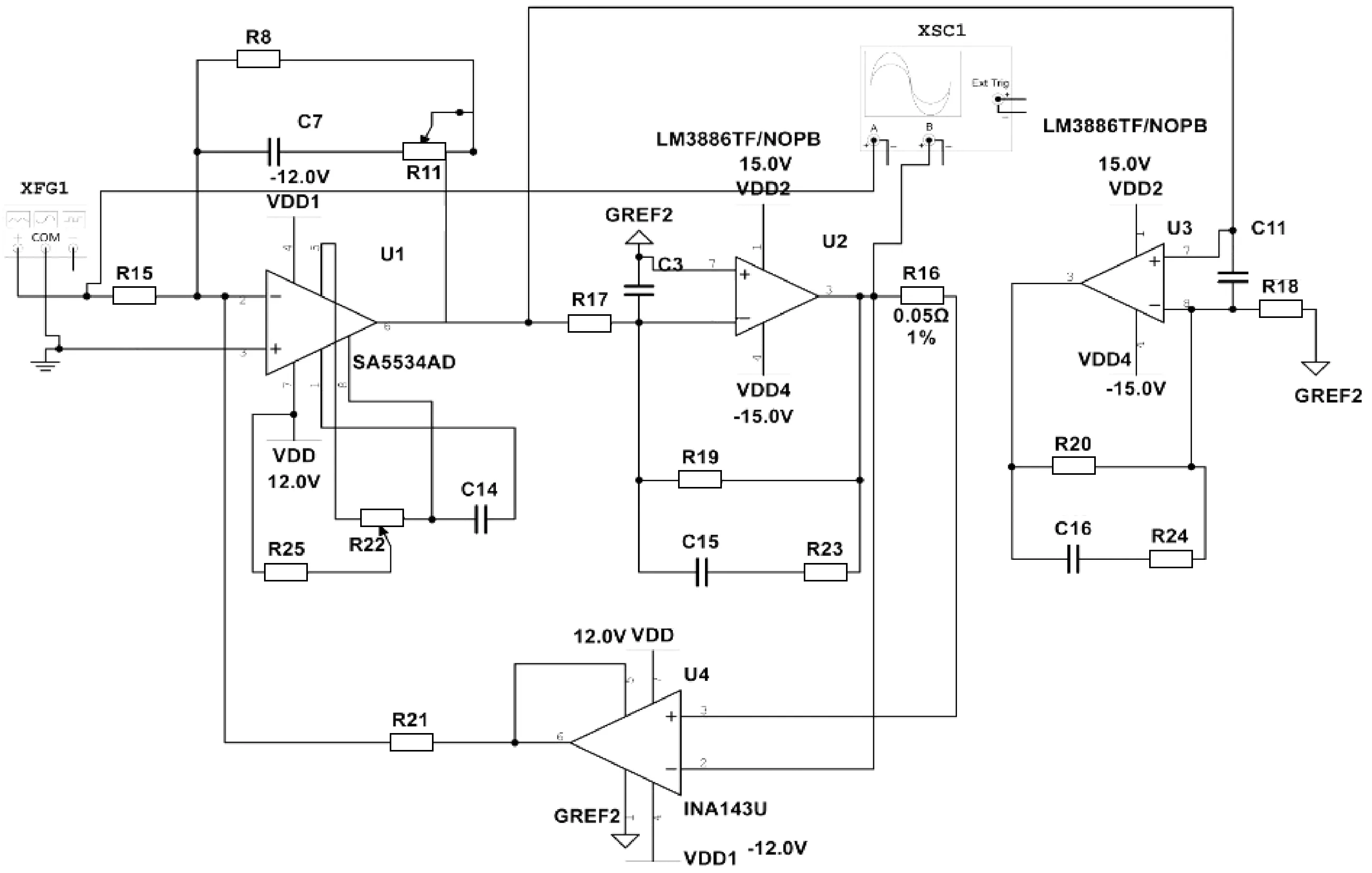

根據需求設計的全模擬驅動電路,如圖8、圖9所示。再使用NI multisim進行電路仿真,探究是否符合設計要求[14]。

圖8 驅動電路圖

圖9 位置采樣信號電路圖

4.1 驅動電路設計

4.1.1 差分轉單端電路

DA信號的輸出需要轉化為單端信號進行后續的計算,本電路差分轉單端芯片選用TI公司的INA133U,可以實現準確的增益和高共模抑制。電路如圖8中A所示。

4.1.2 運算放大電路

運算放大器采用TI公司的SA5534AD,具備高輸出驅動能力等特點。通過在COMP和COMP/BAL上連接外部補償電容器來優化各種應用的頻率響應。電路如圖8中B所示。

4.1.3 功率驅動電路

功率驅動芯片采用TI公司的LM3886TF,可以利用自身自峰值瞬時溫度保護電路,提供動態受保護的安全工作區,使輸出端得到完全的保護,防止欠壓、過壓等。電路如圖8中C所示。

4.1.4 電流采樣電路

電流采樣采用精密采樣電阻采樣,方便接入模擬電路,且不會影響電路輸出終值。使用INA143U處理采樣電阻兩端信號,輸出單端信號計算得到實時電流值。電路如圖8中D所示。

4.1.5 位置采樣電路

位置采樣電路將光柵尺傳感器輸出的差分信號輸入到AM26LV32ETPWR中轉化為單端信號。位置采樣電路如圖9所示。

4.2 驅動電路仿真測試

根據圖8電路在NI multisim中進行電路繪制并仿真測試,NI multisim中繪制的仿真電路圖如圖10所示。

圖10 NImultisim軟件仿真電路圖

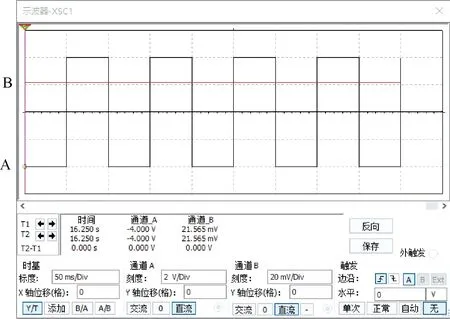

使用軟件自帶的信號發生器在電路輸出端輸入30 Hz方波信號,測試得到電路最終的穩定輸出信號。仿真結果如圖11所示,通道A表示輸入方波信號,通道B表示穩定情況下精密采樣電阻實測電壓值,滿足設計要求[15]。

圖11 仿真結果圖

4.3 實驗測試

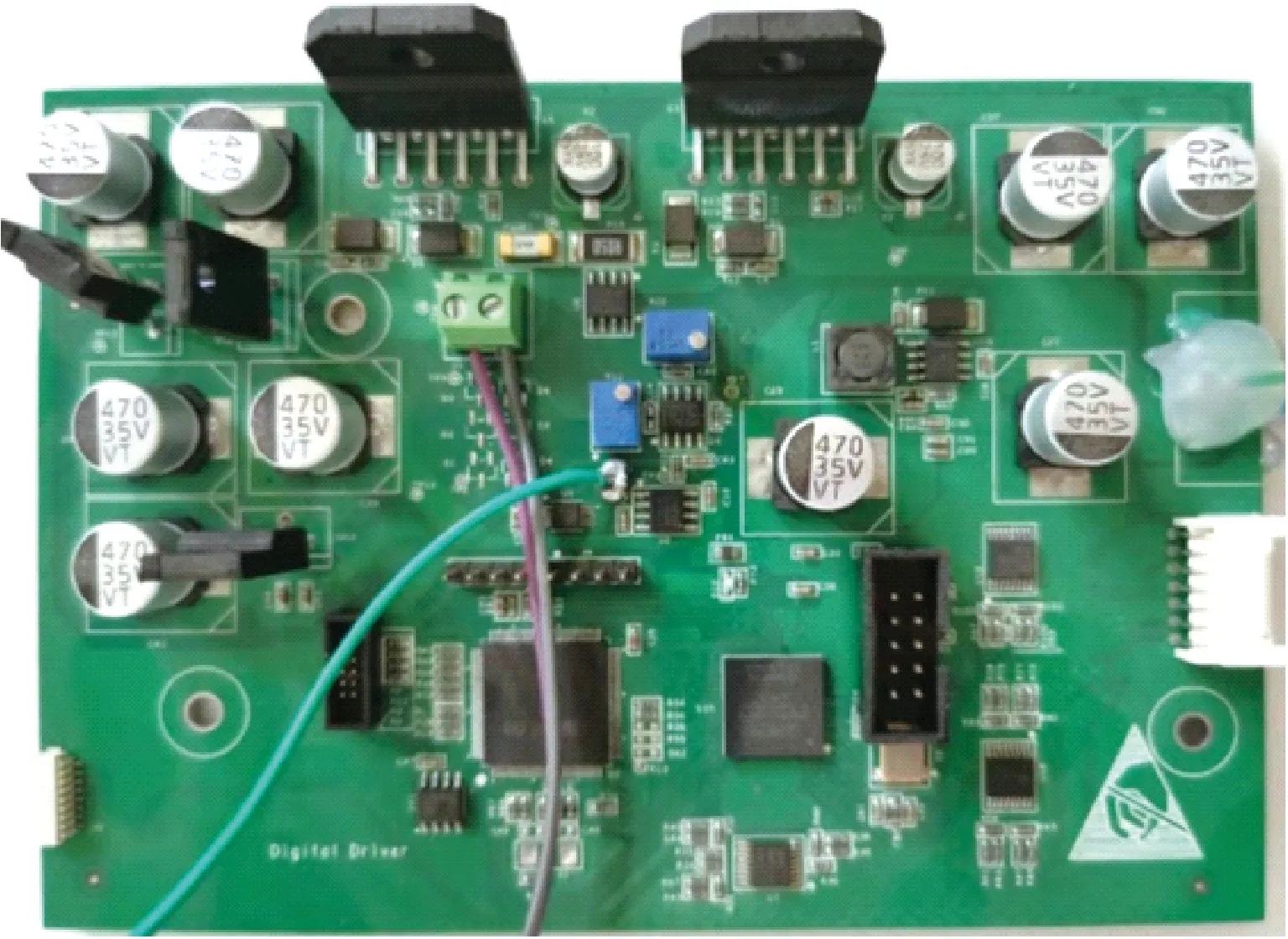

本文設計的驅動器開發板如圖12所示。

圖12 硬件驅動板實物圖

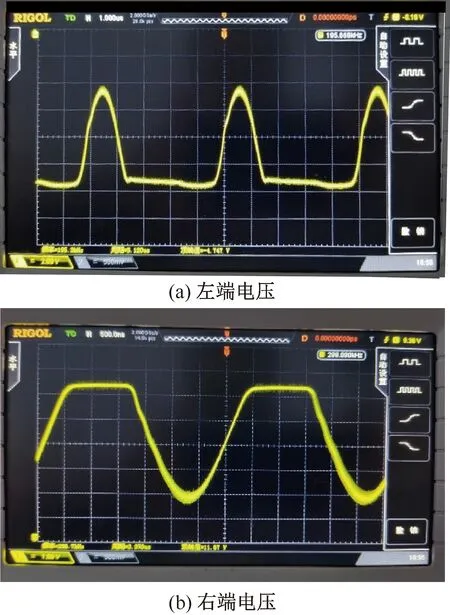

本文基于FPGA和ARM設計的驅動器開發板,輸出驅動電機兩端電壓信號,如圖13所示。所測兩端電壓信號可以滿足設計音圈電機的驅動控制,說明本文設計的驅動器有效。

圖13 電機兩端電壓圖

5 結 語

本文提出一種基于ARM和FPGA的音圈電機驅動控制系統,完成了音圈電機式振鏡驅動電機控制板的設計和驗證,根據芯片各自的功能特點進行功能劃分。仿真實驗表明,設計的驅動電路板可以實現所需功能,并且功能劃分也實現了系統硬件的資源合理配置,保證控制系統實時性要求。