基于特高頻傳感器的局部放電信號并行采集系統設計?

代少升劉仁光劉 凱

(1.重慶郵電大學通信與信息工程學院,重慶400065;2.重慶市信號與信息處理重點實驗室,重慶400065)

局部放電檢測技術是氣體開關絕緣設備(Gas Insulated Switchgear,GIS)故障檢測的關鍵技術,是高壓電站安全穩定運行的前提[1-4]。GIS內部絕緣缺陷類型主要有:金屬尖端、自由金屬顆粒、懸浮電極等,針對于不同的缺陷類型,其放電的波形的時域特征參數(均值、最大最小值、峰值、方差、偏斜度、陡度等)具有明顯的區別[5],放電脈沖的時域特征參數也是區分不同放電類型的主要依據。目前,主流局部放電信號檢測方法有:超聲波傳感器檢測法、特高頻傳感器檢測法、脈沖電流法。

文章在特高頻傳感器的基礎上,致力于研究如何利用分時交替并行采樣技術實現系統采樣率的提升。分時交替并行采樣技術,即TIADC(time-interleaved analog-to-digital,TIADC)技術,以4片最大采樣速率為250 MHz的AD9481模數轉換芯片實現了最大采樣率為1 GHz。該方法具有成本低和配置靈活的優點,用戶可以自行配置250 MHz~1 GHz的采樣率。此外,圍繞分時交替并行采樣技術引入的系統偏置失配誤差、增益失配誤差以及時延失配誤差,提出了基于LMS迭代的自適應偏置與增益失配校準算法以及基于Farrow結構的分數延時濾波器的時延失配校準算法。

1 系統體系結構

系統以Xilinx Kintex-7 XC7K160T-2FFG676I FPGA芯片為主控核心,完成系統的采樣、緩存以及誤差校正。系統包含AD采樣前置電路、高速數據緩存、以及誤差校正等模塊,系統結構如圖1所示。

圖1 系統結構圖

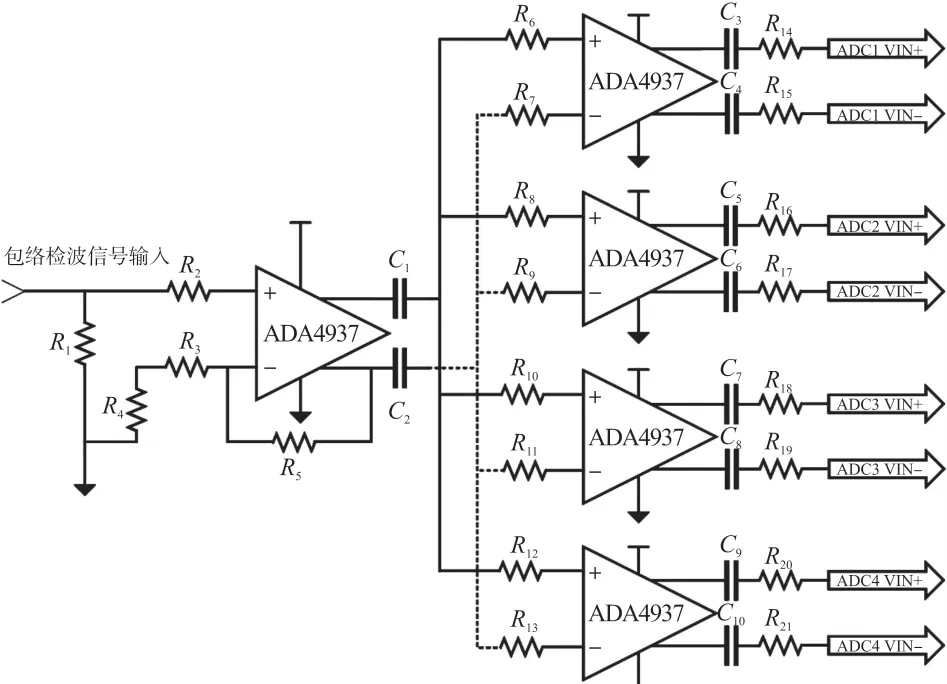

1.1 AD采樣前置電路

TIADC技術需要送入四片ADC芯片的信號是完全相同的模擬信號。設計中AD9481采用差分的方式接收數據,先將單端的包絡檢波后的信號轉換成差分輸出,再驅動成四路完全相同差分信號,輸入給高速的AD采集芯片AD9481。AD采樣前置電路如圖2所示。

圖2 AD采樣前置電路原理圖

AD采樣前置電路核心由5片ADA4937運算放大器組成,ADA4937-3 dB帶寬為1.9 GHz,其可實現單端到差分或者差分到差分的操作,具有可調的共模輸出電壓,可以通過一個電阻調節增益。

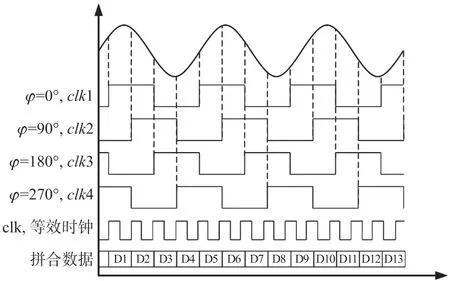

1.2 時間交替并行采樣原理

TIADC技術利用多片低速的ADC時間交替并行采集,再對各通道數據進行拼合,從而實現高速數據采集。M路子ADC采集通道,可達到的最高采樣頻率為fs,fs/M為單通道的采樣頻率,圖3為4路并行通道采樣的時序圖,各ADC通道相位相差90°。

圖3 4片ADC分時交替采樣時序圖

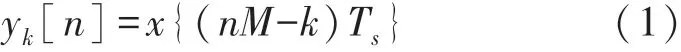

理想情況下,由各子通道進行拼合得到的數據,與采樣率為fs的單片ADC采樣結果一致。然而實際應用中,各ADC芯片性能并不完全一致、各ADC基準電平也有差異以及PCB布局布線使得相位有延遲,這些都將引起通道之間的失配誤差[6]。由參考電壓不一致引起偏置失配誤差;各通道增益不一致引起增益失配誤差;各通道時鐘相位延遲不一致引起時延失配誤差。無失配誤差時,單通道ADC的理想輸出為:

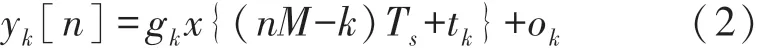

實際情況下考慮失配誤差的存在,實際的輸出為:

上述兩式中gk,ok,tk,Ts分別表示第k個子通道增益失配誤差、偏置失配誤差、時延失配誤差及多通道并行采樣周期。由于這些失配誤差的存在,導致實際的輸出數據中存在雜散譜,降低了采樣精度。因此必須采取有效措施進行校準補償。

2 數據緩存及誤差校準

2.1 數據緩存

系統以Xilinx 7系列芯片XC7K160T-2FFG676I作為主控芯片。Kintex 7系列芯片,具有基于6輸入查找表的高性能FPGA邏輯;具有高性能的I/O邏輯資源,支持DDR3的速率高達1 866 Mbyte/s;內置千 兆 收 發 器,最 大 速 率 從600 Mbyte/s到6.6 Gbyte/s,提供特殊的低功耗模式,針對芯片到芯片進行了接口優化;鎖相環(PLL)和混合模式時鐘管理器(MMCM)可產生高精度和低抖動的時鐘。

考慮到每一路ADC的采樣率為250 MHz,對從接收到的單路ADC采樣數據,首先經過Xilinx公司FPGA中的高性能輸入串行/解串器(ISERDES)進行1∶4降速處理,將每一路250 MHz的數據轉化為單路62.5 MHz的數據流,由四個異步FIFO進行跨時鐘域處理。如圖4所示,在進行數據拼合時,將4個異步FIFO中的數據讀出來,按照采樣的先后順序進行拼合。第一路的250 MHz采樣時鐘作為系統時鐘,利用對FIFO讀使能信號的控制,實現四路ADC采樣數據的拼合并存儲到DDR3內存中。

圖4 四路AD數據拼合時序圖

2.2 偏置失配誤差校準

偏置失配誤差是由于ADC采樣保持電路失配、各通道采樣參考電壓不一致以及運放失調引起。偏置失配誤差特點是不隨輸入信號的頻率變化,在時域上表現為疊加直流噪聲,僅會使ADC的動態量程造成損失,在頻域上偏置失配誤差出現在0頻附近,偏置失配誤差不是頻率的函數,不隨輸入信號的頻率變化,因此可以被視為固定值[7]。偏置失配誤差模型如圖5所示。

圖5 偏置失配誤差模型

ok為第k個子ADC通道的偏置失配誤差,一般視為固定值ok,由圖5可知:

式中:yk[n]為第k個ADC通道的時域輸出,δ(tnMTs+kTs)表示第k個通道在nMTs-kTs時刻采樣。

M個通道的合路輸出為:

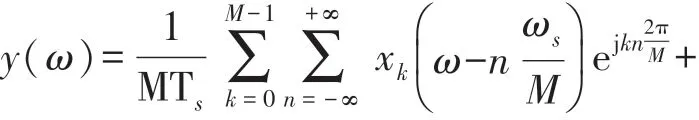

對上式作傅里葉變換得:

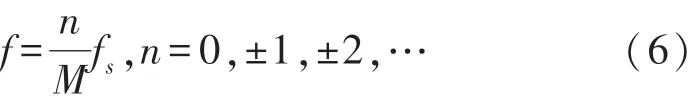

式中:第一項為ADC的理想輸出,第二項是由偏置失配誤差造成的雜散譜。由頻譜表達式可以看出雜散分量的頻率分布為:

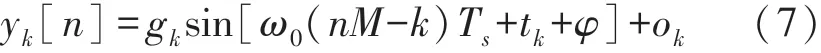

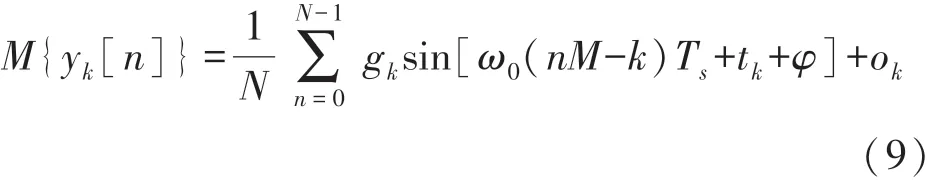

令系統輸入模擬信號為x=sin(ω0t+φ),ω0為輸入信號角頻率,φ為信號的初相,考慮三種主要的失配誤差同時存在時,第k路子ADC的輸出為:

根據正弦信號的特性可知,當采樣點數恰好為整數倍信號周期時,對上式求平均可得:

式(8)表明對采樣信號求統計平均可以獲得通道的偏置失配誤差。一般條件下,對采樣信號求平均可得:

由式(9)可知當采樣點數足夠多時,對采樣信號求均值可以得到偏置誤差的估計值為ok。因此對偏置誤差的估計,以標準正弦信號求采樣均值獲得4個采樣通道的偏置誤差并以第一通道為基準,可以求得第k通道的偏置誤差為:

2.3 增益失配誤差校準

假設系統輸入的模擬信號為x=sin(ω0t+φ),考慮增益誤差存在的情況,第k路子ADC時域表達式如下:

傳統的針對增益失配誤差的校準采用的是基于FFT變換來獲取各通道的增益誤差[8-9],此方法計算復雜且計算量大,不便于硬件實現。對于增益失配誤差,首先對輸入信號求絕對值,再進行滑動平均求得平均值,由此可得參考通道和待校準通道的平均絕對值輸出為:

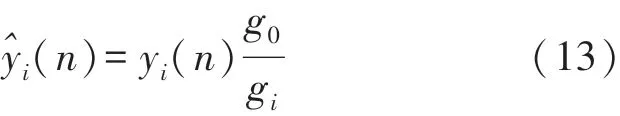

式中:gi,g0分別為待校準通道和參考通道的增益值,將|Vi|和|V0|作差,消除偏置失配誤差影響。然后經最小均方濾波器(LMS)得到通道的增益失配系數,校準后的通道輸出為:

2.4 時延失配誤差校準

每個通道的實際采樣時刻與理想采樣時刻存在時間偏差,導致時延失配誤差的產生。時延誤差通常由采樣時鐘走線延遲、輸入信號的線路延遲等造成。時延失配誤差對直流信號不影響,因為直流信號在任意時刻的采樣值一致,對于交流信號頻率越高時延失配誤差越大,輸入信號的斜率越大所造成的時延誤差越大[10-12]。

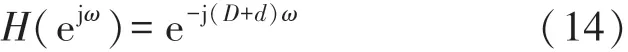

針對時延誤差采用基于Farrow結構的分數延時濾波器進行校正,分數延時濾波器的系統函數如下[13-14]:

式中:D為分數延時濾波器的整數部分,d為分數延時濾波器的小數部分。對應的幅頻響應為:

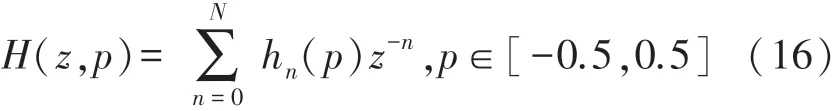

式中:p為延時部分,ω為歸一化后的角頻率,二者分別滿足ω∈[0,απ],p∈[-0.5,0.5],其中α為[0,1]之間的小數。為了最大限度的逼近理想的分數延時濾波器,Farrow結構的分數延時濾波器的頻響函數為[15-16]:

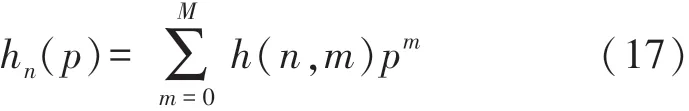

式中:hn(p)為濾波器系數是關于p的函數,以M階p的多項式近視為:

將式(17)代入式(16)得:

基于Farrow機構的分數延時濾波器的結構如圖6所示。

圖6 Farrow結構濾波器框圖

3 實驗結果

3.1 增益和偏置失配誤差校準驗證

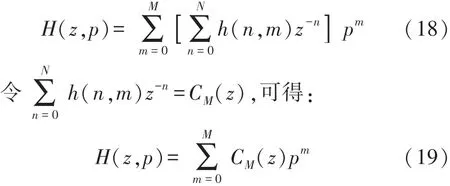

圖7 為TIADC系統增益失配和偏置失配聯合校準Simulink仿真模型,時鐘模塊采用了脈沖PulseGenerator產生四路相位差為90°、頻率為250 MHz的采樣時鐘,ADC采用Simulink模型庫中提供的精度為8位的理想ADC,量化前引入了偏置和增益失配誤差,采樣量化后經LMS自適應偏置和增益失配校準模塊,最后經Multiport Switch模塊合路輸出。Simulink仿真模型校準算法完全利用HDL Coder庫搭建,方便后續轉換為Verilog代碼進行功能仿真進一步驗證算法的有效性。

圖7 增益失配和偏置失配聯合校準模型

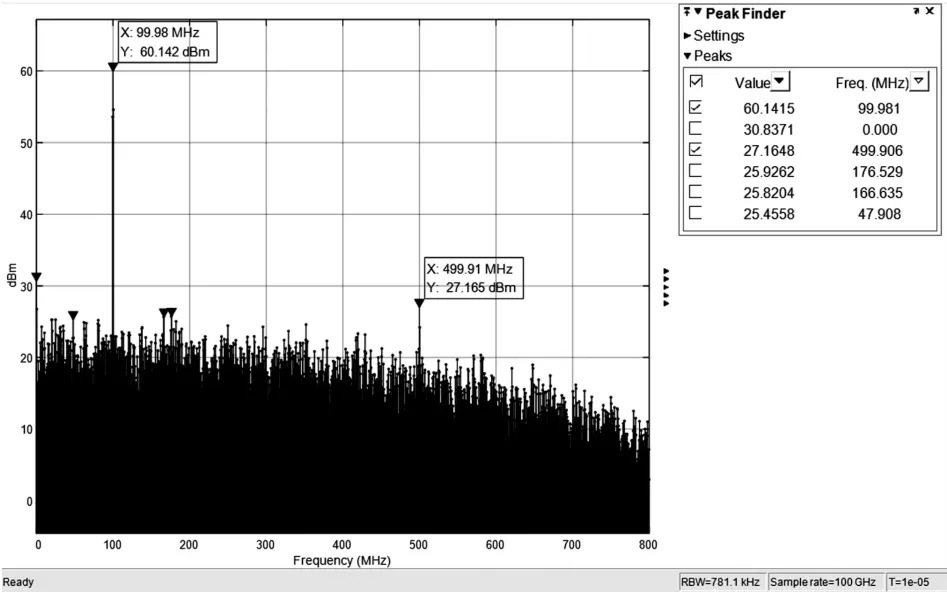

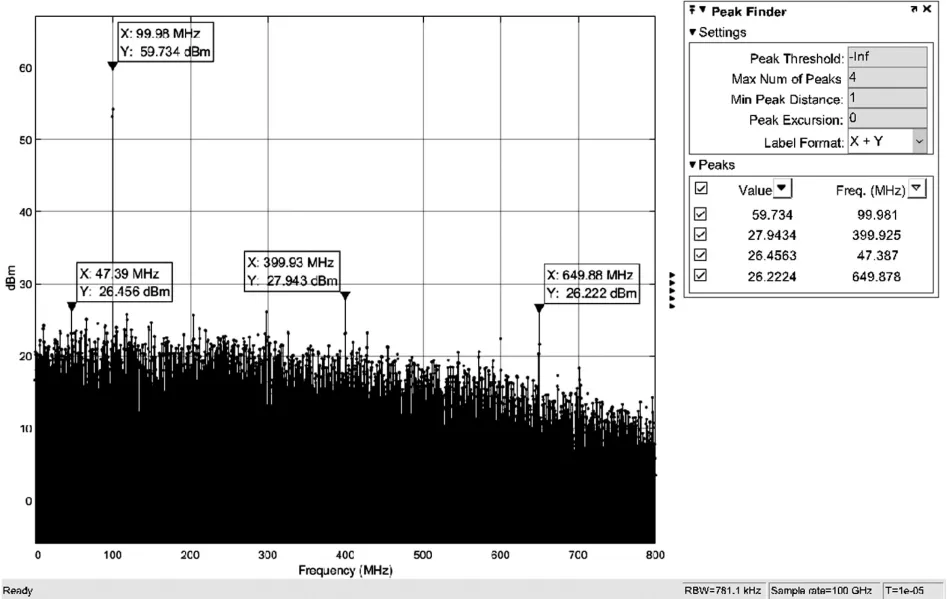

仿真參數設置如下:信號頻率為100 MHz的正弦波、各通道的偏置誤差為offset=[0.1,-0.05,0.07,0.2]、增益誤差為gain=[1,1.1,0.7,1.02]。使用Simulink自帶的頻譜分析儀對校準前后的信號分別進行FFT運算得到信號的頻譜分別如圖8和圖9所示。可以明顯看出校準后由偏置失配誤差和增益失配誤差引起的雜散譜消失,TIADC性能得到明顯提升。

圖8 增益和偏置誤差校準前頻譜圖

圖9 增益和偏置誤差校準后頻譜圖

3.2 時延失配誤差校準驗證

時延失配誤差的校準在增益和偏置校準的基礎上加入了Farrow結構的全并行分數延遲補償模塊完成時延失配誤差的補償。采樣時鐘的時延失配利用Simulink庫中的可變延時模塊添加到各通道采樣保持模塊的采樣時鐘沿,各通道的時延誤差為time=[0.1,0.1,0.07,0.2],誤差單位為ns,圖10和圖11分別為校準前后的頻譜圖。

圖10 時延誤差校準前頻譜圖

圖11 時延誤差校準后頻譜圖

3.3 三種失配聯合校準

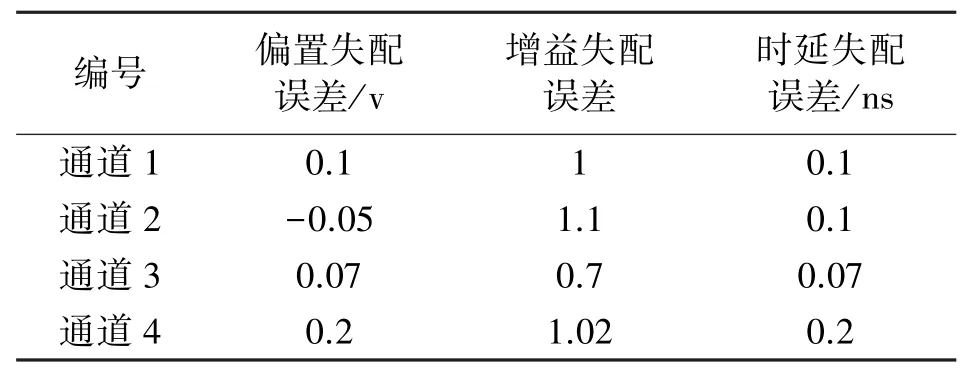

整合上述失配誤差校準算法到系統中,給定失配誤差如表1所示。

表1 三種失配誤差值

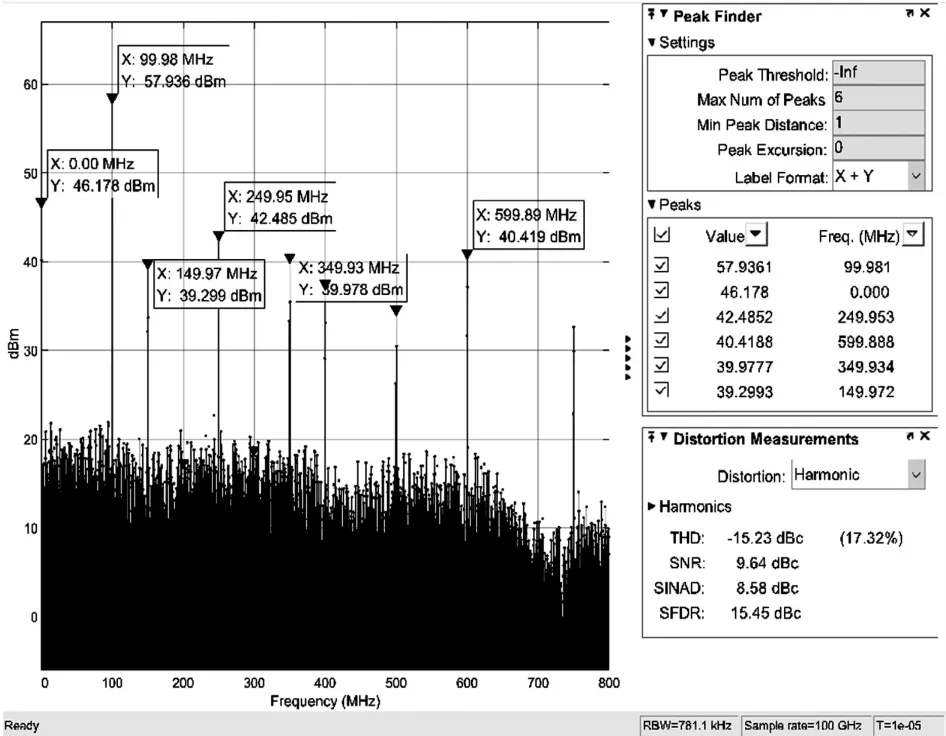

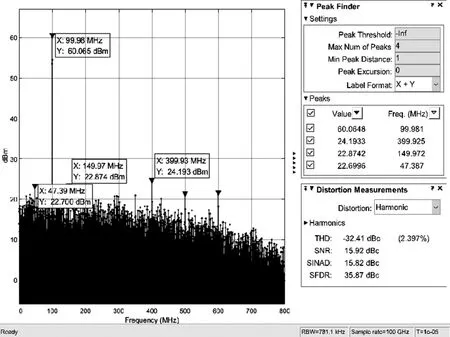

圖12 和圖13分別表示在100 MHz單頻信號輸入信號條件下,校準前后和校準后的頻譜圖。表2表示TIADC校準前后動態參數對比。

圖12 校準前頻譜圖

圖13 校準后頻譜圖

表2 校準前后動態參數對比

通過三種失配誤差聯合校準前后圖譜及校準前后動態參數對比可知,由失配誤差引起的雜散譜得到了有效的抑制,無雜散動態范圍提升到了35.87 dB。

3.4 硬件實現

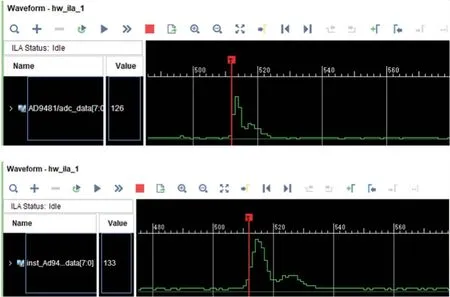

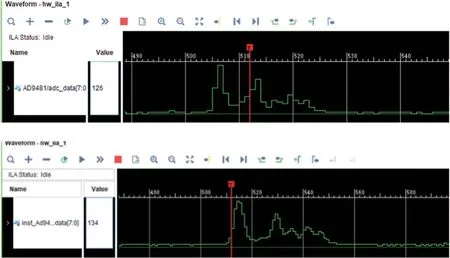

本節,利用Simulink自帶的HDL Coder工具箱將誤差校準算法轉化為硬件描述語言,Simulink會自動生成Verilog代碼,并將其加載到Xilinx XC7K160T-2FFG676I芯片。使用實驗室標準信號源產生100MHz的正弦信號,通過Xilinx自帶的邏輯分析儀抓取采集到數據波形并導出數據在MATLAB中分析得校準之后的頻譜如圖14所示,實際采集的尖端放電信號的時域波形如圖15所示。

圖14 FPGA采集100MHz正弦信號頻譜

圖15 尖端放電時域波形圖

3.5 不同缺陷類型局放信號采集

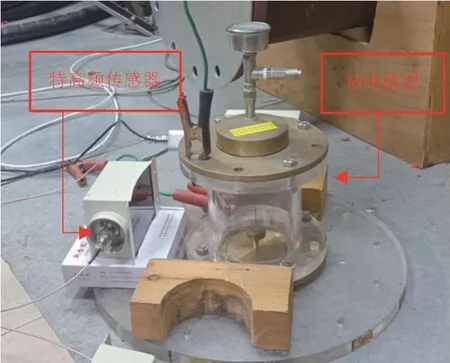

不同缺陷類型的局部放電信號產生平臺如圖16所示。實驗中,通過圖16中的放電模型產生金屬尖端放電、懸浮放電、自由金屬顆粒放電三種放電類型。通過FPGA采集到的采樣率提升前后的波形對比如圖17~圖19所示。

圖16 局部放電產生平臺

圖17 尖端放電采樣率提升前后波形圖

圖18 懸浮放電采樣率提升前后波形圖

圖19 自由金屬顆粒放電采樣率提升前后波形圖

由上述三種不同放電類型的采樣率提升前后的波形圖對比可知,采樣率的提升更好的保留了原始局放的脈沖波形特征。并且對比三種不同缺陷局部放電信號的波形圖可以看出,由該系統采集到的局部放電波形能夠反映不同的缺陷類型。

4 結論

本文為實現最大程度的保留特高頻傳感器接收的局部放電信號時域波形特征,設計了一種基于TIADC技術特高頻局部放電信號并行采集系統。針對TIADC技術引入的失配誤差,提出了基于LMS的自適應增益和偏置誤差校準算法,對于時延失配設計并實現了基于Farrow結構的分數延時濾波器進行校準。最后實驗結果表明,設計的并行采集能夠實現最高1 GHz的采樣率,并且針對TIADC引入的通道失配誤差也得到了有效校準,有效抑制了雜散譜,在100 MHz帶寬范圍內無雜散動態范圍提升到了35 dB。