變電站便攜式保護裝置的設計與分析

王 丹

(黑龍江省能源研究所,哈爾濱 150001)

0 引 言

繼電保護裝置是電力系統穩定運行的關鍵設備之一,其工作狀態的好壞直接影響系統安全。我國電力事業正在飛速發展,并計劃于2016年至2020年建成統一的“堅強智能電網”,“堅強智能電網”以堅強網架為基礎,以通信信息平臺為支撐,以智能控制為手段,覆蓋所有電壓等級,包括電力系統的發電、輸電、變電、配電、用電和調度各個環節。而電力系統的可靠性又是發展“堅強智能電網”的前提[1-3]。目前我國變電站主要由常規變電站和數字化變電站組成,其中110 kV以下采取單套配置的保護系統,一旦保護裝置發生故障后,需要停電進行檢修,影響了供電的持續性,其中220 kV以上采用雙套配置的保護系統,但是其中一套故障后,則降為單套配置的保護系統,大大影響了系統的可靠性。研制能夠通過簡單安裝并能夠快速投入保護狀態的便攜性保護裝置,既可以提高變電環境的可靠性,又能保證供電的持續性是非常重要的。

1 系統組成

1.1 工作原理

選用型號為EP4CE6E22C8D的FPGA芯片作為硬件電路的主芯片,該芯片是由Altera公司制造的Cyclone Ⅳ系列產品,是整個裝置的核心,完成對信號采集的處理、微機保護算法的實現、人機交互部分的控制,以及輸出控制信號等,通過硬件描述語言在芯片上完成邏輯控制輸出、參數讀寫、算法實現、保護等功能[4-6]。

1.2 硬件電路

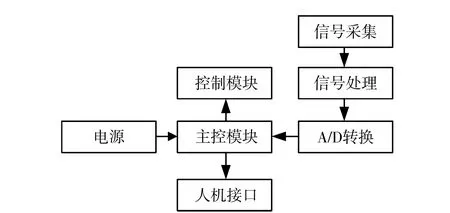

設計裝置的結構圖如圖1所示。該裝置采用模塊化思想,將硬件電路分為:數據采集處理模塊、控制模塊、人機交互模塊、輸出模塊等。

圖1 硬件裝置結構

在常規繼電保護的基礎上,數據模塊采用ISO122芯片進行信號隔離,降低了系統干擾,選用鉗式互感器采集后送入信號處理模塊,信號處理模塊將采集的模擬信號整形放大送到轉換芯片AD7656,將轉換的數字信號送入FPGA;控制模塊為根據FPGA輸出的控制信號執行控制動作。

1.3 軟件程序流程

采用VHDL語言對電路進行描述,VHDL語言的數據類型豐富,靈活性高的特點可以簡化開發難度。應用模塊化思想對硬件進行逐個描述,然后用頂層文件用頂層文件對各部分模塊進行協調和控制,以保護模塊程序框架為例,如圖2所示。

圖2 保護模塊程序流程

1.4 算法的選擇

便攜式保護裝置通過對送入系統的數據進行分析來判斷保護動作,所以,算法的速度和精度也影響著系統的性能。

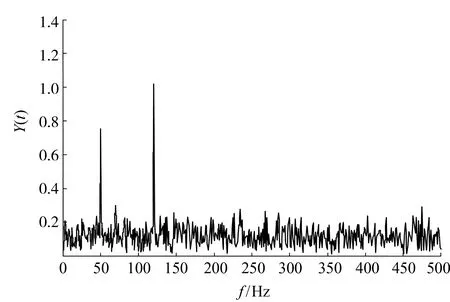

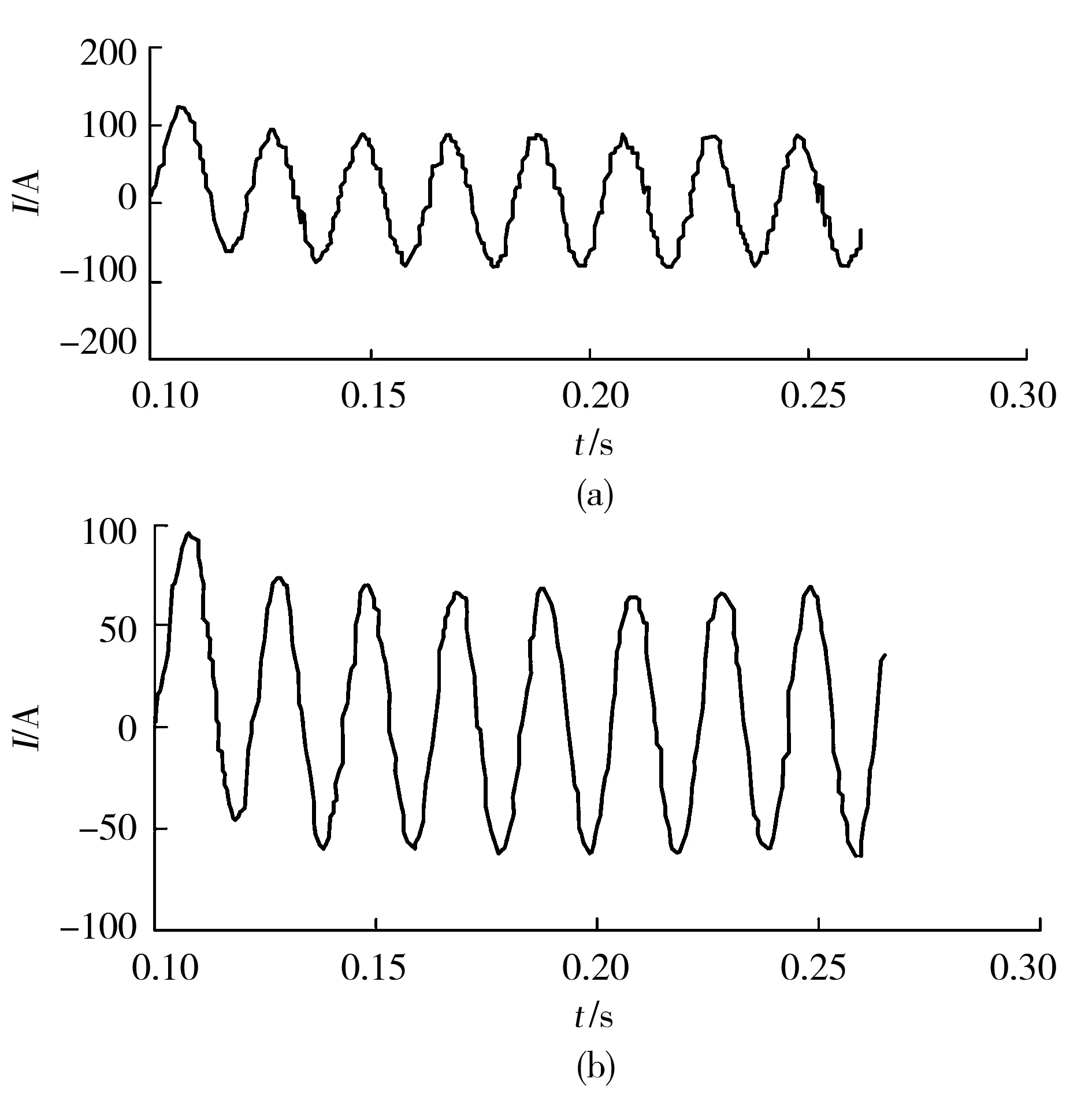

實際差動電流并不是標準正弦波,含有直流分量、高次諧波,當設采樣頻率f為1 200 Hz,采樣點數為24點,對變壓器內部發生的AB相短路進行仿真,對輸出電流的差動電流進行分析可以觀察到在變壓器內兩相短路故障時,差動電流中基波分量最多,其次是直流分量和高次諧波。如圖3所示。

圖3 差動電流波形分析

在數字信號處理時候,為得到精準的得到基波分量,可以利用傅里葉級數:

(1)

式中,n=0,1,2,…;an為各次諧波分量的余弦分量的幅值;bn為各次諧波分量的正弦分量的幅值。

可求出an、bn分別為:

(2)

代入式(1)可得到基波分量表達式為:

x1(t)=b1sinω1t+a1cosω1t

(3)

合并正弦、余弦:

(4)

可求出周期函數的有效值和相角:

2X2=a12+b12

(5)

(6)

經過采樣、模數變換后常得到離散的值,所以將傅里葉離散化處理,表述為:

(7)

(8)

式中,N為每個周期內對基波采樣的采樣次數;i(k)為k時刻信號的采樣值。

為了降低非周期分量的影響,可將一次差分濾波加在傅里葉算法之前。經過反復驗證,比較各類算法,本裝置采用差分濾波的全波傅里葉算法,該算法具有良好的濾波效果,也適用于便攜式保護裝置。

2 仿真與應用

2.1 控制系統仿真

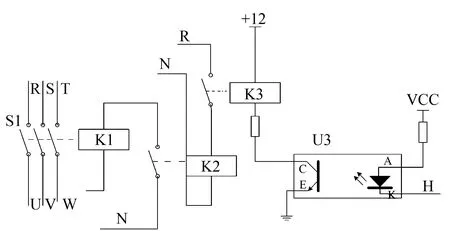

控制部分原理圖如圖4所示,FPGA主控模塊發出控制信號H,通過光耦U3驅動繼電器K3,與中間接觸器K2,K2合閘后對保護繼電器K1進行控制。

圖4 控制部分原理

通過MATLAB,對所設計的控制方案進行仿真驗證。以電流差動保護原理,對單相接地故障進行仿真,設置A相為故障相得到線路左右兩側三相電流波形圖,如圖5所示。

圖5 線路兩側三相電流

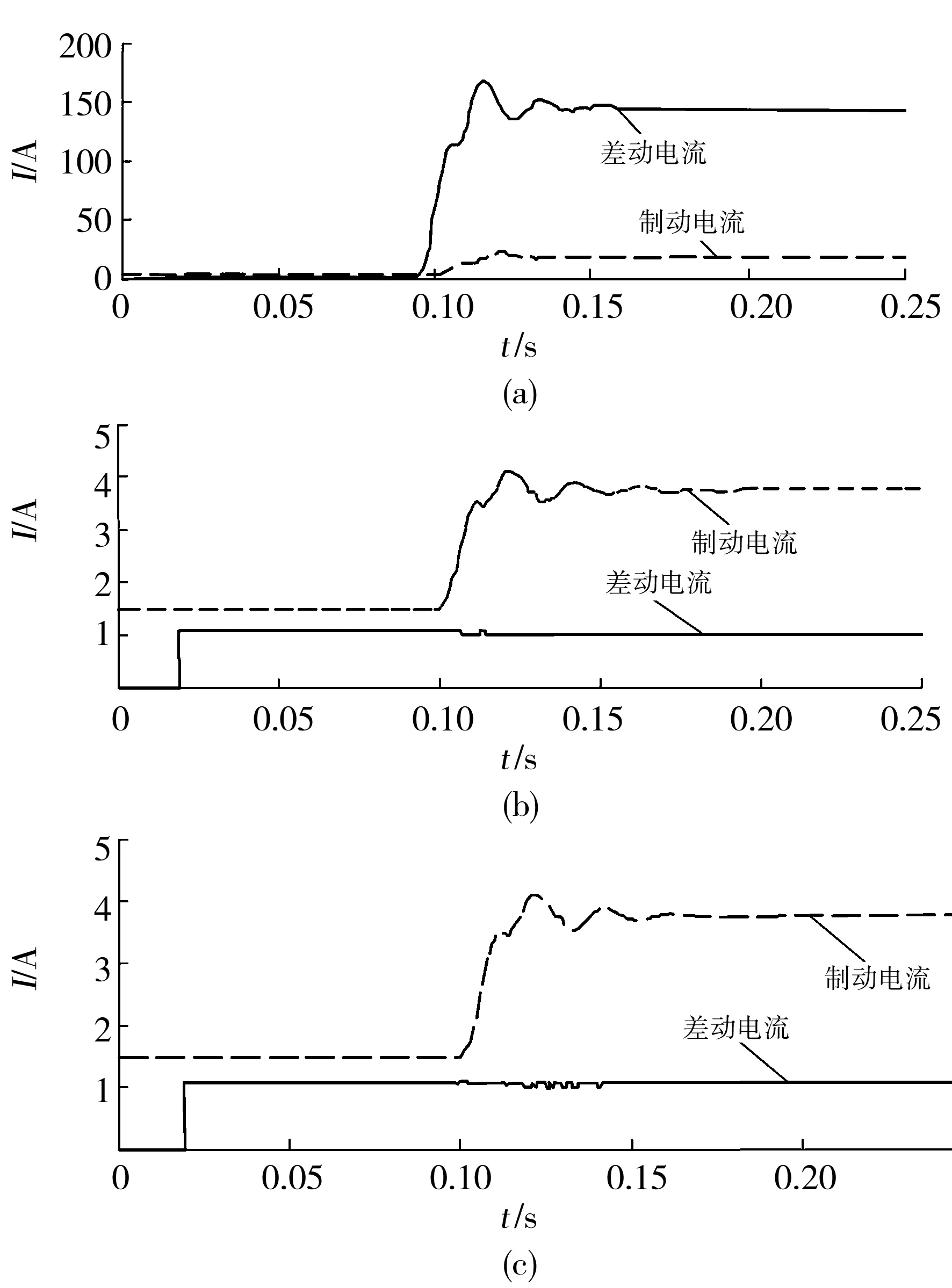

由圖5可見,經過傅氏算法采樣對三相電流進行濾波處理后得到的曲線接近正弦波,得到較好的濾波效果。仿真得到三相電流差動電流和制動電流圖,如圖6所示。

圖6 三相電流差動電流及制動電流

由圖6可知,在0.1 s時線路發生A相故障差動電流值高于制動電流值,輸出動作信號,非故障相制動電流高于差動電流,保護不動作。

2.2 實例分析

為減少故障及事故引起的經濟損失,提高電力系統變電站的運行的可靠性,要定期對一次設備和二次設備進行停電維護,檢修線路和變壓器內部故障時,也影響了供電的持續性[3]。在變電站檢修期間,接入便攜式裝置可以提供臨時性的保護,來保證電力系統的安全可靠運行。

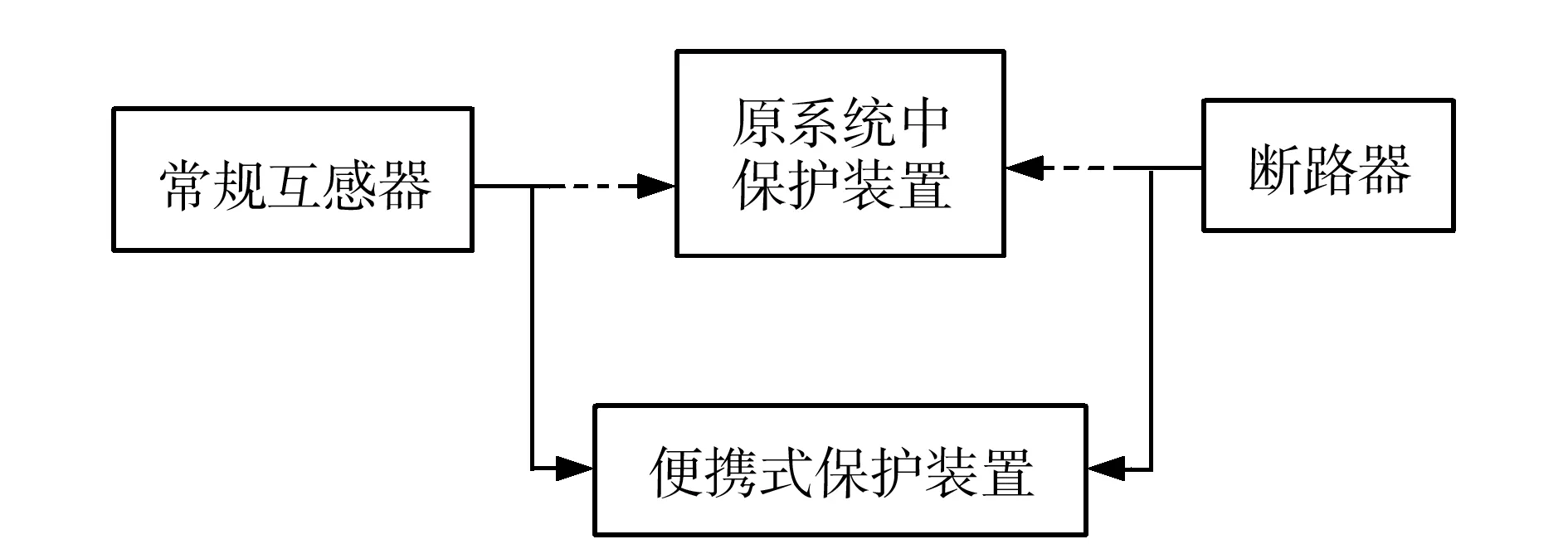

以常規變電站為例,如圖7所示,讓裝置暫時性接替原有保護裝置的保護工作,從而降低越級跳閘的風險性,保證系統安全。

圖7 常規變電站保護替換方式

3 結束語

變電站便攜式保護克服了常規變電站與智能變電站在故障檢修時無法保證系統可靠性與供電持續性問題,與傳統微機繼電保護裝置不同,采用FPGA做為核心主控芯片,實現差分濾波的傅里葉算法,對各個模塊協調控制,并將裝置設計為箱式結構,便于攜帶,設計進一步工作為在軟件方面,繼續進行大量動態模擬仿真試驗,數字仿真實驗,驗證了裝置的靈敏度以及提高裝置的抗干擾能力。